一种功率半导体器件、封装结构及电子设备

文献发布时间:2023-06-19 12:13:22

技术领域

本申请涉及电子设备技术领域,尤其涉及到一种功率半导体器件、封装结构及电子设备。

背景技术

在电力系统、数据中心、电动汽车、新能源应用等多个领域,利用电力电子设备来实现能量转换是常用的手段,功率半导体器件作为电力电子变换器的基本组成单元,在其中起着至关重要的作用。半导体器件通常包括半导体衬底层、金属电极层、钝化层、塑封层等多层结构,各层结构的固有热特性不一致,在温度循环及温度冲击等可靠性考核过程中,各层结构间就会由于热膨胀系数(coefficient of thermal expansion,CTE)不匹配而产生剪切应力,当超过一定的循环次数时,该应力甚至会超过金属材料的屈服强度,致使金属电极层发生形变,此时剪切应力几乎完全由刚性的钝化层承担,这样就会导致钝化层内部产生裂纹,若裂纹发生进一步扩展,则有可能会引发半导体器件失效。

发明内容

本申请提供了一种功率半导体器件、封装结构及电子设备,用以减小功率半导体器件失效的风险。

第一方面,本申请提供了一种半导体器件,该半导体器件包括半导体衬底、外延层、第一金属层、第二金属层以及钝化层。其中,半导体衬底中掺杂有第一类型杂质;外延层设置在半导体衬底的一面,外延层中也可掺杂有第一类型杂质,另外,外延层背离半导体衬底的第一面还可设置有掺杂第二类型杂质的第一掺杂区,且外延层的第一面的周侧边缘具有划片道区;第一金属层设置在外延层背离半导体衬底的一侧,第一金属层与外延层电性连接;第二金属层设置在外延层背离半导体衬底的一侧,另外,从半导体器件的边缘指向中心的方向,第二金属层可位于划片道区与第一金属层的边缘之间;钝化层可以设置在第一金属层背离半导体衬底的一侧,钝化层可以为环形结构,钝化层可覆盖第二金属层及第一金属层的边缘,用于抵挡外界杂质与潮气的入侵,以提高功率半导体器件的性能稳定性与可靠性。

上述方案中,第二金属层相对第一金属层更靠近功率半导体器件的边缘,从而使钝化层在功率半导体器件的边缘的第二金属层处形成台阶结构,在温度循环及温度冲击等可靠性考核中,钝化层上的应力集聚点可以转移至其在第二金属层处形成的台阶结构处,即使钝化层在该台阶结构处产生裂纹,也不至于影响功率半导体器件的电性功能区,从而可以减小功率半导体器件电性失效的风险。

具体设置时,功率半导体器件为肖特基二极管或者功率金属氧化物半导体场效应晶体管。

在一些可能的实施方案中,第二金属层可以包括多组金属结构,多组金属在环形区域内可以两两间隔设置。这样,沿周向方向,钝化层的边缘可以形成多处台阶结构,从而使钝化层上的应力集聚点可以有效地向钝化层的边缘转移。

在一些可能的实施方案中,外延层在垂直于功率半导体器件的厚度方向的截面可以为矩形。此时,环形区域也可以为与外延层的形状相匹配的矩形环,且环形区域的四个角部分别与外延层的四个角部相对设置。金属结构的数量可以为四组,四组金属结构可分别设置在环形区域的四个角部,从而在钝化层的四个角部分别形成台阶结构,进而将钝化层上的应力集聚点向边缘的四个角部转移。

具体设置时,每组金属结构可以包括至少一个金属块,至少一个金属块可以沿从功率器件的边缘到中心的方向排布,这样可以在钝化层的边缘由内到外形成至少一道台阶结构,有利于使钝化层的应力集聚点更加有效地转移至钝化层的边缘。

示例性地,每组金属结构中金属块的数量可以为一个、两个或者三个等等,相应地可以在钝化层的边缘形成一道台阶结构、两道台阶结构或者三道台阶结构。

在一个具体的实施方案中,金属块可以包括相互连接的第一部分和第二部分,第一部分与第二部分呈一定的夹角设置。具体设置时,第一部分与第二部分之间的夹角可以在0~180°之间。

示例性地,第一部分与第二部分可以相互垂直,这时,第一部分与第二部分分别沿外延层的第一面相邻的两条侧边设置。这种设置方式可以提高钝化层在该金属块位置的应力集聚程度,从而减小对功率半导体器件的电性功能区的影响。

另外,在实际应用中,第一部分与第二部分形成的夹角可以朝向功率半导体器件的边缘设置,也可以背向功率半导体器件的边缘设置,本申请对此不作限制,这两种设置方式均可以提高钝化层在金属块位置的应力集聚程度。

在一个具体的实施方案中,金属块在垂直于功率半导体器件的厚度方向的截面可以为阶梯形。金属块可以包括台阶面以及连接在相邻的两个台阶面之间的连接面,其中,台阶面与连接面可以分别沿外延层的第一面相邻的两条边设置。这种设置方式也可以提高钝化层在金属块位置的应力集聚程度。

具体设置时,金属块的阶梯形式可以具有不同的爬升趋势,例如可以由右下至左上的趋势爬升,也可以由左下至右上的趋势爬升,本申请对此不作限制,这两种设置方式均可以提高钝化层在金属块位置的应力集聚程度。

在一个具体的实施方案中,金属块在垂直于功率半导体器件的厚度方向的截面还可以为弧形。具体设置时,金属块可以朝向功率半导体器件的边缘凸出,弧形的圆心角可以在0~90°之间,示例性地,当弧形的圆心角为90°时,该弧形两侧端点的切线可以分别沿外延层的第一面相邻的两条边设置。这种设置方式也可以提高钝化层在金属块位置的应力集聚程度。

在一些可能的实施方案中,功率半导体器件还可以包括场氧化层,场氧化层可以为环形结构,场氧化层的外侧与划片道区间隔设置,场氧化层的内侧位于第一金属层的边缘与外延层之间,第二金属层则设置在场氧化层与钝化层之间。场氧化层可以保护功率半导体器件的终端区表面,减小外部电荷对终端区的影响,从而提高功率半导体器件的工作可靠性。

在一些可能的实施方案中,场氧化层上可以开设有通孔,第二金属层可以通过通孔与外延层电性连接,以使第二金属层与外延层保持等电位,进而提高功率半导体器件的性能可靠性。

另外,外延层的第一面对应通孔的位置还可以设置有掺杂有第一类型杂质的第二掺杂区,第二金属层具体可以通过通孔与第二掺杂区电性连接。

具体设置时,第二掺杂区内第一类型杂质的掺杂浓度可以大于外延层中第一类型杂质的掺杂浓度,从而更加有效地使第二金属层与外延层保持等电位。

在一些可能的实施方案中,钝化层可以包括至少一个层结构,层结构的材质可以为电介质材料。示例性地,层结构的材质具体可以为二氧化硅、氮化硅或者半绝缘多晶硅中的一种。

在一些可能的实施方案中,功率半导体器件还可以包括保护层,保护层也可以为环形结构,保护层可以覆盖钝化层以及部分第一金属层。保护层可用于缓冲后续封装制程中塑封料对器件表面的挤压,并且可以阻挡塑封料中颗粒物向器件内部扩散,从而提高功率半导体器件的性能稳定性与可靠性。示例性地,保护层的材质可以为聚酰亚胺或者对苯撑苯并二恶唑纤维等。

第二方面,本申请还提供了一种封装结构,该封装结构包括基板、引线以及前述任一可能的实施方案中的功率半导体器件,其中,功率半导体器件设置在基板的一面,引线设置在基板上与功率半导体器件同侧的一面,且引线围绕功率半导体器件设置,引线的第一端与功率半导体器件电性连接。在温度循环及温度冲击等可靠性考核中,功率半导体器件的应力集聚点可以转移至边角区域,即使产生裂纹,也不至于影响功率半导体器件的电性功能区,从而可以消减功率半导体器件电性失效的风险,进而可以提高封装结构的可靠性。

第三方面,本申请还提供了一种电子设备,该电子设备可以包括电路板以及前述实施方案中的封装结构,封装结构可以通过焊接等方式固定于电路板上,电路板上避开封装结构的区域还可以设置信号管脚,信号管脚可以与引线的第二端连接,以使封装结构能够通过电路板上的走线与其它器件相连接,进而实现功率半导体器件与外部电路的连接。由于功率半导体器件电性失效的风险较低,因此该电子设备的性能稳定性得以提升。

附图说明

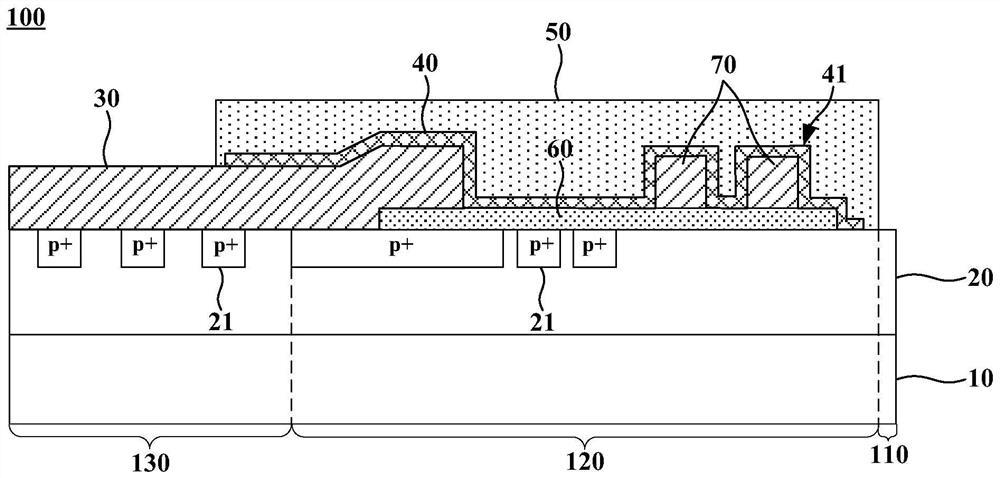

图1为一种功率半导体器件的截面结构示意图;

图2为本申请实施例提供的一种功率半导体器件的局部平面结构示意图;

图3为图2中所示的功率半导体器件在A-A处的截面结构示意图;

图4为本申请实施例提供的另一种功率半导体器件的局部平面结构示意图;

图5为图4中的功率半导体器件在B-B处的截面结构示意图;

图6为本申请实施例提供的又一种功率半导体器件的局部平面结构示意图;

图7为本申请实施例提供的又一种功率半导体器件的局部平面结构示意图;

图8为本申请实施例提供的又一种功率半导体器件的局部平面结构示意图;

图9为本申请实施例提供的又一种功率半导体器件的局部截面结构示意图;

图10为本申请实施例提供的封装结构的结构示意图。

附图标记:

100-功率半导体器件;10-半导体衬底;20-外延层;30-第一金属层;40-钝化层;

50-保护层;110-划片道区;120-终端区;130-有源区;21-第一掺杂区;60-场氧化层;

70-第二金属层;71-金属结构;711-金属块;7111-第一部分;7112-第二部分;

7113-台阶面;7114-阶梯面;80-绝缘层;81-栅极;61-多晶硅材料;62-栅极信号走线;

63-通孔;200-基板;300-引线框架。

具体实施方式

为了使本申请的目的、技术方案和优点更加清楚,下面将结合附图对本申请作进一步地详细描述。

在电力系统、数据中心、电动汽车、新能源应用等多个领域,利用电力电子设备来实现能量转换是常用的手段,功率半导体器件作为电力电子变换器的基本组成单元,在其中起着至关重要的作用。

碳化硅(SiC)属于第三代宽禁带半导体材料,相比于传统的硅材料,碳化硅具有高临界击穿场强、高热导率、高本征工作温度等优异特性,由其制备的肖特基二极管(schottky barrier diode,SBD)、功率金属氧化物半导体场效应晶体管(metal-oxide-semiconductor field-effect transistor,MOSFET)等功率器件具有工作结温高、开关损耗低等优点,有利于电力电子系统的高频化及轻量化,在功率因数校正(power factorcorrection,PFC)整流器、光伏逆变器、车载电驱动系统等领域广泛应用。

肖特基二极管利用金属与半导体接触形成的金属-半导体结原理制作而成,因此,肖特基二极管也称为金属-半导体二极管或表面势垒二极管。肖特基二极管的反向恢复时间短、正向导通压降低,因此多用作高频、低压等场景。下面首先以功率半导体器件为肖特基二极管为例进行说明。

图1为一种功率半导体器件的截面结构示意图。参考图1所示,该功率半导体器件100可以包括依次层叠的半导体衬底10、外延层20、第一金属层30、钝化层40以及保护层50。另外,按照功能区域划分,从边缘指向中心的方向,该功率半导体器件还可以依次包括划片道区110、终端区120以及有源区130,其中,有源区130内设置有多个基本功能元胞,以保证半导体器件功能的正常实现;终端区120可保证半导体器的击穿电压,以提高半导体器件的工作可靠性;划片道区110则可为后续的切割作业进行导引,在各层结构制作完成后,可以利用切割工具沿划片道区将晶片切割为多个独立的功率半导体器件100。

具体实施时,半导体衬底10具体可以为碳化硅衬底,半导体衬底10中可掺杂有第一类型杂质。第一类型杂质可以为N型杂质或者P型杂质,可以理解的,若第一类型杂质为N型杂质,则所形成的半导体衬底10即为N型半导体衬底;若第一类型杂质为P型杂质,则所形成的半导体衬底10即为P型半导体衬底。以下实施例以第一类型杂质为N型杂质进行说明。

外延层20设置在半导体衬底10的一面,外延层20中也可掺杂有第一类型杂质。具体实施时,外延层20中第一类型杂质的掺杂浓度与半导体衬底10中第一类型杂质的掺杂浓度可以不同,例如外延层20中第一类型杂质的掺杂浓度可以小于半导体衬底10中第一类型杂质的掺杂浓度。通过调节外延层20中第一类型杂质的掺杂浓度,可以实现对功率半导体器件的性能参数的控制。例如,当增大外延层20中第一类型杂质的掺杂浓度,半导体器件的击穿电压和特征导通电阻均可变小;当增大外延层20中第一类型杂质的掺杂浓度,半导体器件的击穿电压和特征导通电阻均有所增大。

另外,半导体器件的击穿电压和特征导通电阻也受外延层20的厚度的影响,例如,随着外延层20厚度的增大,半导体器件的击穿电压和特征导通电阻均可变大;随着外延层20厚度的减小,半导体器件的击穿电压和特征导通电阻均可变小。因此,在实际应用中,可以根据应用场景的需求对外延层20的厚度以及其中第一类型杂质的掺杂浓度进行设计,以获得合适的性能参数。

请继续参考图1,外延层20具有背离半导体衬底10设置的第一面,在外延层20的第一面设置有多个第一掺杂区21,该第一掺杂区21内掺杂有第二类型杂质。应当理解的是,当第一类型杂质为N型杂质时,第二类型杂质则为P型杂质,此时第一掺杂区也即P型掺杂区。需要说明的是,有源区130和终端区120可分别设置第一掺杂区21,其中,有源区130内的第一掺杂区21可以为条形结构,有源区130内的多个第一掺杂区21可以呈阵列排布,用于形成功率半导体器件100的基本功能元胞;终端区120内的第一掺杂区21则可以为环形结构,终端区120内的多个第一掺杂区21可以呈辐射状排布,用于使电场横向扩展,以保证有源区130PN结的耐压效率。

第一金属层30设置在外延层20的第一面,具体设置时,第一金属层30可以覆盖有源区130,以保证与有源区130内的N型半导体的可靠接触。第一金属层30的材质不限,例如可以为钛、钨、钼、金、银、铝、镍等。在本实施例中,第一金属层30可作为功率半导体器件100的正极,N型半导体(半导体衬底10及外延层20)可作为功率半导体器件100的负极。第一金属层30与N型半导体接触后,由于两者功函数不同,N型半导体中的电子会由高能级发射至金属低能级中,表面电中性被破坏,形成耗尽层,建立起由N型半导体指向第一金属层30的电场,并使电子产生由第一金属层30向N型半导体的漂移运动。当电子发射与漂移运动达到相对平衡后,便形成稳定的肖特基势垒。当在肖特基结两端加上正向偏压,也即第一金属层30接电源正极,N型半导体衬底接电源负极时,肖特基势垒降低,电子发射增强,正向偏压足够高时,即形成正向电流;反之,当在肖特基结两端加上反向偏压,肖特基势垒增大,电子发射被抑制,形成反向阻断。

钝化层40可以设置在第一金属层30背离半导体衬底的一侧。具体设置时,钝化层40可以为环形结构,钝化层40的内侧可覆盖第一金属层30的边缘,钝化层40的外侧与划片道区110间隔设置。钝化层40可以抵挡外界杂质与潮气的入侵,从而提高功率半导体器件100的性能稳定性与可靠性。在一些实施例中,钝化层40可以为单层结构,这时钝化层40的材质可以为二氧化硅、氮化硅或者半绝缘多晶硅中的一种。在另外一些实施例中,钝化层40还可以为多层结构,各层结构的材质不同且均可以为二氧化硅、氮化硅或者半绝缘多晶硅中的一种。需要说明的是,本申请实施例所采用的“内”、“外”等方位用词主要依据功率半导体器件100的结构进行阐述,定义靠近功率半导体器件100边缘的一侧为外侧,远离功率半导体器件100边缘的一侧为内侧。

保护层50可以设置在钝化层40背离半导体衬底10的一侧。保护层50也可以为环形结构,保护层50的内侧可覆盖钝化层40以及部分第一金属层30,保护层50的外侧则可延伸至划片道区110。在本实施例中,保护层50的材质可以为聚酰亚胺(polyimide,PI)、聚苯并噁唑(polybenzoxazole,PBO)等,其可用于缓冲后续封装制程中塑封料对器件表面的挤压,另外还可以阻挡塑封料中颗粒物向器件内部扩散,从而提高功率半导体器件100的性能稳定性与可靠性。

可以理解的是,在一些实施例中,功率半导体器件100的终端区120内还可以设置场氧化层60,场氧化层60也可以为环形结构,且场氧化层60的内侧位于第一金属层30与外延层20之间,场氧化层60的外侧与划片道区110间隔设置。场氧化层60的材质可以为二氧化硅(SiO2)、磷硅玻璃(phosphosilicate glass,PSG)或者硼磷硅玻璃(boro-phospho-silicate glass,BPSG)等,场氧化层60可以保护终端区120表面,减小外部电荷对终端区120的影响,从而提高功率半导体器件100的工作可靠性。

在图1所示的实施例中的功率半导体器件中,由于各层结构的固有热特性不一致,在温度循环及温度冲击等可靠性考核过程中,半导体衬底10、钝化层40、保护层50等层结构间就会由于CTE值不匹配而产生剪切应力,当超过一定的循环次数时,该应力甚至会超过第一金属层30的金属材料的屈服强度,致使第一金属层30发生形变,此时剪切应力几乎完全由刚性的钝化层40承担,从而导致钝化层40内部产生裂纹。

此外,由于第一金属层30相对较厚,且整体尺寸较大,因此其形变也更为严重;而相比于传统的硅材料半导体衬底,碳化硅材料与钝化层40材料的CTE值差别更大,因此应力集中问题也更为严重,并且尤其容易集中在钝化层40在第一金属层30的边缘所形成的台阶区域S,导致该区域的钝化层40产生裂纹的风险进一步增加,若裂纹发生进一步扩展,就会影响器件的电性功能区,从而有可能引发功率半导体器件100失效。

图2为本申请实施例提供的一种功率半导体器件的局部平面结构示意图,图3为图2中所示的功率半导体器件在A-A处的截面结构示意图。一并参考图3和图4所示,针对上述问题,在本申请的一些实施例中,功率半导体器件100还可以包括第二金属层70,沿层叠方向,该第二金属层70设置于场氧化层60与钝化层40之间。另外,从功率半导体器件100的边缘指向中心的方向,该第二金属层70位于划片道区110与第一金属层30的边缘之间的环形区域内,因此第二金属层70相对第一金属层30更靠近功率半导体器件100的边缘,且第二金属层70在外延层20的第一面的投影位于终端区120内最边缘的第一掺杂区21的外侧,也即第二金属层70位于功率半导体器件100的电性功能区140外侧,从而使钝化层40在功率半导体器件100的边缘的第二金属层70处形成台阶结构41。经过实验以及仿真结果验证,在温度循环及温度冲击等可靠性考核中,钝化层40上的应力集聚点更容易集中在其靠近功率半导体器件100边缘的台阶结构41处,因此通过设置第二金属层70,就可以将可靠性考核过程中的应力集聚点转移至半导体器件的边缘区域,即使钝化层40在该区域的台阶结构41处产生裂纹,也不至于影响半导体器件的电性功能区,从而可以消减半导体器件电性失效的风险。

其中,第二金属层70的材质与第一金属层30可以相同,如可以为钛、钨、钼、金、银、铝、镍等,这样可以使得第二金属层70与第一金属层30的来料实现归一化,从而有利于降低功率半导体器件100的制作成本。

具体实施时,第二金属层70可以包括多组金属结构71,多组金属结构71可以间隔分布在第一金属层30的边缘与划片道区110之间的环形区域内,因此沿周向方向,钝化层40的边缘可以形成多处台阶结构41,从而使钝化层40上的应力集聚点可以有效地向钝化层40的边缘转移。

例如,在一些实施例中,外延层20及半导体衬底10在垂直于功率半导体器件100的厚度的方向的截面可以为矩形,这时,划片道区110与第一金属层30的边缘之间的环形区域也大致为矩形环,且该环形区域的四个角部分别与外延层20的四个角部相对设置,第二金属层70可以包括四组金属结构,四组金属结构71可以分别位于环形区域的四个角部,从而在钝化层40的四个角部分别形成台阶结构41,进而将钝化层40上的应力集聚点转移至其四个角部。

图4为本申请实施例提供的另一种功率半导体器件的局部平面结构示意图,图5为图4中的功率半导体器件在B-B处的截面结构示意图。一并参考图4和图5所示,在本申请实施例中,每组金属结构71可以包括至少一个金属块711,示例性地,每组金属结构71中金属块711的数量可以为一个、两个或者三个,等等,图5中以每组金属结构71包括两个金属块711为例进行说明,这时,两个金属块711可以沿从功率半导体器件100的边缘到中心的方向排布,从而在钝化层40的边缘形成内外两道台阶结构41,这样有利于使钝化层40的应力集聚点更加有效地转移至钝化层40的边缘。

继续参考图4和图5,金属块711可以包括相互连接的第一部分7111和第二部分7112,第一部分7111与第二部分7112呈一定的夹角设置。具体实施时,第一部分7111与第二部分7112之间的夹角可以在0~180°之间,本申请对此不作具体限制。示例性地,第一部分7111与第二部分7112可以相互垂直,也即,金属块711的截面形状为L形。金属块711靠近外延层20的角部设置,当外延层20的截面形状为矩形时,第一部分7111与第二部分7112可分别沿外延层20的第一面相邻的两条边设置,这种设置方式有利于提高钝化层40在该金属结构处的应力集聚程度,从而减小对功率半导体器件100的电性功能区的影响。

另外,本申请实施例中,第一部分7111与第二部分7112形成的夹角可以如图4中所示的背向功率半导体器件100的边缘设置,或者也可以朝向功率半导体器件100的边缘设置,本申请对此不作限制,这两种设置方式均可以提高钝化层40在金属结构71处的应力集聚程度。可以理解的,在每组金属结构71中,各个金属块711的设置方向可以保持一致,这样有利于减小金属结构71的占用空间,进而减小对功率半导体器件100的整体结构尺寸的影响。

图6为本申请实施例提供的又一种功率半导体器件的局部平面结构示意图,图6中所示的功率半导体器件在C-C处的截面结构示意图也可以参考图5。一并参考图5和图6所示,在该实施例中,金属块711在垂直于功率半导体器件100的厚度方向的截面可以为阶梯形。具体设置时,金属块711可以包括台阶面7113以及连接于相邻的两个台阶面7113之间的连接面7114,可以理解的,台阶面7113与阶梯面7114均垂直于外延层20的第一面。金属块711靠近外延层20的角部设置,当外延层20的截面形状为矩形时,金属块711的台阶面7113和连接面7114分别沿外延层20的第一面相邻的两条边设置。类似地,这种设置方式也可以提高钝化层40在金属结构71处的应力集聚程度,从而减小对功率半导体器件100的电性功能区140的影响。

另外,上述实施例中,金属块711的阶梯形式可以如图6中所示的由右下至左上的趋势爬升,也可以如图7中所示的由左下至右上的趋势爬升,本申请对此不作限制,这两种设置方式均可以提高钝化层40在金属结构71处的应力集聚程度。类似地,在每组金属结构71中,各个金属块711的爬升趋势可以保持一致,这样有利于减小金属结构的占用空间,进而减小对功率半导体器件100的整体结构尺寸的影响。需要说明的是,本申请实施例所采用的“上”、“下”、“左”、“右”等方位用词主要依据图6和图7中的展示方位进行描述,并不形成对功率半导体器件100于实际应用场景中的方位的限定。

图8为本申请实施例提供的又一种功率半导体器件的局部平面结构示意图,图8中所示的功率半导体器件在D-D处的截面结构示意图也可以参考图5。一并参考图5和图8所示,在该实施例中,金属块711在垂直于功率半导体器件100的厚度方向的截面还可以为弧形。具体设置时,金属块711可以朝向功率半导体器件100的边缘凸出,弧形的圆心角可以在0~90°之间,示例性地,当弧形的圆心角为90°时,该弧形两侧端点的切线可以分别沿外延层20的第一面相邻的两条边设置。与前述实施例类似,这种设置方式也可以提高钝化层40在金属结构71处的应力集聚程度,从而减小对功率半导体器件100的电性功能区的影响。

以上实施例列举了几种不同结构形式的金属块及其设置方式,应当理解的是,本申请实施例中的金属块并不限于上述几种结构,对于采用其它形式的、具有相似结构特点的金属块同样可应用于本申请实施例中,只要能够达到集聚应力的效果即可,此处不再一一列举。

请再次参考图3所示,本申请实施例还提供了一种功率半导体器件100的制备方法,包括以下步骤:

步骤一、在半导体衬底10上形成外延层20;其中,半导体衬底10与外延层20具体可以为碳化硅材质,且半导体衬底10与外延层20中均掺杂有第一类型杂质,外延层20中第一类型杂质的掺杂浓度与半导体衬底10中第一类型杂质的掺杂浓度可以不同,例如外延层20中第一类型杂质的掺杂浓度可以小于半导体衬底10中第一类型杂质的掺杂浓度。

步骤二、在外延层20背离半导体衬底10的第一面形成若干第一掺杂区21,第一掺杂区21内掺杂有第二类型杂质。其中,有源区130内的第一掺杂区21可以为块状结构,有源区130内的多个第一掺杂区21可以呈阵列排布;位于终端区120内的第一掺杂区21可以为环形结构,终端区120内的多个第一掺杂区21可以呈辐射状排布。

步骤三、在外延层20的第一面形成环形的场氧化层60,场氧化层60的外侧与划片道区110间隔设置,场氧化层60的内侧靠近有源区130的边缘设置;场氧化层60可以保护终端区120表面,减小外部电荷对终端区120的影响,从而提高功率半导体器件100的工作可靠性。

步骤四、外延层20背离半导体衬底10的一侧形成第一金属层30和第二金属层70,其中,第一金属层30设置在外延层20的第一面,且第一金属层30可以覆盖场氧化层60的内侧边缘;第二金属层70设置在场氧化层60背离外延层20的一面,且第二金属层70在外延层20的第一面的投影位于终端区120内最边缘的第一掺杂区21的外侧,也即第二金属层70位于功率半导体器件100的电性功能区外侧。

步骤五、在第一金属层30及第二金属层70背离外延层20的一侧形成环形的钝化层40,钝化层40可覆盖第二金属层70及第一金属层30的边缘,且钝化层40的外侧与划片道区110间隔设置。钝化层40可以抵挡外界杂质与潮气的入侵,从而提高功率半导体器件100的性能稳定性与可靠性。另外,钝化层40在第二金属层70处可形成台阶结构41,在温度循环及温度冲击等可靠性考核过程中,可以使钝化层40上的应力集聚点转移至其靠近功率半导体器件100边角的台阶结构41处,由于第二金属层70远离功率半导体器件100的电性功能区,因此即使钝化层40在该区域的台阶结构41处产生裂纹,也不至于影响功率半导体器件100的电性功能区,从而可以消减器件电性失效的风险。

步骤六、在钝化层40背离半导体衬底10的一侧形成环形的保护层50,保护层50的内侧可覆盖钝化层40以及部分第一金属层30,保护层50的外侧则可延伸至划片道110区。保护层50可用于缓冲后续封装制程中塑封料对器件表面的挤压,另外还可以阻挡塑封料中颗粒物向器件内部扩散,从而提高功率半导体器件100的性能稳定性与可靠性。

值得一提的是,在本申请实施例中,第二金属层70与第一金属层30可以通过同一工序制作,具体实施时,可以在场氧化层60背离外延层20的一侧形成整层金属层,然后通过掩膜、刻蚀等工艺去除多余金属材料,从而形成第一金属层30和第二金属层70,因此本申请实施例可以在不增加额外的工艺步骤与制作成本的前提下,将应力集聚点转移至功率半导体器件100的边角处,消减器件电性失效的风险。

以上实施例是以功率半导体器件为肖特基二极管为例进行的说明,在本申请的其它一些实施例中,功率半导体器件还可以为功率MOSFET,下面以功率半导体器件为功率MOSFET为例进行说明。

图9为本申请实施例提供的又一种功率半导体器件的局部截面结构示意图。参考图9所示,该实施例中,功率半导体器件100也可以包括半导体衬底10、外延层20、场氧化层60、第一金属层30和第二金属层70、钝化层40以及保护层50。其中,半导体衬底10、外延层20、场氧化层60、第一金属层30和第二金属层70、钝化40层以及保护层50的相对位置关系可参阅上述实施例的设置方式,这里不再赘述。

在本申请实施例中,位于有源区120的第一掺杂区21内还设置有N型掺杂区和P型掺杂区,以第一掺杂区21内掺杂的第二类型杂质为P型杂质为例,第一掺杂区21内可并列设置有三个扩散区,分别为两个N型掺杂区和设置于两个N型掺杂区之间的P型掺杂区,其中,P型掺杂区中P型杂质的掺杂浓度大于第一掺杂区21内P型杂质的掺杂浓度。

外延层20的第一面还设置有绝缘层80,第一金属层30可穿过绝缘层80上的通孔与第一掺杂区21内的N型掺杂区和P型掺杂区电性连接。绝缘层80与场氧化层60的材质相同,例如二者均可以为二氧化硅材质。绝缘层80内设置有栅极81,栅极81可以为多晶硅材料。

本实施例中,第一金属层30即为该功率半导体器件100的源极,需要说明的是,以下实施例中,源极与第一金属层30的标号相同。半导体衬底10背离外延层20的一面还设置有漏极金属(图中未示出),栅极81可用于接收驱动源极30和漏极导通的控制信号。具体来说,在源极30、漏极之间加正电压时,栅极81、源极30之间的电压为零,第一掺杂区21与外延层20之间形成的PN结反偏,源极30与漏极之间无电流流过,功率半导体器件100处于截止状态;在栅极81、源极30之间加正电压时,栅极81的正电压会将其下方第一掺杂区21中的空穴推开,将第一掺杂区21内的电子吸引至栅极81下方第一掺杂区21的表面;当所施加的正电压大于开启电压时,栅极81下方第一掺杂区21表面的电子浓度将超过空穴浓度,使P型半导体反型为N型而成为反型层,该反型层形成N沟道而使PN结消失,源极30与漏极导通。

另外,在场氧化层60靠近第一金属层30的一侧,绝缘层80内还设置有与上述栅极81互连的多晶硅材料61,场氧化层60背离外延层20的一面还设置有栅极信号走线62,栅极信号走线62通过绝缘层80上开设的通孔与绝缘层80内部的多晶硅材料61连接,进而与有源区130内的栅极81连接,以将控制信号发送给栅极81。

与前述实施例类似,本实施例中,第二金属层70设置于场氧化层60与钝化层40之间,且第二金属层70在外延层20的第一面的投影位于终端区120内最边缘的第一掺杂区21的外侧,也即第二金属层70位于功率半导体器件100的电性功能区外侧,从而使钝化层40在功率半导体器件100的边缘的第二金属层70处形成台阶结构41。在温度循环及温度冲击等可靠性考核中,钝化层40上的应力集聚点可以转移至其在第二金属层70处形成的台阶结构41处,即使钝化层40在该台阶结构41处产生裂纹,也不至于影响功率半导体器件100的电性功能区,从而可以消减功率半导体器件100电性失效的风险。

其中,第二金属层70内的金属块形状也可以参考前述实施例的设置方式,例如金属块的截面形状可以为L形、阶梯形、弧形等等,此处不再进行赘述。

继续参考图9,在本申请实施例中,场氧化层60对应第二金属层70的位置还可以开设有通孔63,第二金属层70可以通过通孔63与外延层20电性连接,以使第二金属层70与外延层20保持等电位,进而提高功率半导体器件100的性能可靠性。外延层20的第一面对应通孔63的位置还可以设置有掺杂有第一类型杂质的第二掺杂区22,这时第二金属层70具体可以通过通孔63与第二掺杂区22电性连接。其中,第二掺杂区22内第一类型杂质的掺杂浓度可以大于外延层20中第一类型杂质的掺杂浓度,这样可以更加有效地保证第二金属层70与外延层20等电位。

参考图10所示,本申请实施例还提供了一种封装结构,该封装结构可以包括基板200、引线300以及前述任一可能的实施例中的功率半导体器件100,功率半导体器件100可以设置于基板200的其中一面,引线300设置于基板200上与功率半导体器件100同侧的一面,且引线300围绕功率半导体器件100设置,引线300的第一端与功率半导体器件100电性连接。在一些实施例中,功率半导体器件100具体可以为肖特基二极管或者功率MOSFET。在温度循环及温度冲击等可靠性考核中,功率半导体器件100的应力集聚点可以转移至边角区域,即使产生裂纹,也不至于影响功率半导体器件100的电性功能区,从而可以消减功率半导体器件100电性失效的风险,进而可以提高封装结构的可靠性。

本申请实施例还提供了一种电子设备,该电子设备可以为现有技术中的通讯设备、服务器、超级计算机或者路由器、交换机等设备。电子设备可以包括电路板以及前述实施例中的封装结构,封装结构可以通过焊接等方式固定于电路板上,电路板上避开半导体器件的区域则可以设置信号管脚,信号管脚可以与引线的第二端电性连接,以使封装结构能够通过电路板上的走线与其它器件相连接,进而实现功率半导体器件与外部电路的连接。由于功率半导体器件电性失效的风险较低,因此该电子设备的性能稳定性得以提升。

以上,仅为本申请的具体实施方式,但本申请的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本申请揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本申请的保护范围之内。因此,本申请的保护范围应以权利要求的保护范围为准。

- 一种功率半导体器件、封装结构及电子设备

- 一种轧机用功率半导体器件封装结构