一种主机和基板管理控制器之间的通信方法、装置、设备

文献发布时间:2023-06-19 12:13:22

技术领域

本申请涉及服务器技术领域,特别涉及一种主机和基板管理控制器之间的通信方法、装置、设备。

背景技术

在服务器上,Host(主机)与BMC(即Baseboard Management Controller,基板管理控制器)之间有大量交互,在服务器功能越来越强大,可管理性,可用性,稳定性,可服务性要求越来越高的趋势下,对Host与BMC之间的交互接口的要求也越来越高。IPMI(即Intelligent Platform Management Interface,智能平台管理接口)作为经典的服务器管理接口,应用广泛。在服务器上,Host和BMC通过IPMI接口有大量的交互。IPMI接口的性能,安全性直接影响服务器的可用性和安全性,进而影响数据中心和整个业务的可用性和安全性。

目前,现有技术中包括在Kcs(即keyboard controller style,键盘控制器类型/风格)接口上实现IPMI协议、在BT(即Block Transter,块传输接口)接口上实现IPMI协议、在Smbus(即System Management Bus,系统管理总线)接口上实现IPMI协议、在SMIC(即Server Management Interface Chip,服务器管理接口芯片)上实现IPMI协议、在USB(即Universal Serial Bus,通用串行总线)接口上实现IPMI等方案,但均有各种缺陷,主要包括传输速度慢、稳定性差、可用阶段晚等。

发明内容

有鉴于此,本申请的目的在于提供一种主机和基板管理控制器之间的通信方法、装置、设备,能够提升主机和基板管理控制器之间的通信效率,从而提升开机速度,并且稳定性好,可用阶段早。其具体方案如下:

第一方面,本申请公开了一种主机和基板管理控制器之间的通信方法,应用于基板管理控制器,包括:

从基板管理控制器的静态随机存取存储器中读取IPMI命令;其中,所述IPMI命令为主机BIOS下发至所述静态随机存取存储器的命令,并且,所述静态随机存取存储器在PEI阶段使能;

解析所述IPMI命令,得到所述IPMI命令的解析数据;

根据所述解析数据确定所述IPMI命令对应的返回数据;

将所述返回数据放置于所述静态随机存取存储器,以便所述主机BIOS从所述静态随机存取存储器中读取所述返回数据。

可选的,所述从基板管理控制器的静态随机存取存储器中读取IPMI命令,包括:

当发生预设中断,则从基板管理控制器的静态随机存取存储器中读取IPMI命令。

可选的,所述从基板管理控制器的静态随机存取存储器中读取IPMI命令,包括:

从基板管理控制器的静态随机存取存储器的动态区域中读取IPMI命令;

其中,所述动态区域为所述主机BIOS在所述静态随机存取存储器中划分的用于进行IPMI命令交互的存储区域;并且,所述静态随机存取存储器还包括由所述主机BIOS划分的静态区域,用于存放静态数据。

可选的,还包括:

在主机进入操作系统前,将所述静态随机存取存储器锁定。

可选的,还包括:

根据预设IPMI命令通信控制模式对主机操作系统下发的IPMI命令进行认证,若认证通过,则允许所述主机操作系统访问所述静态随机存取存储器。

可选的,所述预设IPMI命令通信控制模式为根据IPMI命令类型预设的模式,标准IPMI命令的预设IPMI命令通信控制模式为兼容模式,非标准IPMI命令的预设IPMI命令通信控制模式为保护模式;

相应的,所述根据预设IPMI命令通信控制模式对主机操作系统下发的IPMI命令进行认证,包括:

利用第一预设认证方式对主机操作系统下发的标准IPMI命令进行认证,以及利用第二预设认证方式对主机操作系统下发的非标准IPMI命令进行认证。

可选的,其特征在于,还包括:

当所述主机操作系统访问完所述静态随机存取存储器,则将所述静态随机存取存储器重新锁定。

第二方面,本申请公开了一种主机和基板管理控制器之间的通信装置,应用于基板管理控制器,包括:

IPMI命令获取模块,用于从基板管理控制器的静态随机存取存储器中读取IPMI命令;其中,所述IPMI命令为主机BIOS下发至所述静态随机存取存储器的命令,并且,所述静态随机存取存储器在PEI阶段使能;

IPMI命令解析模块,用于解析所述IPMI命令,得到所述IPMI命令的解析数据;

返回数据确定模块,用于根据所述解析数据确定所述IPMI命令对应的返回数据;

返回数据放置模块,用于将所述返回数据放置于所述静态随机存取存储器,以便所述主机BIOS从所述静态随机存取存储器中读取所述返回数据。

第三方面,本申请公开了一种电子设备,包括:

存储器,用于保存计算机程序;

处理器,用于执行所述计算机程序,以实现如权利要求1至7任一项所述的主机和基板管理控制器之间的通信方法。

第四方面,本申请公开了一种计算机可读存储介质,用于保存计算机程序,所述计算机程序被处理器执行时实现前述的主机和基板管理控制器之间的通信方法。

可见,本申请从基板管理控制器的静态随机存取存储器中读取IPMI命令;其中,所述IPMI命令为主机BIOS下发至所述静态随机存取存储器的命令,并且,所述静态随机存取存储器在PEI阶段使能;解析所述IPMI命令,得到所述IPMI命令的解析数据;根据所述解析数据确定所述IPMI命令对应的返回数据;将所述返回数据放置于所述静态随机存取存储器,以便所述主机BIOS从所述静态随机存取存储器中读取所述返回数据。也即,本申请中的主机与基板管理控制器之间的通信基于静态随机存取存储器实现IPMI协议,主机与基板管理控制器之间通过共享静态随机存取存储器进行IPMI通信,数据传输速度快,并且,静态随机存取存储器在PEI阶段使能,使静态随机存取存储器在开机早期便能够用于进行IPMI通信,这样,能够提升主机和基板管理控制器之间的通信效率,从而提升开机速度,并且稳定性好,可用阶段早。

附图说明

为了更清楚地说明本申请实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

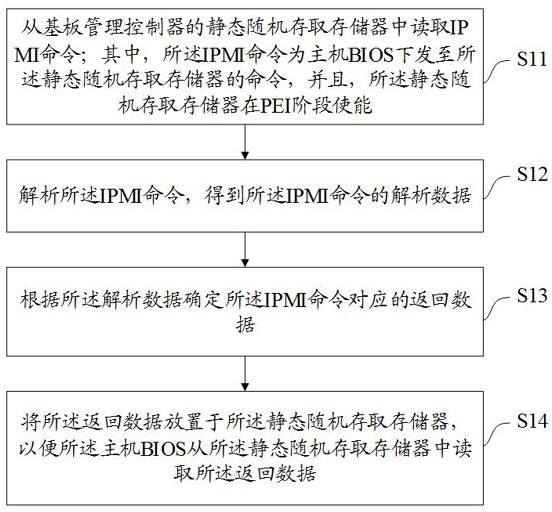

图1为本申请公开的一种主机和基板管理控制器之间的通信方法流程图;

图2为本申请公开的一种具体的主机和基板管理控制器之间的通信方法流程图;

图3为本申请公开的一种主机和基板管理控制器之间的通信方法流程图;

图4为本申请公开的一种具体的主机和基板管理控制器之间的通信方法流程图;

图5为本申请公开的一种主机和基板管理控制器之间的通信装置结构示意图;

图6为本申请公开的一种电子设备结构图。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

目前,现有技术中包括在Kcs接口上实现IPMI协议、在BT接口上实现IPMI协议、在Smbus接口上实现IPMI协议、在SMIC上实现IPMI协议、在Usb接口上实现IPMI等方案,但均有各种缺陷,但均有各种缺陷,主要包括传输速度慢、稳定性差、可用阶段晚等。为此,本申请提供了一种主机和基板管理控制器之间的通信方案,能够提升主机和基板管理控制器之间的通信效率,从而提升开机速度,并且稳定性好,可用阶段早。

参见图1所示,本申请实施例公开了一种主机和基板管理控制器之间的通信方法,应用于基板管理控制器,包括:

步骤S11:从基板管理控制器的静态随机存取存储器中读取IPMI命令;其中,所述IPMI命令为主机BIOS下(即Basic Input Output System,基本输入输出系统)发至所述静态随机存取存储器的命令,并且,所述静态随机存取存储器在PEI阶段使能。

在具体的实施方式中,从基板管理控制器的静态随机存取存储器的动态区域中读取IPMI命令;其中,所述动态区域为所述主机BIOS在所述静态随机存取存储器中划分的用于进行IPMI命令交互的存储区域;并且,所述静态随机存取存储器还包括由所述主机BIOS划分的静态区域,用于存放静态数据。

也即,主机BIOS将静态随机存取存储器分为动态区域和静态区域两个区域。

进一步的,本实施例中,当发生预设中断,则从基板管理控制器的静态随机存取存储器中读取IPMI命令。

需要指出的是,为保持通信的有效性,减少BMC的通信负担,本实施例选择使用中断方式实现,而不采用轮询方式。因为SRAM不支持中断,可选择GPIO(即General-purposeinput/output,通用型之输入输出)中断,不使用串口寄存器或者传统的KCS寄存器来实现中断机制。下IPMI命令前先填写BMC中的相应的寄存器,触发相应的预先指定的中断,BMC收到后,进行通信。中断机制的使能可以由BMC来实现。

其中,所述静态随机存取存储器被所述主机BIOS在PEI(Pre-EFIInitialization,用于调度PEIM(即PEI Modules,PEI阶段的程序块),DXE(即DriverExecution Environment,驱动执行环境)准备执行环境)阶段使能,也即,在启动阶段,在使能静态随机存取存储器之后便可以通过静态随机存取存储器进行主机和基板管理控制器之间的通信,可用阶段早,而现有方案,比如在USB接口上实现IPMI的方案,需要在USB驱动初始化完成后才能使用,可用阶段晚。

并且,在PEI阶段早期使能SRAM。可以实现一个PEIM,在PEI早期,使能SRAM。需要指出的是,在PEI阶段,PEI Dispatcher(PEIM 调度器)先按照优先级执行先验文件中列举的PEIM,然后根据PEIM之间的依赖条件执行依赖条件满足的PEIM。IPMI协议是一个基础服务,需要在PEI早期使能,为其他PEIM提供IPMI服务,为满足IPMI协议使用需求,需要在PEI阶段早期使能SRAM。具体的,实现一个用来初始化SRAM的PEIM,加入先验文件中,优先级设置为高于IPMI PEIM的优先级,从而使初始化SRAM的PEIM在PEI早期且在IPMI PEIM被执行前执行,使能SRAM,保证IPMI的协议使用需求。

在具体的实施方式中,在Boot(启动)阶段中,PEI阶段:主机BIOS初始化BMC的PCIE设备,分配BUS(总线)和MMIO(即Memory-mapped I/O,内存映射I/O)资源,使能SRAM访问,并将SRAM划分为两块区域,一块为静态区,一块为实现IPMI通信的动态区域。静态区域存放一些固定的静态数据,如Flag,文件等,增加Host与BMC交互的便捷性,适应性和高效性。动态区域用来实现IPMI通信,使用SRAM实现超大数据块传输,实现快速通信,之后安装IPMI PPI(即PEIM and PEIM Interface,PEI Module(PEI模块)和PEI Module(PEIM 模块)之间的接口),提供PEI阶段使用的IPMI Over SRAM Lib(即本申请方案的Library库)。DXE:提供DXE,SMM,Runtime等类型的Protcol(协议)供各种类型的模组(BIOS软件模块,包括DXE Driver(驱动)和SMM(即System Management Mode,系统管理模式) Driver)使用,提供DXE,SMM,Runtime(运行时)等类型的Lib供各种类型的模组(BIOS软件模块,包括DXE Driver和SMMDriver)使用。并且,BMC在主机BIOS使能SRAM访问后,使能中断机制。

步骤S12:解析所述IPMI命令,得到所述IPMI命令的解析数据。

步骤S13:根据所述解析数据确定所述IPMI命令对应的返回数据。

步骤S14:将所述返回数据放置于所述静态随机存取存储器,以便所述主机BIOS从所述静态随机存取存储器中读取所述返回数据。

在具体的实施方式中,动态区域包括命令区和数据区,其中,所述命令区用于存放IPMI命令,数据区用于存放返回数据。

例如,主机BIOS向基板管理控制器的静态随机存取存储器下发询问服务器启动方式的IPMI命令,基板管理控制器获取到IPMI命令该命令,进行解析,得到解析数据,根据解析数据从用户配置数据中获取用户配置的服务器启动方式,比如为通过USB启动,得到返回数据。放置在于所述静态随机存取存储器,具体为动态区域中,主机BIOS从所述静态随机存取存储器中读取所述返回数据,之后通过USB启动。

需要指出的是,SRAM通过MMIO访问,走的是PCIE链路,和Smbus相比具有很好的稳定性。

可见,本申请实施例从基板管理控制器的静态随机存取存储器中读取IPMI命令;其中,所述IPMI命令为主机BIOS下发至所述静态随机存取存储器的命令,并且,所述静态随机存取存储器在PEI阶段使能;解析所述IPMI命令,得到所述IPMI命令的解析数据;根据所述解析数据确定所述IPMI命令对应的返回数据;将所述返回数据放置于所述静态随机存取存储器,以便所述主机BIOS从所述静态随机存取存储器中读取所述返回数据。也即,本申请中的主机与基板管理控制器之间的通信基于静态随机存取存储器实现IPMI协议,主机与基板管理控制器之间通过共享静态随机存取存储器进行IPMI通信,数据传输速度快,并且,静态随机存取存储器在PEI阶段使能,使静态随机存取存储器在开机早期便能够用于进行IPMI通信,这样,能够提升主机和基板管理控制器之间的通信效率,从而提升开机速度,并且稳定性好,可用阶段早。

参见图2所示,本申请实施例公开了一种具体的主机和基板管理控制器之间的通信方法,应用于基板管理控制器,包括:

步骤S21:从基板管理控制器的静态随机存取存储器中读取IPMI命令;其中,所述IPMI命令为主机BIOS下发至所述静态随机存取存储器的命令,并且,所述静态随机存取存储器在PEI阶段使能。

步骤S22:解析所述IPMI命令,得到所述IPMI命令的解析数据。

步骤S23:根据所述解析数据确定所述IPMI命令对应的返回数据。

步骤S24:将所述返回数据放置于所述静态随机存取存储器,以便所述主机BIOS从所述静态随机存取存储器中读取所述返回数据。

步骤S25:在主机进入操作系统前,将所述静态随机存取存储器锁定。

也即,本申请实施例包括保护机制,在主机进入操作系统前,将所述静态随机存取存储器锁定,进行访问控制,以提升通信安全性。

需要指出的是,在另外一些实施例中,也可以利用BIOS通过软件或硬件在主机进入操作系统前,将所述静态随机存取存储器锁定,其中,硬件方式较为可靠。

步骤S26:根据预设IPMI命令通信控制模式对主机操作系统下发的IPMI命令进行认证,若认证通过,则允许所述主机操作系统访问所述静态随机存取存储器。

其中,所述预设IPMI命令通信控制模式为根据IPMI命令类型预设的模式,标准IPMI命令的预设IPMI命令通信控制模式为兼容模式,非标准IPMI命令的预设IPMI命令通信控制模式为保护模式。其中,非标准IPMI命令为Customized(定制化)命令。

相应的,所述根据预设IPMI命令通信控制模式对主机操作系统下发的IPMI命令进行认证,包括:

利用第一预设认证方式对主机操作系统下发的标准IPMI命令进行认证,以及利用第二预设认证方式对主机操作系统下发的非标准IPMI命令进行认证。

需要指出的是,第一预设认证方式可以为简单的用户名、密码认证,第二预设认证方式利用复杂度较高的认证方式。

也即,本申请实施例可以兼容标准IPMI命令和非标准IPMI命令,继承了IPMI协议的兼容性和广泛性,具有较高的兼容性。

在具体的实施方式中,可以增加控制开关,以设置IPMI命令通信控制模式。对于标准IPMI命令,可设置默认值为使能状态,即兼容模式,对于非标准IPMI命令,默认设置可为保护模式。

在另外一些实施例中,可以根据用户需要,将所有类型的IPMI命令的IPMI命令通信控制模式设置为保护模式或兼容模式。

步骤S27:当所述主机操作系统访问完所述静态随机存取存储器,则将所述静态随机存取存储器重新锁定。

在具体的实施方式中,当所述主机操作系统访问完所述静态随机存取存储器的动态区域,则将所述静态随机存取存储器的动态区域重新锁定。

另外,对于静态区域,在主机进入操作系统前,将静态随机存取存储器锁定,具体为将静态区域和动态区域均锁定。也即,静态区域在主机进入操作系统前,也会被锁定。主机操作系统访问静态区域,基板管理控制器进行安全认证,认证通过后,允许主机操作系系统访问静态区域,访问完成后,重新锁定静态区域。

参见图3所示,图3为本申请实施例公开的一种主机和基板管理控制器之间的通信方法流程图。在PEI早期初始化BMC SRAM,在进入操作系统前,开启保护机制锁定SRAM,在主机操作系统运行阶段,对SRAM访问需要进行访问认证,访问完成后重新锁定,开启保护。其中,UEFI(Unified Extensible Firmware Interface,即统一可扩展固件接口),OS(即Operation System 操作系统)。其中,图3中箭头上的省略号表示启动阶段中的相应步骤,可以参考现有技术。

参见图4所示,图4为本申请实施例公开的一种具体的主机和基板管理控制器之间的通信方法流程图。

参见表1所示,表1为本申请方案与现有方案的效果比对。

表1

可见,现有技术存在以下特点:

1.Ipmi Over Kcs:在Kcs接口上实现IPMI协议,使用IO口传输,速度慢,保护机制较弱。

2.Ipmi Over BT:在BT接口上实现IPMI协议,使用IO端口传输,支持块传输,速度较快,保护机制较弱。

3.Ipmi Over SSIF:在Smbus接口上实现IPMI协议,稳定性较差,速度慢。

4.Ipmi Over SMIC:使用较少,需要单独的芯片支持,使用IO传输,没有明显优势。

5.Ipmi Over Usb:在Usb接口上实现IPMI协议,传输速度快,兼容性和稳定性较差,需要Usb驱动初始化完成后才能使用,可用阶段较晚。

而本申请提供的方案,在SRAM上实现IPMI协议,既可以实现IPMI通信,又同时实现SRAM通信,利用SRAM超大块传输实现快速传输,有中断机制和安全机制。这样,利用SRAM超大块传输实现快速传输改进了IPMI通信速度慢的缺点。改进了Ipmi Over Usb技术可用性差的特点,在服务器启动和运行的整个阶段均可使用,保持了IPMI的高可用性和兼容性。将SRAM划分为静态区域和动态区域,在实现IPMI协议的同时,还实现了SRAM通信机制,满足定制化需求,实现易用且安全的定制化交互接口。本申请的安全机制,中断机制等。在实现传输的兼容性和高速性的同时保持了安全性和高效性。可见,本申请方案既克服传统的IPMI交互接口速度慢,安全保护机制若弱的缺点,又克服一些非标准化交互接口兼容性差,通用性弱的,需要不断根据实际需求修改的缺点,实现传输速度快,安全机制强,兼容性强,稳定性好等特性。从而提高了Host与BMC交互的速度,安全性和高效性,并保持了兼容性。这样,提高了服务器的开机速度,提高了服务器的可用性和可服务性。因为通信更加安全,也提高了服务器的安全性,为服务器的安全稳定运行提供了保障。由于兼容性好,通用性强,接口实现后可以迭代使用,减少了维护成本。

另外,现有的SRAM方案仅用于交互定制化的数据,实现自定义的定制化协议。开机阶段BIOS和BMC之间的大量IPMI交互仍然使用传统的IPMI实现方式,传统IPMI实现的缺陷(见表1)并没有改善。只有在BDS阶段,PCIE初始化完成后可用,可用性有限。

而本申请方案:对现有SRAM方案进行了改进,使得整个启动阶段包括PEI,DXE,BDS,均可使用SRAM,满足了IPMI协议整个启动阶段可用的需求,从而支持在SRAM上实现IPMI协议。既支持交互定制化的数据和自定义的协议,满足定制化需求,又基于SRAM实现IPMI协议,支持超大块传输,提升了IPMI的性能,缩短了开机阶段BIOS和BMC之间的大量IPMI交互所用的时间,从而加快了开机速度,提升了服务器的可用性。

另外,IPMI协议可以基于BMC中的两种SRAM,其中,电池供电的SRAM,在断电的情况下,仍然能保持静态区域的数据,电源恢复后可以恢复配置不丢失。本技术的思想可用于其他领域,将上层协议基于不同的接口,总线或媒介实现。在保持兼容性的同时,提高安全性和效率。

参见图5所示,本申请实施例公开了一种主机和基板管理控制器之间的通信装置,应用于基板管理控制器,包括:

IPMI命令获取模块11,用于从基板管理控制器的静态随机存取存储器中读取IPMI命令;其中,所述IPMI命令为主机BIOS下发至所述静态随机存取存储器的命令,并且,所述静态随机存取存储器在PEI阶段使能;

IPMI命令解析模块12,用于解析所述IPMI命令,得到所述IPMI命令的解析数据;

返回数据确定模块13,用于根据所述解析数据确定所述IPMI命令对应的返回数据;

返回数据放置模块14,用于将所述返回数据放置于所述静态随机存取存储器,以便所述主机BIOS从所述静态随机存取存储器中读取所述返回数据。

可见,本申请从基板管理控制器的静态随机存取存储器中读取IPMI命令;其中,所述IPMI命令为主机BIOS下发至所述静态随机存取存储器的命令,并且,所述静态随机存取存储器在PEI阶段使能;解析所述IPMI命令,得到所述IPMI命令的解析数据;根据所述解析数据确定所述IPMI命令对应的返回数据;将所述返回数据放置于所述静态随机存取存储器,以便所述主机BIOS从所述静态随机存取存储器中读取所述返回数据。也即,本申请中的主机与基板管理控制器之间的通信基于静态随机存取存储器实现IPMI协议,主机与基板管理控制器之间通过共享静态随机存取存储器进行IPMI通信,数据传输速度快,并且,静态随机存取存储器在PEI阶段使能,使静态随机存取存储器在开机早起便能够用于进行IPMI通信,这样,能够提升主机和基板管理控制器之间的通信效率,从而提升开机速度,并且稳定性好,可用阶段早。

其中,IPMI命令获取模块11,具体用于当发生预设中断,则从基板管理控制器的静态随机存取存储器中读取IPMI命令。

并且,IPMI命令获取模块11,具体用于从基板管理控制器的静态随机存取存储器的动态区域中读取IPMI命令;

其中,所述动态区域为所述主机BIOS在所述静态随机存取存储器中划分的用于进行IPMI命令交互的存储区域;并且,所述静态随机存取存储器还包括由所述主机BIOS划分的静态区域,用于存放静态数据。

另外,所述装置还包括静态随机存取存储器访问控制模块,用于在主机进入操作系统前,将所述静态随机存取存储器锁定。

进一步的,所述装置还包括命令认证模块,用于根据预设IPMI命令通信控制模式对主机操作系统下发的IPMI命令进行认证,若认证通过,则允许所述主机操作系统访问所述静态随机存取存储器。

其中,所述预设IPMI命令通信控制模式为根据IPMI命令类型预设的模式,标准IPMI命令的预设IPMI命令通信控制模式为兼容模式,非标准IPMI命令的预设IPMI命令通信控制模式为保护模式;

相应的,命令认证模块,用于利用第一预设认证方式对主机操作系统下发的标准IPMI命令进行认证,以及利用第二预设认证方式对主机操作系统下发的非标准IPMI命令进行认证。

静态随机存取存储器访问控制模块还用于当所述主机操作系统访问完所述静态随机存取存储器,则将所述静态随机存取存储器重新锁定。

参见图6所示,本申请实施例公开了一种电子设备,包括处理器21和存储器22;其中,所述存储器22,用于保存计算机程序;所述处理器21,用于执行所述计算机程序,以实现前述实施例公开的主机和基板管理控制器之间的通信方法。

关于上述主机和基板管理控制器之间的通信方法的具体过程可以参考前述实施例中公开的相应内容,在此不再进行赘述。

进一步的,本申请实施例还公开了一种计算机可读存储介质,用于保存计算机程序,其中,所述计算机程序被处理器执行时实现前述实施例公开的主机和基板管理控制器之间的通信方法。

关于上述主机和基板管理控制器之间的通信方法的具体过程可以参考前述实施例中公开的相应内容,在此不再进行赘述。

本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其它实施例的不同之处,各个实施例之间相同或相似部分互相参见即可。对于实施例公开的装置而言,由于其与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

结合本文中所公开的实施例描述的方法或算法的步骤可以直接用硬件、处理器执行的软件模块,或者二者的结合来实施。软件模块可以置于随机存储器(RAM)、内存、只读存储器(ROM)、电可编程ROM、电可擦除可编程ROM、寄存器、硬盘、可移动磁盘、CD-ROM、或技术领域内所公知的任意其它形式的存储介质中。

以上对本申请所提供的一种主机和基板管理控制器之间的通信方法、装置、设备进行了详细介绍,本文中应用了具体个例对本申请的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本申请的方法及其核心思想;同时,对于本领域的一般技术人员,依据本申请的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本申请的限制。

- 一种主机和基板管理控制器之间的通信方法、装置、设备

- 一种主机和基板管理控制器之间的通信方法、装置、设备