一种半导体衬底及半导体结构的制备方法

文献发布时间:2023-06-19 12:21:13

技术领域

本发明涉及半导体生产工艺领域,特别涉及一种半导体衬底及半导体结构的制备方法。

背景技术

Ge材料相对Si材料具有更优异的载流子迁移率,其电子迁移率与空穴迁移率分别是Si的2.6倍与4.2倍。对于绝大多数晶体管及其集成电路,高迁移率意味着载流子渡越基区的时间减少,可有效地提高其工作频率、速度和放大性能。

目前常规GeOI(绝缘体上锗)是采用Si上外延Ge然后键合的方式制备,由于Ge的晶格常数要远大于Si,所以在Si上生长的Ge是压应变的。虽然采用压力键合会补偿一部分应变,但远不够补偿生长引入的应变。单一压应变的GOI限制了衬底的应用,在很多器件性能上不能发挥出最优模式。

为此,提出本发明。

发明内容

本发明的主要目的在于提供一种半导体衬底的制备方法,该方法能够生长出高质量的拉应变的GeOI层。

本发明的另一目的在于提供一种半导体结构的制备方法,该方法能够生长出高质量的拉应变的GeOI层,利用其制作的器件可靠性高。

为了实现以上目的,本发明提供了以下技术方案。

一种半导体衬底的制备方法,包括:

在硅衬底上外延锗缓冲层,

在所述锗缓冲层表面生长第一绝缘层;

图形化刻蚀所述第一绝缘层,形成多个凹槽;

外延生长锗锡层;

外延生长锗层。

一种半导体结构的制备方法,包括:

提供支撑衬底,在所述支撑衬底生长第二绝缘层;

利用上文所述的制备方法制得半导体衬底;

将所述支撑衬底与所述半导体衬底键合,并且所述第二绝缘层与所述锗层相邻;

去除所述硅衬底、所述锗缓冲层、所述第一绝缘层和所述锗锡层。

与现有技术相比,本发明达到了以下技术效果:

(1)在硅衬底上形成锗缓冲层和第一绝缘层,然后图形化第一绝缘层,之后生长的锗锡层,如此,锗锡层的大部分位错和缺陷就可以被限制在第一绝缘层的图形区域内,因此锗锡层本身质量高,在其上生长的锗(IV族材料)层也必然具有较高的质量。同时由于应变释放后的GeSn材料其晶格常数要大于Ge,所以其上外延的Ge是拉应变(Tensile)的。

(2)本发明还通过键合的手段将外延生长拉应变锗转移至简单衬底上,该过程中无需离子注入,也不会引入大量缺陷,制备的器件可靠性高。

附图说明

通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选实施方式的目的,而并不认为是对本发明的限制。

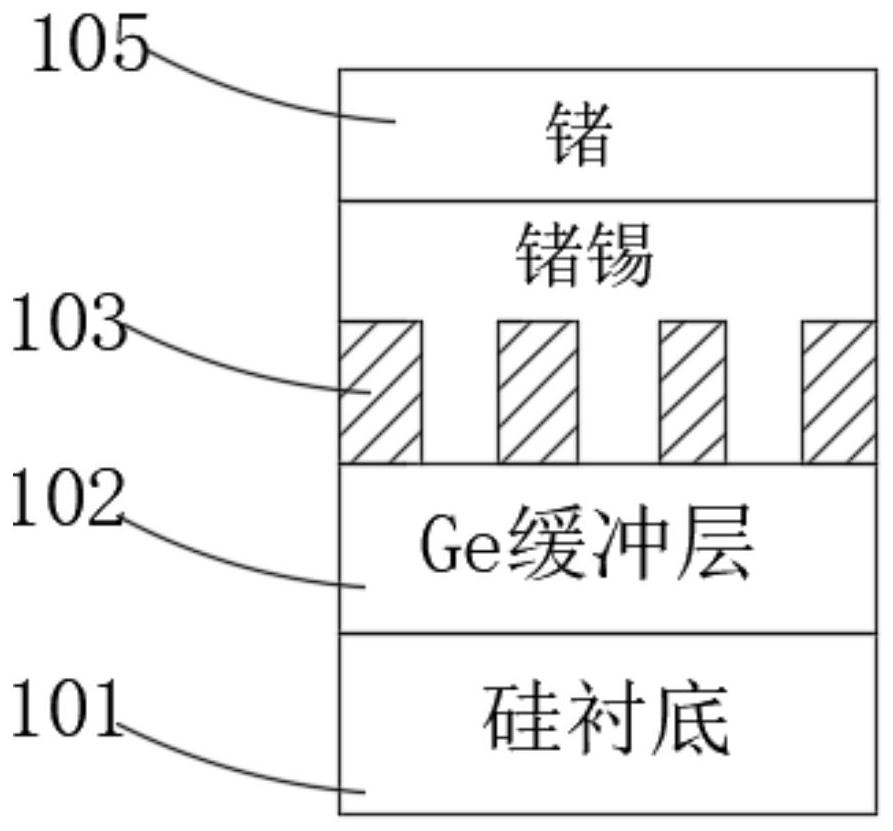

图1至图5为本发明制备半导体衬底时不同阶段的结构示意图;

图6至图8为本发明制备一种半导体结构时不同阶段的结构示意图。

具体实施方式

以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性的,而并非要限制本公开的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本公开的概念。

在附图中示出了根据本公开实施例的各种结构示意图。这些图并非是按比例绘制的,其中为了清楚表达的目的,放大了某些细节,并且可能省略了某些细节。图中所示出的各种区域、层的形状以及它们之间的相对大小、位置关系仅是示例性的,实际中可能由于制造公差或技术限制而有所偏差,并且本领域技术人员根据实际所需可以另外设计具有不同形状、大小、相对位置的区域/层。

在本公开的上下文中,当将一层/元件称作位于另一层/元件“上”时,该层/元件可以直接位于该另一层/元件上,或者它们之间可以存在居中层/元件。另外,如果在一种朝向中一层/元件位于另一层/元件“上”,那么当调转朝向时,该层/元件可以位于该另一层/元件“下”。

为了在衬底上生长出高质量和应变释放性能的IV材料层,本发明提供了以下方法。

第一步,如图1所示,在硅衬底101上外延锗缓冲层102,该锗缓冲层102的生长方式可以是高低温生长法,缓冲法等。

第二步,如图2所示,生长第一绝缘层103;该第一绝缘层103可以是氧化物、氮化物等绝缘材料,例如常见的氮化硅、氧化硅、氧化铝等。生长方法包括但不限于APCVD、UHVCVD、LPCVD、RTCVD、PECVD或氧化生长等。

第三步,如图3所示,图形化刻蚀所述第一绝缘层103,形成多个凹槽103a。通常采用光刻和刻蚀结合,刻蚀可以结合CMP、湿法腐蚀、干法刻蚀、原子层腐蚀(ALE)(干法或湿法)、气体氧化+湿法腐蚀等手段。这一步形成的凹槽可容纳Ge

第四步,如图4所示,外延生长锗锡层104。锗锡层的位错和缺陷被限制在第一绝缘层的凹槽图形内,因此具有较高的质量,为生长高质量的锗提供先决条件。同时由于应变释放后的GeSn材料其晶格常数要大于Ge,所以其上外延的Ge是拉应变(Tensile)的。

第五步,如图5所示,外延生长锗层105。

以上获得的衬底用途广泛,使用时通常将上述衬底上的锗层转移至简单衬底上,下文具体介绍转移的方法流程。

第一步,如图6所示,提供支撑衬底201,该支撑衬底可以是本领域技术人员熟知的任何用以承载半导体集成电路组成元件的底材,例如绝缘体上硅(silicon-on-insulator,SOI)、体硅(bulk silicon)、锗硅等,或者是已经在上述基础衬底上制作出电路等结构的衬底。

第二步,在支撑衬底上生长第二绝缘层202;该第二绝缘层202可以是氧化物、氮化物等绝缘材料,例如常见的氮化硅、氧化硅、氧化铝等。生长方法包括但不限于APCVD、UHVCVD、LPCVD、RTCVD、PECVD或氧化生长等。

第三步,键合。将上文图5所示的半导体衬底与图6所示的支撑衬底键合,使所述第二绝缘层202与锗层105相邻,如图7所示。在键合之前还可以对两个衬底进行预处理,例如磨抛等。

第四步,去除所述硅衬底101、所述锗缓冲层102、所述第一绝缘层103和所述锗锡层104,得到如图8所示的结构。去除的手段不限,包括但不限于磨抛、湿法腐蚀、干法刻蚀和CMP之间的任意组合等。

以上对本公开的实施例进行了描述。但是,这些实施例仅仅是为了说明的目的,而并非为了限制本公开的范围。本公开的范围由所附权利要求及其等价物限定。不脱离本公开的范围,本领域技术人员可以做出多种替代和修改,这些替代和修改都应落在本公开的范围之内。

- 衬底结构、包含衬底结构的半导体封装结构,以及制造半导体封装结构的半导体工艺

- 半导体衬底及具有半导体衬底的半导体封装结构