应用于探测器的实时偏置校正方法、系统、介质及设备

文献发布时间:2023-06-19 18:27:32

技术领域

本发明属于平板探测器及线阵探测器领域,尤其涉及应用于探测器的实时偏置校正方法、系统、介质及设备。

背景技术

平板探测器及线阵探测器是一种将X射线能量转换为电信号的设备,就其硬件电路而言,通常包含无源的多行多列的像素阵列及有源的信号读出阵列,其中有源的信号读出阵列根据架构不同可能包括行选通电路、多选一电路、积分电路、PGA电路、模数转换电路以及数据处理电路等。平板探测器及线阵探测器采用rollingshutter快门模式,其通过逐行扫描完成整个像素阵列的扫描,在一个典型的APS像素架构平板探测器中,同一列上的多行像素通常会共用一套列信号读出电路,这些电路通常会因为供电波动、外界工频干扰等问题存在一些低频干扰,因此在平板探测器及线阵探测器的使用中通常需要加入实时偏置校正以消除这部分低频干扰。

传统的实时偏置校正方法通常包括使用带有双采样功能(DDS)或者暗场行像素采样功能(DRS)的探测器。DDS功能的实现思路是在每个像素信号正常读出以后将像素复位并再次采集复位下的输出,将2次输出通过硬件或程序相减以达到消除低频干扰的目的。DRS功能的实现思路是在正常感光像素阵列的开始行之前或结束行之后加入进行物理遮光的像素,在正常感光像素读出时扣除对应列的暗像素输出,以达到消除低频干扰的目的。

通过原理可以发现,DDS功能在像素信号读出后通过像素复位得到后级信号读出电路的偏置信号输出,利用像素读出时刻与后级信号读出电路偏置读出时刻在时间上足够接近的特性,消除以单像素采集频率为上限的较高频率的干扰。但也可发现,DDS功能较为复杂,每个像素均需采集2次输出,因此其包含几个明显的缺点:1.DDS功能通常需要较为复杂的功能电路支持,极大的降低了芯片良率;2.DDS功能下每个像素均需要采集2次,数据量增大为原来的2倍,极大的影响了极限帧速率;3.2次数据的相减会增加噪声至单次数据采集的1.41倍。

DRS功能可以扣除以一帧图像采集频率为上限的稍低频干扰,但其也存在几个明显的缺点:1.DRS功能在物理上需要增加额外的像素行,会较大幅度的增加芯片面积;2.DRS功能通常在芯片表面进行平面级的物理遮光,但由于光的扩散特性,靠近正常像素的遮光像素通常会存在漏光现象不能使用,进一步的增加了所需像素行的数量;3.由于挂载像素引入的输入端寄生电容及减法的存在,DRS功能下噪声的增加幅度较大,且与暗像素的行数存在相关性,行数越多,单列像素中可用于平均的暗像素越多,噪声增加幅度则越小,但相应的芯片面积将显著增加。

总结而言,DDS功能引入的问题主要包括:(1)需要复杂的硬件功能电路支持,降低了芯片良率;(2)显著降低探测器的极限帧速率;(3)显著增大了校正后的暗场图像噪声。DRS功能引入的问题主要包括:(1)需要额外像素电路支持,增大了芯片面积;(2)不易对像素进行有效遮光;(3)校正后的暗场图像噪声存在一定的增加。

发明内容

本发明所要解决的技术问题是提供应用于探测器的实时偏置校正方法、系统、介质及设备。

本发明解决上述技术问题的技术方案如下:一种应用于探测器的实时偏置校正方法,包括:

步骤1,控制探测器中像素阵列与后级列信号读出电路之间的模拟开关关断,同时控制所述后级列信号读出电路的输入端为复位状态;

步骤2,在所述复位状态下,采集所述探测器中列模数转换电路的第一数字输出值,将第一数字输出值作为所述像素阵列中每列对应的偏置系数;

步骤3,控制所述模拟开关打开,同时控制所述后级列信号读出电路的输入端为工作状态;

步骤4,在所述工作状态下,采集所述探测器中列模数转换电路的第二数字输出值,将第二数字输出值与每列的偏置系数相减,得到当前行的多列像素完成实时偏置校正后的校正输出值;

步骤5,逐行扫描并重复步骤3至步骤4,直至获得所述像素阵列全部像素的校正输出值。

本发明的有益效果是:本发明通过断开无源像素阵列与后级有源电路的联系并直接采集后级电路的输出来得到实时的列偏置系数,通过正常像素读出时后级电路输出与对应列偏置系数直接相减来达到实时偏置校正的目的。相比于DDS功能,本发明无需增加复杂的硬件电路,几乎不影响良率,完全不增加面积;相比于DRS功能,由于未挂载像素阵列时后级电路的噪声更小,相同条件下本发明对极限帧速率及噪声的影响更小;同时由于没有物理暗像素数量的限制,本发明具有非常好的灵活性,可根据需要在噪声与极限帧速率之间选取最为合适的平衡。

在上述技术方案的基础上,本发明还可以做如下改进。

进一步,所述步骤1具体为:

在所述探测器处于曝光时间时,通过寄存器配置像素阵列与后级列信号读出电路之间的模拟开关关断,同时,通过寄存器配置控制所述后级列信号读出电路的输入端为复位状态。

进一步,所述步骤2之后还包括:

将每列的偏置系数与所述像素阵列一一对应形成像素对,存储至所述探测器的存储装置中。

进一步,所述采集所述探测器中列模数转换电路的第一数字输出值的过程为:

将经线性转换后的所述模数转换电路的单次采集数字输出值作为第一数字输出值;

或将经线性转换后的所述模数转换电路的多次采集数字输出值的平均值作为第一数字输出值。

本发明解决上述技术问题的另一种技术方案如下:一种应用于探测器的实时偏置校正系统,包括:

第一控制模块,用于控制探测器中像素阵列与后级列信号读出电路之间的模拟开关关断,同时控制所述后级列信号读出电路的输入端为复位状态;

第一采集模块,用于在所述复位状态下,采集所述探测器中每路模数转换电路的第一数字输出值,将每路的第一数字输出值作为所述像素阵列中每列对应的偏置系数;

第二控制模块,用于控制所述模拟开关打开,同时控制所述后级列信号读出电路的输入端为工作状态;

校正模块,用于在所述工作状态下,采集所述探测器中列模数转换电路的第二数字输出值,将第二数字输出值与每列的偏置系数相减,得到当前行多列像素完成实时偏置校正的校正输出值;

结果模块,用于逐行扫描并重复第二控制模块以及校正模块,直至获得所述像素阵列全部像素的校正输出值。

本发明的有益效果是:本发明通过断开无源像素阵列与后级有源电路的联系并直接采集后级电路的输出来得到实时的列偏置系数,通过正常像素读出时后级电路输出与对应列偏置系数直接相减来达到实时偏置校正的目的。相比于DDS功能,本发明无需增加复杂的硬件电路,几乎不影响良率,完全不增加面积;相比于DRS功能,由于未挂载像素阵列时后级电路的噪声更小,相同条件下本发明对极限帧速率及噪声的影响更小;同时由于没有物理暗像素数量的限制,本发明具有非常好的灵活性,可根据需要在噪声与极限帧速率之间选取最为合适的平衡。

进一步,所述第一控制模块具体用于:

在所述探测器处于曝光时间时,通过寄存器配置像素阵列与后级列信号读出电路之间的模拟开关关断,同时,通过寄存器配置控制所述后级列信号读出电路的输入端为复位状态。

进一步,还包括:

存储模块,用于将每列的偏置系数与所述像素阵列一一对应形成像素对,存储至所述探测器的存储装置中。

进一步,所述第一采集模块具体用于:

所述采集所述探测器中每路模数转换电路的第一数字输出值的过程为:

将经线性转换后的所述模数转换电路的单次采集数字输出值作为第一数字输出值;

或将经线性转换后的所述模数转换电路的多次采集数字输出值的平均值作为第一数字输出值。

本发明解决上述技术问题的另一种技术方案如下:一种存储介质,所述存储介质中存储有指令,当计算机读取所述指令时,使所述计算机执行如上述任一项所述的一种应用于探测器的实时偏置校正方法。

本发明的有益效果是:本发明通过断开无源像素阵列与后级有源电路的联系并直接采集后级电路的输出来得到实时的列偏置系数,通过正常像素读出时后级电路输出与对应列偏置系数直接相减来达到实时偏置校正的目的。相比于DDS功能,本发明无需增加复杂的硬件电路,几乎不影响良率,完全不增加面积;相比DRS功能,由于未挂载像素阵列时后级电路的噪声更小,相同条件下本发明对极限帧速率及噪声的影响更小;同时由于没有物理暗像素数量的限制,本发明具有非常好的灵活性,可根据需要在噪声与极限帧速率之间选取最为合适的平衡。

本发明解决上述技术问题的另一种技术方案如下:一种电子设备,包括上述存储介质、执行上述存储介质内的指令的处理器。

本发明的有益效果是:本发明通过断开无源像素阵列与后级有源电路的联系并直接采集后级电路的输出来得到实时的列偏置系数,通过正常像素读出时后级电路输出与对应列偏置系数直接相减来达到实时校正的目的。相比于DDS功能,本发明无需增加复杂的硬件电路,几乎不影响良率,完全不增加面积;相比于DRS功能,由于未挂载像素阵列时后级电路的噪声更小,相同条件下本发明对极限帧速率及噪声的影响更小;同时由于没有物理暗像素数量的限制,本发明具有非常好的灵活性,可根据需要在噪声与极限帧速率之间选取最为合适的平衡。

附图说明

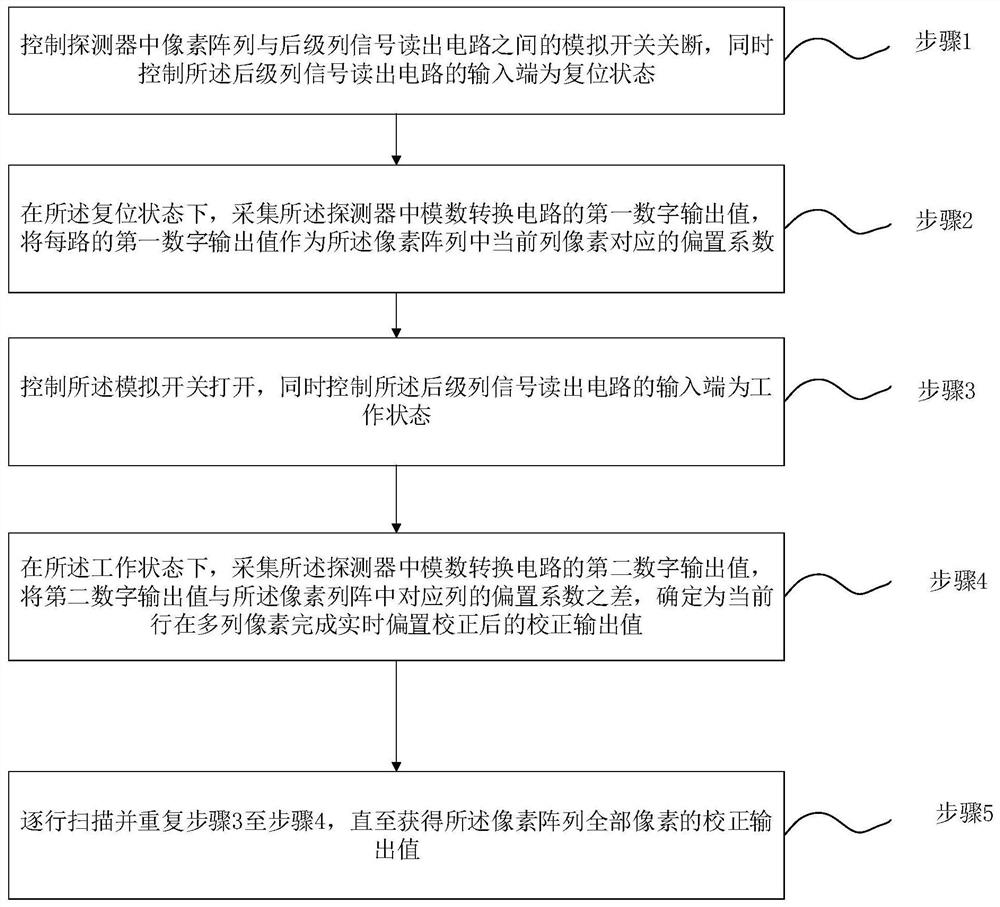

图1为本发明一种应用于探测器的实时偏置校正方法实施例提供的流程示意图;

图2为本发明一种应用于探测器的实时偏置校正系统实施例提供的结构框架图;

图3为本发明一种应用于探测器的实时偏置校正方法实施例提供的电路结构图。

具体实施方式

以下对本发明的原理和特征进行描述,所举实例只用于解释本发明,并非用于限定本发明的范围。

如图1所示,一种应用于探测器的实时偏置校正方法,包括:

步骤1,控制探测器中像素阵列与后级列信号读出电路之间的模拟开关关断,同时控制所述后级列信号读出电路的输入端为复位状态;

步骤2,在所述复位状态下,采集所述探测器中列模数转换电路的第一数字输出值,将第一数字输出值作为所述像素阵列中每列对应的偏置系数;

步骤3,控制所述模拟开关打开,同时控制所述后级列信号读出电路的输入端为工作状态;

步骤4,在所述工作状态下,采集所述探测器中列模数转换电路的第二数字输出值,将第二数字输出值与对应列的偏置系数相减,得到当前行的多列像素完成实时偏置校正的校正输出值;

步骤5,逐行扫描并重复步骤3至步骤4,直至获得所述像素阵列全部像素的校正输出值。

在一些可能的实施方式中,本发明通过断开无源像素阵列与后级有源电路的联系并直接采集后级电路的输出来得到实时的列偏置系数,通过正常像素读出时后级电路输出与对应列偏置系数直接相减来达到实时校正的目的。相比于DDS功能,本发明无需增加复杂的硬件电路,几乎不影响良率,完全不增加面积;相比于DRS功能,由于未挂载像素阵列时后级电路的噪声更小,相同条件下本发明对极限帧速率及噪声的影响更小;同时由于没有物理暗像素数量的限制,本发明具有非常好的灵活性,可根据需要在噪声与极限帧速率之间选取最为合适的平衡。需要说明的是,步骤1,控制探测器中像素阵列与后级列信号读出电路之间的模拟开关关断,同时控制所述后级列信号读出电路的输入端为复位状态的具体过程为:

通过一定的措施将平板探测器或线阵探测器模拟链路中后级电路的输入与对应像素电荷输出之间的联系断开;根据具体应用确定后级电路的输入端状态;需注意,措施包括但不限于①通过寄存器配置或IO输入特定波形关断前级电路与后级电路之间的开关②通过寄存器配置或IO输入特定波形关断前级电路的输出③通过切断部分电源关闭前级电路的输出④通过寄存器配置或IO输入特定波形将前级电路的输出置于固定电压。后级电路针对整个模拟电路而言,其可以是位于像素阵列之后的所有模拟电路,也可以是像素阵列后模拟电路中的某一部分。联系断开,指的是后级电路输入与其对应的前级像素电荷输出间不存在任何直接的或间接的物理上的连接。后级电路的输入端状态包括但不限于悬空、高阻或置于固定的电压。确定后级输入端状态的方法,关键点在于尽可能的接近像素电荷输出联系未断开时的工作状态。

步骤2,在所述复位状态下,采集所述探测器中列模数转换电路的第一数字输出值,将第一数字输出值作为所述像素阵列中每列对应的偏置系数的具体过程为:

采集后级电路的输出并生成多列对应的偏置系数;后级电路的输出,指的是后级电路中经模数转换电路后的数字输出。后级电路的输出采集,可单次采集以实现最优的极限帧速率,或根据实际需要设置多次采集的次数以实现极限帧速率及噪声之间的最优平衡。偏置系数生成方法,可由模数转换电路的单次数字输出经一定线性转换后得到,也可将多次数字输出平均后经一定线性转换后得到。步骤3之前还包括:

将这些偏置系数整合为校正模板并存储;偏置系数整合为模板的方法,通常是根据列偏置系数所处的列信号处理电路位置建立校正系数—物理列数对应表。

步骤4,在所述工作状态下,采集所述探测器中列模数转换电路的第二数字输出值,将第二数字输出值与对应列的偏置系数相减,得到当前行的多列像素完成实时偏置校正的校正输出值的具体过程为:

在正常采集图像时,在每个像素对应的输出中减去其对应的列偏置系数;

实施例1,以像素矩阵为1024*1024的16位APS平板探测器为例,其典型的模拟电路部分如图3所示,像素矩阵具有1024列像素,每列像素共用一路积分电路+PGA电路+模数转换电路作为列信号读出电路,像素及各级电路之间均具有可通过寄存器配置关断/打开的模拟开关。使用该平板实现本发明所描述的实时偏置校正时,一种典型的方法及步骤如下:

1.在平板探测器处于曝光时间时,通过寄存器配置关断像素阵列与后级列信号读出电路之间的模拟开关;

2.通过寄存器配置将后级列信号读出电路的输入端置于复位状态;

3.得到此时单次采集下1024列模数转换电路的数字输出作为每一列的偏置系数;

4.将1024个偏置系数与1024列像素一一对应,记录为b1~b1024存储在主处理器的片上存储器中;

5.通过寄存器配置打开像素阵列与后级列信号读出电路之间的模拟开关,并将后级列信号读出电路的输入端置于正常工作状态;

6.在平板探测器处于某一行图像采集时,第n列像素对应的第n列模数转换电路输出减去偏置系数bn即得到当列完成实时偏置校正后的校正输出,通过此方法可得到当前行第1~1024列的校正输出;

7.通过行扫描电路完成首行到末行的图像采集,并重复步骤6完成整个像素阵列的实时偏置校正。

可以看到,在本实施实例中,使用到的额外功能电路仅包含开关,而由于行扫描概念的存在,开关通常已经存在于常用的平板探测器及线阵探测器中。同时,由于开关断开时后级有源电路未挂载像素,因此相同条件下本方法相对于DRS功能噪声更低。并且相对于DRS功能多暗像素的使用需要芯片硬件支持,本发明可在前级无源像素与任意后级电路联系断开时不断采集偏置值,因此具有更优的灵活性及应用性。

优选地,在上述任意实施例中,所述步骤1具体为:

在所述探测器处于曝光时间时,通过寄存器配置像素阵列与后级列信号读出电路之间的模拟开关关断,同时,通过寄存器配置控制所述后级列信号读出电路的输入端为复位状态。

优选地,在上述任意实施例中,所述步骤2之后还包括:

将每列的偏置系数与所述像素阵列一一对应形成像素对,存储至所述探测器的存储装置中。

优选地,在上述任意实施例中,所述采集所述探测器中列模数转换电路的第一数字输出值的过程为:

将经线性转换后的所述模数转换电路的单次采集数字输出值作为第一数字输出值;

或将经线性转换后的所述模数转换电路的多次采集数字输出值的平均值作为第一数字输出值。

如图2所示,一种应用于探测器的实时偏置校正系统,包括:

第一控制模块100,用于控制探测器中像素阵列与后级列信号读出电路之间的模拟开关关断,同时控制所述后级列信号读出电路的输入端为复位状态;

第一采集模块200,用于在所述复位状态下,采集所述探测器中列模数转换电路的第一数字输出值,将第一数字输出值作为所述像素阵列中每列对应的偏置系数;

第二控制模块300,用于控制所述模拟开关打开,同时控制所述后级列信号读出电路的输入端为工作状态;

校正模块400,用于在所述工作状态下,采集所述探测器中列模数转换电路的第二数字输出值,将第二数字输出值与对应列的偏置系数相减,得到当前行多列像素完成实时偏置校正的校正输出值;

结果模块500,用于逐行扫描并重复第二控制模块以及校正模块,直至获得所述像素阵列全部像素的校正输出值。

在一些可能的实施方式中,本发明通过断开无源像素阵列与后级有源电路的联系并直接采集后级电路的输出来得到实时的列偏置系数,通过正常像素读出时后级电路输出与对应列偏置系数直接相减来达到实时校正的目的。相比于DDS功能,本发明无需增加复杂的硬件电路,几乎不影响良率,完全不增加面积;相比于DRS功能,由于未挂载像素阵列时后级电路的噪声更小,相同条件下本发明对极限帧速率及噪声的影响更小;同时由于没有物理暗像素数量的限制,本发明具有非常好的灵活性,可根据需要在噪声与极限帧速率之间选取最为合适的平衡。

优选地,在上述任意实施例中,所述第一控制模块100具体用于:

在所述探测器处于曝光时间时,通过寄存器配置像素阵列与后级列信号读出电路之间的模拟开关关断,同时,通过寄存器配置控制所述后级列信号读出电路的输入端为复位状态。

优选地,在上述任意实施例中,还包括:

存储模块,用于将每列的偏置系数与所述像素阵列一一对应形成像素对,存储至所述探测器的存储装置中。

优选地,在上述任意实施例中,所述第一构建模块具体用于:

所述采集所述探测器中每路模数转换电路的第一数字输出值的过程为:

将经线性转换后的所述模数转换电路的单次采集数字输出值作为第一数字输出值;

或将经线性转换后的所述模数转换电路的多次采集数字输出值的平均值作为第一数字输出值。

本发明解决上述技术问题的另一种技术方案如下:一种存储介质,所述存储介质中存储有指令,当计算机读取所述指令时,使所述计算机执行如上述任一项所述的一种应用于探测器的实时偏置校正方法。

在一些可能的实施方式中,本发明通过断开无源像素阵列与后级有源电路的联系并直接采集后级电路的输出来得到实时的列偏置系数,通过正常像素读出时后级电路输出与对应列偏置系数直接相减来达到实时校正的目的。相比于DDS功能,本发明无需增加复杂的硬件电路,几乎不影响良率,完全不增加面积;相比于DRS功能,由于未挂载像素阵列时后级电路的噪声更小,相同条件下本发明对极限帧速率及噪声的影响更小;同时由于没有物理暗像素数量的限制,本发明具有非常好的灵活性,可根据需要在噪声与极限帧速率之间选取最为合适的平衡。

本发明解决上述技术问题的另一种技术方案如下:一种电子设备,包括上述存储介质、执行上述存储介质内的指令的处理器。

在一些可能的实施方式中,本发明通过断开无源像素阵列与后级有源电路的联系并直接采集后级电路的输出来得到实时的列偏置系数,通过正常像素读出时后级电路输出与对应列偏置系数直接相减来达到实时校正的目的。相比于DDS功能,本发明无需增加复杂的硬件电路,几乎不影响良率,完全不增加面积;相比于DRS功能,由于未挂载像素阵列时后级电路的噪声更小,相同条件下本发明对极限帧速率及噪声的影响更小;同时由于没有物理暗像素数量的限制,本发明具有非常好的灵活性,可根据需要在噪声与极限帧速率之间选取最为合适的平衡。

读者应理解,在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任一个或多个实施例或示例中以合适的方式结合。此外,在不相互矛盾的情况下,本领域的技术人员可以将本说明书中描述的不同实施例或示例以及不同实施例或示例的特征进行结合和组合。

在本申请所提供的几个实施例中,应该理解到,所揭露的装置和方法,可以通过其它的方式实现。例如,以上所描述的方法实施例仅仅是示意性的,例如,步骤的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个步骤可以结合或者可以集成到另一个步骤,或一些特征可以忽略,或不执行。

上述方法如果以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分,或者该技术方案的全部或部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行本发明各个实施例方法的全部或部分步骤。而前述的存储介质包括:U盘、移动硬盘、只读存储器(ROM,Read-OnlyMemory)、随机存取存储器(RAM,RandomAccessMemory)、磁碟或者光盘等各种可以存储程序代码的介质。

以上,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到各种等效的修改或替换,这些修改或替换都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以权利要求的保护范围为准。

- 全景相机标定的校正方法、系统、计算机设备和存储介质

- 软件实时可信度量的方法、设备、系统及存储介质

- 伽马校正方法、装置、设备和存储介质

- 线阵探测器图像拼接实时校正方法、装置、设备和介质

- 线阵探测器图像拼接实时校正方法、装置、设备和介质