用于具有高压保护和阻抗控制的多驱动器架构的装置

文献发布时间:2023-06-19 18:32:25

本申请要求于2021年7月30日提交的美国临时申请号63/227,676的权益。美国临时申请号63/227,676的全部内容通过引用并入本文。

技术领域

本公开总体上涉及利用差分输出驱动器的装置和系统。特别地,本公开涉及可以使用具有恒定阻抗的输出电压来驱动另一电路的差分输出驱动器。

背景技术

驱动器电路(或驱动器)可以被用于通过调节流入受控电路的电流来控制另一电路。例如,晶体管驱动器可以实现为电流放大设备,该设备从低电流源(例如,逻辑门或传感器)接收输入电流并且将输入电流驱动到可以用于驱动诸如灯泡和电机等电路或组件的更高电流。在另一示例中,驱动器可以调节输入电压并且使用调节后的电压来驱动或控制另一组件。在另一示例中,计算设备可以使用包括多个输出驱动器的时钟发生器。时钟发生器可以接收输入时钟信号,并且多个驱动器可以将输入时钟信号驱动到更高电流以驱动在计算设备中实现的不同组件或应用。

发明内容

在一个实施例中,总体上描述了一种用于实现多驱动器架构的装置。该装置可以包括控制器,该控制器被配置为控制驱动器电路的内阻以使驱动器以恒定阻抗电平输出该输出电压。

在一个实施例中,总体上描述了一种用于实现多驱动器架构的装置。该装置可以包括被配置为接收输入电压的第一驱动器。该装置还可以包括被配置为接收输入电压的第二驱动器。该装置还可以包括预驱动器逻辑电路,该预驱动器逻辑电路被配置为选择第一驱动器和第二驱动器中的一者以将输入电压转换为输出电压。该装置还可以包括连接到第一驱动器和第二驱动器的控制器。该装置还可以包括连接在第一驱动器的输出端子与控制器之间的开关。控制器可以被配置为控制开关的内阻。响应于预驱动器逻辑电路选择第一驱动器,第一驱动器可以以恒定阻抗电平输出该输出电压。

在一个实施例中,总体上描述了一种用于实现多驱动器架构的系统。该系统可以包括电路和连接到该电路的装置。该装置可以包括被配置为接收输入电压的第一驱动器。该装置还可以包括被配置为接收输入电压的第二驱动器。该装置还可以包括预驱动器逻辑电路,该预驱动器逻辑电路被配置为选择第一驱动器和第二驱动器中的一者以将输入电压转换为输出电压。该装置还可以包括连接到第一驱动器和第二驱动器的控制器。该装置还可以包括连接在第一驱动器的输出端子与控制器之间的开关。控制器可以被配置为控制开关的内阻以选择第一驱动器和第二驱动器中的一者以将输入电压转换为输出电压。响应于预驱动器逻辑电路选择第一驱动器,第一驱动器可以输出恒定阻抗电平的输出电压。输出电压可以被提供给电路,而无需使用在装置和电路外部的端接电阻器。

前述概述仅是说明性的并且不旨在以任何方式进行限制。除了上述说明性方面、实施例和特征之外,通过参考附图和以下详细描述,其他方面、实施例和特征将变得很清楚。在附图中,相同的附图标记表示相同或功能相似的元素。

附图说明

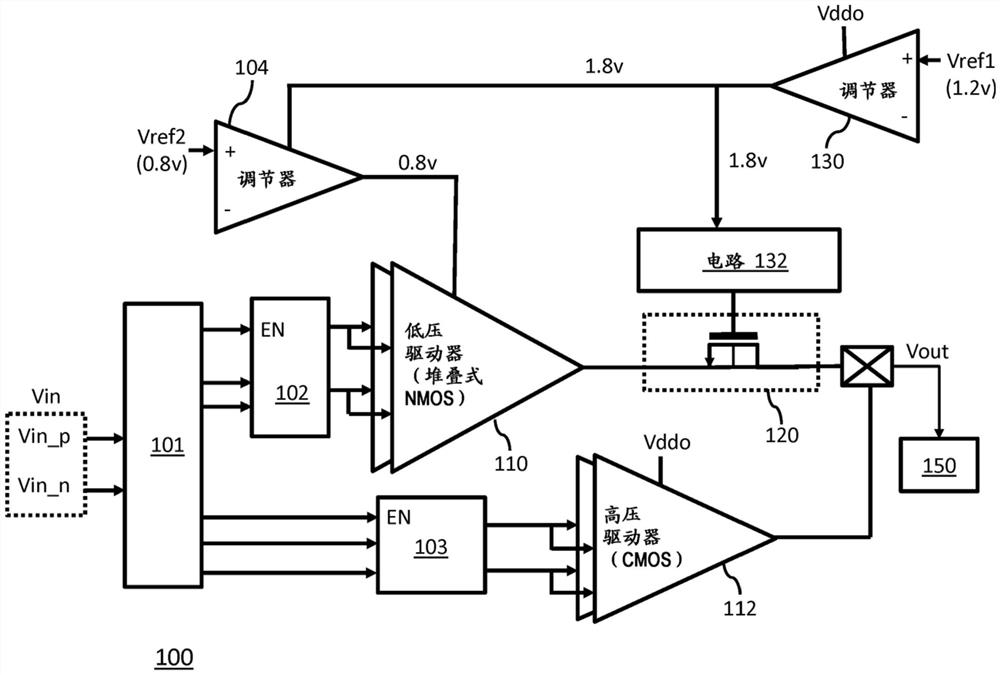

图1是示出在一个实施例中的可以实现具有高压保护和阻抗控制的多驱动器架构的示例装置的图;

图2是示出在一个实施例中的可以实现具有高压保护和阻抗控制的多驱动器架构的另一示例装置的图;

图3是示出在一个实施例中的可以实现具有高压保护和阻抗控制的多驱动器架构的另一示例装置300的图;

图4A是示出在一个实施例中的具有高压保护和阻抗控制的多驱动器架构的示例实现的图;

图4B是示出在一个实施例中的具有高压保护和阻抗控制的多驱动器架构的另一示例实现的图;

图5A是示出在一个实施例中的具有高压保护和阻抗控制的多驱动器架构的另一示例实现的图;以及

图5B是示出在一个实施例中的具有高压保护和阻抗控制的多驱动器架构的另一示例实现的图。

具体实施方式

在以下描述中,阐述了很多具体细节,诸如特定结构、组件、材料、尺寸、处理步骤和技术,以便提供对本申请的各种实施例的理解。然而,本领域普通技术人员将理解,可以在没有这些具体细节的情况下实践本申请的各种实施例。在其他情况下,未详细描述众所周知的结构或处理步骤以避免混淆本申请。

在一方面,差分输出驱动器可以被实现为通过共模电压的测量来调节的幅度调节电压源。差分输出驱动器可以将调节后的电压输出到另一电路或组件以控制或驱动该电路或组件。在一方面,阻抗匹配可以防止电流由于阻抗差异而回流到驱动器中。例如,端接电阻器(例如,在差分输出驱动器外部)可以连接在差分输出驱动器的差分输出(例如,真实输出和互补输出)之间以执行阻抗匹配。在一方面,可以测量端接电阻器的中心抽头处的电压,并且可以将所测量的电压作为反馈提供给调节器,调节器对输出电压实现幅度调节。用以维持功率与噪声性能之间的折衷的专用输出驱动器的要求,可以通过配置或设计差分输出驱动器以包括用于平衡功率和噪声性能的多种特征来解决。然而,生产差分输出驱动器的成本可能会随着特征数目的增加而增加。由于成本相对较高,一些差分输出驱动器可以被设计或配置为需要相对较低的性能规格。

本文中描述的装置、系统和方法可以解决与专用输出驱动器要求相关的各种问题,诸如跨多种驱动器类型的噪声性能,而与特定范围内(例如,从1.8伏(V)到3.3伏)的供应电压无关。此外,本文中描述的装置、系统和方法可以提供相对较小的占用空间以提高成本,并且可以维持功率与噪声性能之间的折衷。在一个示例中,本文中描述的装置、系统和方法可以允许具有可编程电压电平的多种驱动器类型共存,并且在噪声和信号分布方面提高性能水平,并且可以以更小的占用空间来实现。此外,一个或多个开关(例如,具有相对较厚栅极的N型金属氧化物半导体)可以由阻抗控制逻辑块控制,以跨多个供应电压提供恒定阻抗电平。跨多个供应电压的恒定阻抗电平可以允许差分输出驱动器在没有端接电阻器的情况下运行。端接电阻器的移除可以减少占据电路板的组件的数目,并且可以减少电路板上的占用空间。

图1是示出在一个实施例中的可以实现具有高压保护和阻抗控制的多驱动器架构的示例装置100的图。在一个示例中,装置100可以是被实现为电子设备内的驱动器或缓冲器的集成电路。装置100可以接收输入信号,诸如输入电压Vin,并且将Vin转换为输出信号,诸如输出电压Vout。装置100可以使用输出电压信号Vout来驱动另一电路或组件,诸如电路150。在图1所示的示例中,装置100可以包括电路101、预驱动器电路102、预驱动器电路103、电压调节器104、驱动器110、驱动器112、另一电压调节器130、电路132(“控制逻辑块132”)和开关120。在一个实施例中,电路101、预驱动器电路102、预驱动器电路103、驱动器110和驱动器112可以形成装置100的驱动器电路,并且电压调节器104、电压调节器130、电路132和开关120可以形成装置100的控制块或控制器。装置100的电路101可以接收不同电压信号作为输入,诸如输入电压信号Vin,其中Vin可以是具有真实分量和互补分量(例如,Vin_n和Vin_p)的差分输入。电路101可以包括被配置为选择预驱动器电路102、103中的一者的预驱动器逻辑,并且可以对输入电压信号Vin执行电平移位以将Vin的电压电平带到适合驱动器110或驱动器112的电平。例如,如果Vin被提供给预驱动器电路102和驱动器110,则电路101可以将Vin电平移位到第一电压电平,或者如果Vin被提供给预驱动器电路103和驱动器112,则电路101可以将Vin电平移位到第二电压电平。在一个示例中,第二电压电平可以大于第一电压电平。在一个示例实施例中,第二电压电平可以等效于提供给装置100的供应电压Vddo,其中Vddo可以在1.8V到3.3V之间变化,并且第一电压电平可以是1.8V。

预驱动器电路102、103可以从电路101接收电平移位电压,并且可以以较低面积要求优化跨多个供应电压的噪声性能,诸如分别由驱动器110、112输出的电压信号。驱动器110可以是具有堆叠式N型金属氧化物半导体(NMOS)配置的低压驱动器,并且驱动器110可以被配置为提供具有第一电压电平的电压(例如,由电压调节器104调节后的0.8V)。在一个实施例中,驱动器110可以实现低功率高速电流导引逻辑(LP-HCSL)。注意,使用具有配置为1.8伏的预驱动器电路102的堆叠式NMOS拓扑可以减少对低电压驱动器(例如,驱动器110)的总面积要求。驱动器112可以是具有互补对称金属氧化物半导体(CMOS)配置(例如,具有与NMOS堆叠的p型金属氧化物半导体(PMOS))的高压驱动器,并且驱动器112可以使用供应电压Vddo进行操作。装置100可以被配置为满足特定的工艺、电压和温度变化规范以及改进的电源噪声抑制。

在一个示例中,电压调节器130可以接收参考电压Vref1(例如,1.2V)并且可以将Vref1转换为恒定电压,诸如1.8V。电压调节器130可以向电压调节器104和控制逻辑块132提供恒定电压。电压调节器130可以基于供应电压Vddo进行操作。由电压调节器130输出的恒定电压可以是电压调节器104和控制逻辑块132的供应电压。电压调节器104可以接收参考电压Vref2并且可以将Vref2转换为幅度控制电压(例如,0.8V),该电压调节器104可以被用于控制由驱动器110输出的电压信号的幅度。在一个示例中,参考电压Vref2可以是可编程的并且可以在0.4V到1.0V之间变化。可编程参考电压Vref2可以允许由驱动器110输出的电压信号的电压摆动是可编程的。

在一个示例中,开关120可以包括并联连接的一个或多个开关元件(例如,晶体管,诸如N型金属氧化物半导体场效应晶体管(MOSFET))。开关120之中的每个开关元件可以使开关120的体端子或本体端子连接到开关120的源极端子,以降低开关元件的阈值电压并且提高信号完整性。开关120中的开关元件可以由控制逻辑块132选择性地启用(或接通)或禁用(或断开)。控制逻辑块132可以是控制器或数字控制块,该控制器或数字控制块被配置为输出表示可以用于控制开关120的恒定电压的数字信号。例如,控制逻辑块132可以输出第一数字信号,其表示可以启用开关120中的第一数目的开关元件的第一恒定电压,或者可以输出第二数字信号,其表示可以启用开关120中的第二数目的开关元件的第二恒定电压。开关120中启用的开关元件的数目可以称为开关尺寸。

通过使用电压调节器130向控制逻辑块132提供固定或恒定电压,控制逻辑块132可以通过设置开关120的开关尺寸来设置开关120的开关阻抗。恒定开关阻抗可以跨装置100中的不同组件提供固定或恒定的阻抗电平,或者提供多个供应电压值(例如,Vddo)。由开关120设置的恒定阻抗可以使装置的输出Vout也具有恒定阻抗。在一个示例中,启用的第一数目的开关元件可以提供85ohm的恒定开关阻抗,并且启用的第二数目的开关元件可以提供100ohm的恒定开关阻抗。选择开关尺寸可以调整开关120的内阻,以有效地控制装置100的内阻。例如,随着开关中启用的开关元件的数目减少,开关120的内阻可能增加。开关的内阻可以基于启用的开关元件的数目来调整或增加。开关的内阻可以增加到特定水平,使得装置100可以生成支持特定阻抗电平的源极端接的差分输出(例如,Vout)。具有恒定阻抗的输出电压Vout可以允许装置100驱动器电路150,而无需在装置100的差分输出线之间连接外部端接电阻器。在一个实施例中,输出电压Vout可以具有由开关尺寸设置的固定阻抗(例如,85ohms或100ohms),使得无需连接任何端接电阻器以进行阻抗匹配。在一个实施例中,可以通过开关120的开关尺寸来设置两个以上的阻抗电平。在一个实施例中,响应于装置100在时钟发生器的输出驱动器电路中实现,Vout可以是差分时钟信号。

在一个示例中,开关120可以被禁用或断开(例如,所有开关元件被禁用),而驱动器112可以被启用并且驱动器110可以被禁用。响应于启用驱动器112和禁用驱动器110,装置100可以在正常条件下操作(例如,不使用开关来设置恒定阻抗)。响应于开关120被启用或接通(例如,使一个或多个开关元件被启用),驱动器110可以被启用并且驱动器112可以被禁用。因此,驱动器110或112中的任一个可以被选择作为驱动器路径以将输入电压Vin作为输出电压Vout缓冲或传递到另一设备。在一个实施例中,电路101可以被配置为向预驱动器电路102、103中的一者的使能引脚(EN)发送使能信号,以启用预驱动器电路102、103中的一者。然后禁用没有接收到使能信号的预驱动器电路102、103中的预驱动器。在示例实施例中,开关120中的开关元件可以是厚栅NMOS保护开关,该开关可以允许集成多种输入输出(IO)驱动器类型(例如,诸如驱动器110等低压驱动器和诸如驱动器112等高压驱动器)的可行性。如果开关120中的开关元件的栅极相对较薄,则诸如3.3V等相对较高的电压可能会破坏开关元件。通过使用较厚的栅极NMOS来实现开关120,可以消除附加的高压保护开关要求,从而节省电路板空间并且降低设计复杂性。在一个示例中,开关120中的开关元件的栅极的厚度可以是可以耐受至少3.3V的电压的厚度。

图2是示出在一个实施例中的可以实现具有高压保护和阻抗控制的多驱动器架构的另一示例装置200的图。在图2所示的示例中,装置200可以是包括N个差分输出驱动器(诸如208-1、208-2、……、208-N)的设备。装置200的差分输出驱动器可以输出差分输出电压信号,诸如来自差分输出驱动器208-1的Vout-1,其中Vout-1可以包括真实分量Vout-1a和互补分量Vout-1b。在一个示例中,N可以是12,使得装置200可以具有12个差分输出。在另一示例中,N可以是8,使得装置200可以具有8个差分输出。

装置200还可以包括电路204和多路复用器206。电路204可以包括与装置200的应用相关的组件。例如,如果装置200是时钟发生器,则电路204可以包括振荡器、输出驱动器、存储器设备等。此外,装置200可以包括图2中可能未示出的附加输入和输出引脚或端子。差分输出驱动器208-1、208-2、……、208-N中的每个可以包括装置100。多路复用器206可以被配置为选择差分输出驱动器208-1、208-2、……、208-N中的一个或多个以将电压Vin驱动到Vout。例如,如果多路复用器206选择了差分输出驱动器208-1和208-2,则差分输出驱动器208-1和208-2可以将Vin驱动到Vout。在一个示例中,如果装置200是时钟发生器,则多路复用器206可以被配置为从电路204中的输出分频器中选择一个通道以将时钟信号发送到差分输出驱动器208-1、208-2、……、208-N中的一个,其中可以启用所有驱动器以从不同通道输出所需要的时钟信号。在一个实施例中,驱动器208-1、208-2、……、208-N中的每个可以连接到其自己的供应电压(例如,图1中的Vddo)。此外,驱动器208-1、208-2、……、208-N中的每个可以包括相应的一组电压调节器。

图3是示出在一个实施例中的可以实现具有高压保护和阻抗控制的多驱动器架构的另一示例装置300的图。在一个示例中,装置300可以是可编程时钟发生器,该可编程时钟发生器用于诸如具有CPU超频的高端桌面(HEDT)等应用或具有动态频率要求的消费者应用。装置300可以包括电路302。参考图2中的示例,电路302可以是图2所示的电路204。图1所示的装置100的副本可以在连接到装置300的差分输出的输出驱动器208-1、……、208-N中的每个内。在一个实施例中,图3所示的装置300具有十二个差分输出,范围从差分输出(OUT0、OUT0b)到(OUT11、OUT11b)。在另一实施例中,装置300可以包括不同数目的差分输出,诸如八个差分输出。

差分输出(OUT0、OUT0b)到(OUT11、OUT11b)中的每个可以用于驱动对个体应用的输入。例如,装置300的差分输出可以是用于驱动对各种应用的输入的时钟信号(例如,如果装置300是时钟发生器)。差分输出(OUT0、OUT0b)可以驱动对第一外围组件互连快速(PCIe)应用的输入,并且差分输出(OUT3、OUT3b)可以驱动对第二PCIe应用的输入。通过在差分输出驱动器208-1、……、208-N中的每个中实现装置100,装置300可以生成具有固定输出阻抗(例如,85ohm或100ohm)的不同组的差分输出。差分输出的固定输出阻抗可以允许差分输出直接驱动对不同应用的输入(例如,无需在差分输出之间连接外部端接电阻器)。

图4A和图4B是示出在一个实施例中的具有高压保护和阻抗控制的多驱动器架构的示例实现的图。图4A示出了当驱动器112被启用并且驱动器110被禁用时图1中的装置100的实现。在图4A中,启用的驱动器112可以经由直流(DC)耦合将Vout输出到另一设备400。在图4B中,启用的驱动器112可以经由交流(AC)耦合将Vout输出到设备400。

在一个示例中,驱动器112可以处理相对较高的电压输入(例如,3.3V),并且Vout的幅度可能需要从全摆幅降低到至少一半摆幅,以防止信号干扰电源轨并且减少内部噪声。例如,如图4A和图4B所示,驱动器112可以实现为高速3.3V CMOS驱动器。在图4A和图4B所示的配置中,驱动器的输出阻抗(Ro)和串联电阻(Rs)的总和等于传输线阻抗Zo。此外,晶体输入处的匹配端接(如果装置100在时钟发生器中实现)将使信号衰减一半。这可以通过以下两种方式中的一种来完成。首先,并联的R1和R2应当等于传输线阻抗。对于大多数50ohm应用,R1和R2可以是100ohm。备选地,这也可以通过移除R1并且将R2改变为50ohm来实现。在一个示例中,可以增加电阻器的值以减少针对较慢和较弱CMOS驱动器的负载。

图5A和图5B是示出在一个实施例中的具有高压保护和阻抗控制的多驱动器架构的示例实现的图。图5A和图5B示出了当驱动器110被启用并且驱动器112被禁用时图1中的装置100的实现。在图5A中,启用的驱动器110可以经由直流(DC)耦合将Vout输出到另一设备500。在图5B中,启用的驱动器110可以经由AC耦合将Vout输出到设备500。在图5A所示的示例中,驱动器110可以实现低功率高速电流控制逻辑(LP-HCSL)差分协议,并且图2所示的装置200可以是时钟发生器(例如,图3中的装置300),并且设备500可以是基于由Vout驱动的时钟信号进行操作的设备。图5A所示的配置可以支持呈现例如85或100ohm的恒定差分输出阻抗的源端接。注意,在图5A所示的示例中,由于恒定的差分输出阻抗,在驱动器110的不同输出线(例如,50ohm迹线)之间没有连接端接电阻器。

图5B示出了一种配置,其中无论由图1所示的驱动器110实现的协议如何,AC耦合都可以用于驱动另一设备或时钟发生器的时钟输入引脚。图5B所示的配置是在100ohm差分传输线环境下。在一个示例中,驱动器110可以实现用于AC耦合的LP-HCSL协议,并且为被驱动的接收器选择适当的电压摆幅。注意,驱动器110与AC耦合电容器CS之间不需要端接电阻器(例如,差分输出线或两个50ohm迹线之间没有连接端接电阻器)。AC耦合电容器的接收器侧的电阻器应当被选择,以便为特定接收器提供适当的电压偏置。在一个示例中,跨差分对(位于接收器附近)的100ohm电阻器可以衰减或防止接收器处可能破坏时钟信号完整性的反射。

本文中使用的术语仅出于描述特定实施例的目的,并不旨在限制本发明。如本文中使用的,单数形式“一个(a)”、“一个(an)”和“该(the)”旨在也包括复数形式,除非上下文另有明确指示。将进一步理解,当在本说明书中使用时,术语“包括(comprises)”和/或“包括(comprising)”指定了所述特征、整体、步骤、操作、元素和/或组件的存在,但不排除一个或多个其他特征、整体、步骤、操作、元素、组件和/或其组的存在或添加。

以下权利要求中的所有装置或步骤加功能元件(如果有的话)的对应结构、材料、动作和等同物旨在包括用于与其他要求保护的元素相结合执行功能的任何结构、材料或动作,正如特别要求保护的那样。本发明的描述是为了说明和描述的目的而呈现的,但并不旨在穷举或限制于所公开形式的本发明。在不背离本发明的范围和精神的情况下,很多修改和变化对于本领域普通技术人员将是很清楚的。选择和描述实施例是为了最好地解释本发明的原理和实际应用,并且使得本领域其他普通技术人员能够理解具有适合于预期的特定用途的各种修改的本发明的各种实施例。

- 基于级联型多电平变换器的高压阻抗测量装置及控制方法

- 监测车辆的功能性的方法、用于车辆的驱动器的控制部、具有这样的控制部的驱动器以及具有这样的驱动器的车辆

- 具有阻抗控制的驱动器