具有时钟信号分发的芯粒封装芯片

文献发布时间:2023-06-19 19:35:22

技术领域

本发明实施例涉及集成电路封装技术,尤其涉及一种具有时钟信号分发的芯粒封装芯片。

背景技术

随着芯片技术的不断发展,芯片结构的复杂度随之增高。目前采用Chiplet技术对多芯粒进行封装。芯粒工作需要参考时钟的支持。封装内的多个芯粒通过高速片间互联接口互联,高速片间互联接口进行数据传输时需要低抖动的同源参考时钟。

目前的参考时钟在印制电路板(Printed Circuit Board,PCB)基板或封装基板上进行路由绕线,分别连接到每个芯粒。然而在绕线过程中存在排线资源挤兑以及阻抗干扰等问题。如何在减少绕线的同时提高时钟信号质量成为亟待解决的问题。

发明内容

本发明提供一种具有时钟信号分发的芯粒封装芯片,以实现在减少绕线的同时提高时钟信号质量,不仅能够降低绕线成本而且能够提高时钟信号质量。

第一方面,本发明实施例提供了一种具有时钟信号分发的芯粒封装芯片,其特征在于,包括封装基板;

所述封装基板位于PCB基板上;所述PCB基板包括第一时钟源;

所述封装基板上封装有多个芯粒;相邻的两个芯粒通过片间互联接口连接;

每个芯粒包括输入时钟缓冲器、输出时钟缓冲器和至少一个片间互联接口;所述输入时钟缓冲器将时钟信号输出至所在芯粒内的每个片间互联接口和所述输出时钟缓冲器;

所述多个芯粒包括一个第一芯粒和至少一个第二芯粒;

所述第一时钟源与所述第一芯粒的输入时钟缓冲器连接;所述第二芯粒的输入时钟缓冲器与相邻芯粒的输出时钟缓冲器连接,所述相邻芯粒为第一芯粒或第二芯粒;

所述第一芯粒和所述第二芯粒的输出时钟缓冲器与相邻的第二芯粒的输入时钟缓冲器连接。

在上述方案的基础上,所述第一芯粒包括一个输出时钟缓冲器,第二芯粒包括一个输出时钟缓冲器,所述第二芯粒有多个;

所述时钟信号以所述第一芯粒为起点,按照预设顺序在多个第二芯粒上单向串行传递。

在上述方案的基础上,所述第一芯粒包括多个输出时钟缓冲器,所述第二芯粒包括一个或多个输出时钟缓冲器,所述第二芯粒有多个;

所述时钟信号以所述第一芯粒为起点,按照预设顺序在多个第二芯粒上多路并行传递。

在上述方案的基础上,位于传递末端的第二芯粒的输出时钟缓冲器的输出引脚悬空或取消。

在上述方案的基础上,所述PCB基板还包括第二时钟源;所述多个芯粒包括一个第三芯粒和至少一个第四芯粒;

所述第二时钟源与所述第三芯粒的输入时钟缓冲器连接;所述第四芯粒的输入时钟缓冲器与相邻芯粒的输出时钟缓冲器连接,所述相邻芯粒为第三芯粒或第四芯粒;

所述第三芯粒和所述第四芯粒的输出时钟缓冲器与相邻的第四芯粒的输入时钟缓冲器连接;

所述第三芯粒和/或所述第四芯粒通过片间互联接口与所述第一芯粒和/或所述第二芯粒互联。

在上述方案的基础上,所述片间互联接口通过弹性缓存方式进行第一时钟源与第二时钟源的时钟信号统一。

在上述方案的基础上,所述芯粒还包括至少一个中继缓冲器;

所述输入时钟缓冲器通过所述至少一个中继时钟缓冲器将时钟信号分别输出至所在芯粒内的片间互联接口。

在上述方案的基础上,多个芯粒封装于中介层,所述中介层封装于封装基板;或者,所述多个芯粒直接封装于所述封装基板。

在上述方案的基础上,所述输入时钟缓冲器的输入为差分时钟信号,所述输入时钟缓冲器的输出为单端或差分信号,所述输出时钟缓冲器的输入为单端或差分信号,所述输出时钟缓冲器的输出为差分信号;或者,所述输入时钟缓冲器的输入和输出为单端时钟信号,输出时钟缓冲器的输出和输入为单端时钟信号。

在上述方案的基础上,所述多个芯粒同构或异构。

本发明提供的具有时钟信号分发的芯粒封装芯片,第一时钟源的时钟信号通过第一芯粒的输入时钟缓冲器输入至第一芯粒,通过第一芯粒内部的时钟缓冲器的传导到达第一芯粒的输出时钟缓冲器。由第一芯粒的输出时钟缓冲器输出至相邻的第二芯粒的输入时钟缓冲器,实现在芯粒内部完成时钟信号的传递,无需在封装基板或PCB基板上为每个芯粒设置时钟信号,第一时钟源的时钟信号只需输入至第一芯粒,即可实现在第一芯粒和至少一个第二芯粒之间完成第一时钟源的传递。由于在芯粒内部传递时钟信号,因此时钟信号不会发生组抗干扰,且无需在封装基板或PCB基板上设置多条时钟信号的布线,进而解决排线资源挤兑的问题,实现在减少绕线的同时提高时钟信号质量的效果。

附图说明

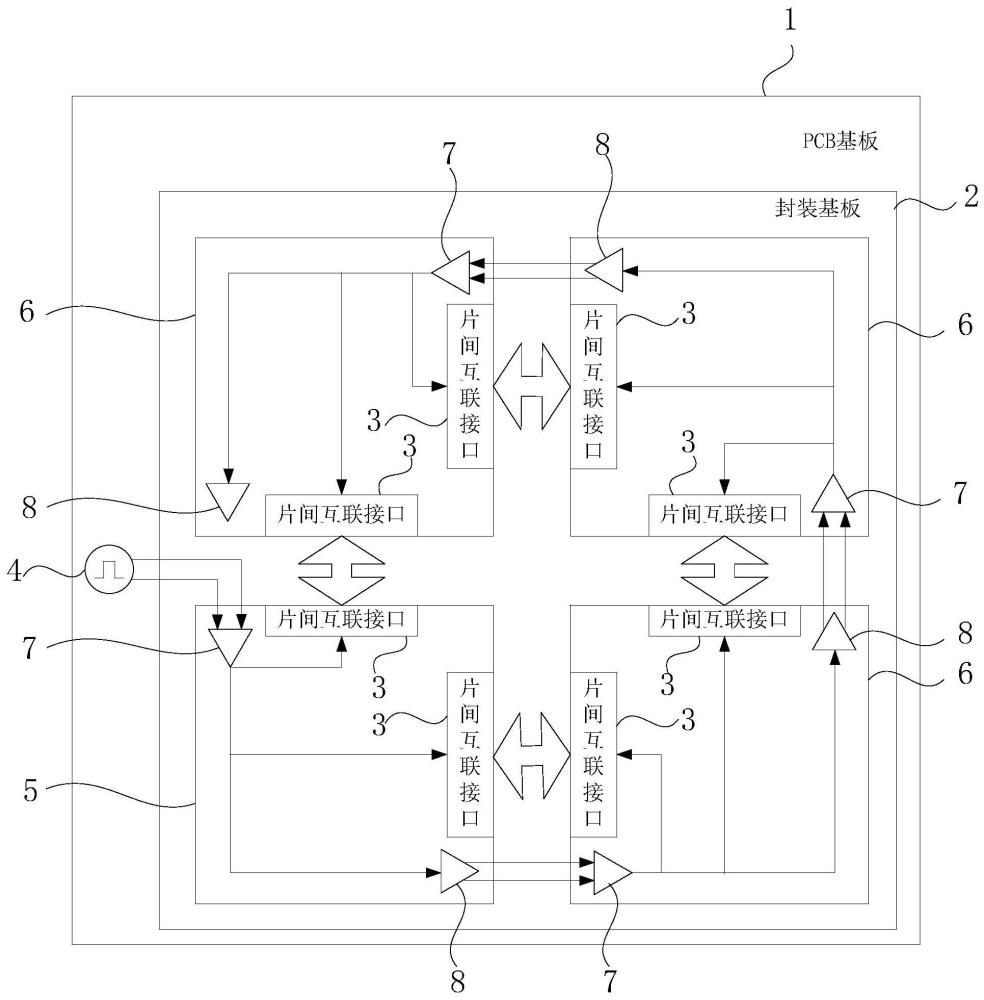

图1是本发明实施例提供的具有时钟信号分发的芯粒封装芯片的结构示意图一;

图2是本发明实施例提供的具有时钟信号分发的芯粒封装芯片的结构示意图二;

图3是本发明实施例提供的具有时钟信号分发的芯粒封装芯片的结构示意图三;

图4是本发明实施例提供的具有时钟信号分发的芯粒封装芯片的结构示意图四;

图5是本发明实施例提供的具有时钟信号分发的芯粒封装芯片的结构示意图五;

图6是本发明实施例提供的具有时钟信号分发的芯粒封装芯片的结构示意图六;

图7是本发明实施例提供的具有时钟信号分发的芯粒封装芯片的结构示意图七;

图8是本发明实施例提供的具有时钟信号分发的芯粒封装芯片的结构示意图八。

1-封装基板,2-PCB基板,3-片间互联接口,4-第一时钟源,5-第一芯粒,6-第二芯粒,7-输入时钟缓冲器,8-输出时钟缓冲器,9-第二时钟源,10-第三芯粒,11-第四芯粒。

具体实施方式

下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

图1为本发明实施例提供的具有时钟信号分发的芯粒封装芯片的结构示意图一,包括封装基板1;

所述封装基板1位于PCB基板2上;所述PCB基板2包括第一时钟源4;

所述封装基板1上封装有多个芯粒;相邻的两个芯粒通过片间互联接口3连接;

每个芯粒包括输入时钟缓冲器7、输出时钟缓冲器8和至少一个片间互联接口3;所述输入时钟缓冲器7将时钟信号输出至所在芯粒内的每个片间互联接口3和所述输出时钟缓冲器8;

所述多个芯粒包括一个第一芯粒5和至少一个第二芯粒6;

所述第一时钟源4与所述第一芯粒5的输入时钟缓冲器7连接;所述第二芯粒6的输入时钟缓冲器7与相邻芯粒的输出时钟缓冲器8连接,所述相邻芯粒为第一芯粒5或第二芯粒6;

所述第一芯粒5和所述第二芯粒6的输出时钟缓冲器8与相邻的第二芯粒6的输入时钟缓冲器7连接。

作为一种示例,如图1所示,包含一个第一芯粒5和三个第二芯粒6的封装结构。其中,本发明实施例中的任意一个芯粒,包括输入时钟缓冲器7、输出时钟缓冲器8和至少一个片间互联接口3,其中任意一个芯粒可以为第一芯粒5或第二芯粒6。输入时钟缓冲器7的输出端分别连接到第一芯粒5上的各个片间互联接口3。片间互联接口3的数量可以根据设计需求而定,可以为一个或多个。

第一芯粒5的输入时钟缓冲器7的输入端与第一时钟源4连接。输入时钟缓冲器7的输出端可以直接与第一芯粒5的输出时钟缓冲器8连接,也可以根据设计需求增加中继时钟缓冲器以便维持时钟信号强度。相应的,芯粒还包括至少一个中继缓冲器;所述输入时钟缓冲器7通过所述至少一个中继时钟缓冲器将时钟信号分别输出至所在芯粒内的片间互联接口3。

可选的,图2是本发明实施例提供的具有时钟信号分发的芯粒封装芯片的结构示意图二,如图2所示,具有时钟信号分发的芯粒封装芯片可以具有一个第一芯粒5和一个第二芯粒6。第一芯粒5设有一个片间互联接口3,第二芯粒6设有一个片间互联接口3。第一芯粒5的输入时钟缓冲器7的输入端与第一时钟源4连接。第一芯粒5的输入时钟缓冲器7的输出端与第一芯粒5的片间互联接口3连接,第一芯粒5的片间互联接口3与第二芯粒6的片间互联接口3连接。第一芯粒5的输入时钟缓冲器7的输出端与第一芯粒5的输出时钟缓冲器8的输入端连接,第一芯粒5的输出时钟缓冲器8的输出端与第二芯粒6的输入时钟缓冲器7的输入端连接。第二芯粒6的输入时钟缓冲器7的输出端与第二芯粒6的片间互联接口3连接。可选的,第二芯粒6的输入时钟缓冲器7的输出端的其他的输出引脚悬空或取消。

本发明实施例提供的具有时钟信号分发的芯粒封装芯片,第一时钟源的时钟信号通过第一芯粒的输入时钟缓冲器输入至第一芯粒,通过第一芯粒内部的时钟缓冲器的传导到达第一芯粒的输出时钟缓冲器。由第一芯粒的输出时钟缓冲器输出至相邻的第二芯粒的输入时钟缓冲器,实现在芯粒内部完成时钟信号的传递,无需在封装基板或PCB基板上为每个芯粒设置时钟信号,第一时钟源的时钟信号只需输入至第一芯粒,即可实现在第一芯粒和至少一个第二芯粒之间完成第一时钟源的传递。由于在芯粒内部传递时钟信号,因此时钟信号不会发生组抗干扰,且无需在封装基板或PCB基板上设置多条时钟信号的布线,进而解决排线资源挤兑的问题,实现在减少绕线的同时提高时钟信号质量的效果。

在一种实现方式中,所述第一芯粒5包括一个输出时钟缓冲器8,第二芯粒6包括一个输出时钟缓冲器8,所述第二芯粒6有多个;所述时钟信号以所述第一芯粒5为起点,按照预设顺序在多个第二芯粒6上单向串行传递。

第二芯粒6的数量可以根据设计需求进行确定。通常多个第二芯粒6与第一芯粒5组成N*N或者M*N的矩阵。例如,如图3所示,三个第二芯粒6与第一芯粒5组成2*2的芯粒矩阵。又例如,如图4所示,八个第二芯粒6与第一芯粒5组成3*3的芯粒矩阵。还可以由十五个第二芯粒6与第一芯粒5组成4*4的芯粒矩阵,以此类推,由一个第一芯粒5接入第一时钟源4的时钟信号,然后由第一芯粒5将时钟信号传递至相邻的第二芯粒6,再由该第二芯粒6传递给相邻的其他第二芯粒6。

在图3中,第一芯粒5为芯粒a、第二芯粒6包括芯粒b、芯粒c和芯粒d。芯粒a、芯粒b、芯粒c和芯粒d按逆时针依次排列,组成2*2的芯粒矩阵。相邻的两个芯粒之间通过片间互联接口3连接。每个芯粒包括一个输入时钟缓冲器7和一个输出时钟缓冲器8。每个芯粒的输入时钟缓冲器7的输出端分别与该芯粒的片间互联接口3以及输出时钟缓冲器8连接。芯粒a的输入时钟缓冲器7的输入端与第一时钟源4连接。芯粒a的输出时钟缓冲器8的输出端与芯粒b的输入时钟缓冲器7的输入端连接。芯粒b的输出时钟缓冲器8的输出端与芯粒c的输入时钟缓冲器7的输入端连接。芯粒c的输出时钟缓冲器8的输出端与芯粒d的输入时钟缓冲器7的输入端连接。通过时钟缓冲器的传导,时钟信号依次经过芯粒a、芯粒b、芯粒c和芯粒b,实现逆时针的串行传递。

需要说明的是,串行传递的传递方向并不限定与顺时针或逆时针。例如当设置有3*3、4*4等多层芯粒矩阵时,只要是以串行方式将全部芯粒连接起来的连接方式均可。

如图4中,第一芯粒5为芯粒a、第二芯粒6包括芯粒b、芯粒c、芯粒d、芯粒e、芯粒f、芯粒g、芯粒h和芯粒i。相邻的两个芯粒之间通过片间互联接口3连接。每个芯粒包括一个输入时钟缓冲器7和一个输出时钟缓冲器8。每个芯粒的输入时钟缓冲器7的输出端分别与该芯粒的片间互联接口3以及输出时钟缓冲器8连接。芯粒a的输入时钟缓冲器7的输入端与第一时钟源4连接。芯粒a的输出时钟缓冲器8的输出端与芯粒b的输入时钟缓冲器7的输入端连接。芯粒b的输出时钟缓冲器8的输出端与芯粒c的输入时钟缓冲器7的输入端连接。芯粒c的输出时钟缓冲器8的输出端与芯粒d的输入时钟缓冲器7的输入端连接。芯粒d的输出时钟缓冲器8的输出端与芯粒e的输入时钟缓冲器7的输入端连接。芯粒e的输出时钟缓冲器8的输出端与芯粒f的输入时钟缓冲器7的输入端连接。芯粒f的输出时钟缓冲器8的输出端与芯粒g的输入时钟缓冲器7的输入端连接。芯粒g的输出时钟缓冲器8的输出端与芯粒h的输入时钟缓冲器7的输入端连接。芯粒h的输出时钟缓冲器8的输出端与芯粒i的输入时钟缓冲器7的输入端连接。通过时钟缓冲器的传导,时钟信号依次经过芯粒a、芯粒b、芯粒c、芯粒d、芯粒e、芯粒f、芯粒g、芯粒h和芯粒i,实现预设顺序的串行传递。

上述实施方式每个芯粒上设置一个输入时钟缓冲器7和一个输出时钟缓冲器8,将时钟缓冲器的数量控制在最低,进而降低成本。

在另一种实现方式中,第一芯粒5包括多个输出时钟缓冲器8,所述第二芯粒6包括一个或多个输出时钟缓冲器8,所述第二芯粒6有多个;所述时钟信号以所述第一芯粒5为起点,按照预设顺序在多个第二芯粒6上多路并行传递。

随着封装的芯粒数量越来越多,单向串行传递时钟信号的时间随之增加。除了在芯粒之间进行单向串行传递,本发明实施例还可以在多个第二芯粒6之间进行多路并行传递,以便提高时钟信号的传递时效。

第二芯粒6的数量可以根据设计需求进行确定。通常多个第二芯粒6与第一芯粒5组成N*N或M*N的矩阵。例如,如图5所示,三个第二芯粒6与第一芯粒5组成2*2的芯粒矩阵。又例如,如图6所示,八个第二芯粒6与第一芯粒5组成3*3的芯粒矩阵。还可以由十五个第二芯粒6与第一芯粒5组成4*4的芯粒矩阵,以此类推,由一个第一芯粒5接入第一时钟源4的时钟信号,然后由第一芯粒5将时钟信号传递至相邻的多个第二芯粒6,再由该第二芯粒6传递给相邻的其他第二芯粒6。

在图5中,第一芯粒5为芯粒a、第二芯粒6包括芯粒b、芯粒c和芯粒d。芯粒a、芯粒b、芯粒c和芯粒d按逆时针依次排列,组成2*2的芯粒矩阵。相邻的两个芯粒之间通过片间互联接口3连接。每个芯粒的输入时钟缓冲器7的输出端分别与该芯粒的片间互联接口3以及输出时钟缓冲器8连接。芯粒a的输入时钟缓冲器7的输入端与第一时钟源4连接。芯粒a的输出时钟缓冲器8A的输出端与芯粒b的输入时钟缓冲器7的输入端连接。芯粒a的输出时钟缓冲器8B的输出端与芯粒d的输入时钟缓冲器7的输入端连接。芯粒b的输出时钟缓冲器8的输出端与芯粒c的输入时钟缓冲器7的输入端连接。通过时钟缓冲器的传导,时钟信号依次经过芯粒a、芯粒d组成的路线一和芯粒a、芯粒b和芯粒c组成的路线二完成传递,路线一和路线二为两条并行传递路线。进一步的,为了节约成本,在芯粒c和芯粒d作为路径末端,取消设置输出时钟缓冲器。

如图6中,第一芯粒5为芯粒a、第二芯粒6包括芯粒b、芯粒c、芯粒d、芯粒e、芯粒f、芯粒g、芯粒h和芯粒i。相邻的两个芯粒之间通过片间互联接口3连接。芯粒的输入时钟缓冲器7的输出端分别与该芯粒的片间互联接口3以及输出时钟缓冲器8连接。

芯粒f的输入时钟缓冲器7的输入端与第一时钟源4连接。芯粒f的输出时钟缓冲器8G的输出端与芯粒a的输入时钟缓冲器7的输入端连接;芯粒f的输出时钟缓冲器8H的输出端与芯粒e的输入时钟缓冲器7的输入端连接;芯粒f的输出时钟缓冲器8I的输出端与芯粒g的输入时钟缓冲器7的输入端连接。

芯粒a的输出时钟缓冲器8的输出端与芯粒b的输入时钟缓冲器7的输入端连接。芯粒e的输出时钟缓冲器8的输出端与芯粒d的输入时钟缓冲器7的输入端连接。芯粒g的输出时钟缓冲器8的输出端与芯粒h的输入时钟缓冲器7的输入端连接。芯粒h的输出时钟缓冲器8的输出端与芯粒i的输入时钟缓冲器7的输入端连接。

通过时钟缓冲器的传导,时钟信号依次经过芯粒f、芯粒a、芯粒b、芯粒c组成的路线一,芯粒f、芯粒e、芯粒d组成的路线二,芯粒f、芯粒g、芯粒h、芯粒i组成的路线三完成传递。路线一、路线二和路线三为三条并行传递路线,实现预设顺序的并行传递。

需要说明的是,并行传递可以为从第一芯粒5分散处的多条并行路线,也可以是放射形等方式进行多路传递。示例性的,如图7所示,第一芯粒5为芯粒a、第二芯粒6包括芯粒b、芯粒c、芯粒d、芯粒e、芯粒f、芯粒g、芯粒h和芯粒i。相邻的两个芯粒之间通过片间互联接口3连接。每个芯粒的输入时钟缓冲器7的输出端分别与该芯粒的片间互联接口3以及输出时钟缓冲器8连接。芯粒a的输入时钟缓冲器7的输入端与第一时钟源4连接。芯粒a的输出时钟缓冲器8A的输出端与芯粒b的输入时钟缓冲器7的输入端连接;芯粒a的输出时钟缓冲器8B的输出端与芯粒f的输入时钟缓冲器7的输入端连接。芯粒f的输出时钟缓冲器8的输出端与芯粒g的输入时钟缓冲器7的输入端连接。芯粒b的输出时钟缓冲器8C的输出端与芯粒c的输入时钟缓冲器7的输入端连接;芯粒b的输出时钟缓冲器8D的输出端与芯粒e的输入时钟缓冲器7的输入端连接。芯粒e的输出时钟缓冲器8E的输出端与芯粒d的输入时钟缓冲器7的输入端连接;芯粒e的输出时钟缓冲器8F的输出端与芯粒h的输入时钟缓冲器7的输入端连接。芯粒h的输出时钟缓冲器8的输出端与芯粒i的输入时钟缓冲器7的输入端连接。

可见,芯粒之间的时钟信号传递可以为串行、并行或者串行与并行结合的方式。可以根据设计成本和时钟传导时效等设计需求对时钟信号的传递路线进行配置。

在上述实施方式的基础上,位于传递末端的第二芯粒6的输出时钟缓冲器8的输出引脚悬空或取消。

位于传递路径末端的第二芯粒6的输出时钟缓冲器8可以保留也可取消。为了方便设计各芯粒采用同构方式,则传递末端的第二芯粒6存在输出时钟缓冲器8,该输出时钟缓冲器8为时钟信号的传递末端,输出时钟缓冲器8的输出引脚悬空。进而提高芯粒引脚的可靠性。

在上述实施方式的基础上,所述PCB基板2还包括第二时钟源9;所述多个芯粒包括一个第三芯粒10和至少一个第四芯粒11;

所述第二时钟源9与所述第三芯粒10的输入时钟缓冲器7连接;所述第四芯粒11的输入时钟缓冲器7与相邻芯粒的输出时钟缓冲器8连接,所述相邻芯粒为第三芯粒10或第四芯粒11;

所述第三芯粒10和所述第四芯粒11的输出时钟缓冲器8与相邻的第四芯粒11的输入时钟缓冲器7连接;

所述第三芯粒10和/或所述第四芯粒11通过片间互联接口3与所述第一芯粒5和/或所述第二芯粒6互联。

在一些使用场景中,芯粒的封装规模较大,此时可能需要向芯粒矩阵接入第二时钟源9。第二时钟源9为第一时钟源4以外的时钟源,第二时钟源9由PCB基本提供。第二时钟源9的数量可以有多个。

第三芯粒10和第四芯粒11的设置方式与第一芯粒5和第二芯粒6的设置方式相同。第三芯粒10在时钟信号传导中的作用与第一芯粒5相同,用于与时钟源连接。第三芯粒10与第二时钟源9连接。第四芯粒11在适中芯号传导中的作用与第二芯粒6相同,用于在封装内部进行时钟信号的传导。

第三芯粒10和第四芯粒11根据设计需求设计排布位置,第三芯粒10和第四芯粒11呈N*N或者M*N的矩阵。

第三芯粒10和第四芯粒11与第一芯粒5和第二芯粒6一同组成芯粒矩阵。第三芯粒10和第四芯粒11为一组芯粒,第一芯粒5和第二芯粒6为另一组芯粒,两组芯粒之间通过相邻的芯粒上设置的片间互联接口3进行数据交互。

示例性的,如图8所示,第一组芯粒包括第一芯粒5和第二芯粒6,其中,芯粒a作为第一芯粒5,芯粒b、芯粒c、芯粒d、芯粒e、芯粒f、芯粒g、芯粒h作为第二芯粒6。第二组芯粒包括第三芯粒10和第四芯粒11,其中,芯粒p作为第三芯粒10,芯粒i、芯粒j、芯粒k、芯粒l、芯粒m、芯粒n、芯粒o作为第四芯粒11。

第一组芯粒和第二组芯粒共同组成4*4的芯粒矩阵。

第一芯粒5组与第二芯粒6组交汇的芯粒分别为芯粒e、芯粒i、芯粒f、芯粒j、芯粒g、芯粒k、芯粒h以及芯粒l。其中,芯粒e与芯粒i相邻,芯粒f与芯粒j相邻,芯粒g与芯粒k相邻,芯粒h与芯粒l相邻。第一芯粒5内部实现和第二芯粒6组内部均能够实现同源时钟的时钟信号传导。

需要说明的是,第一芯粒5组与第二芯粒6组交汇的芯粒不仅可以包括第二芯粒6和第四芯粒11,还可以第一芯粒5和第三芯粒10。

如果第一时钟源4与第二时钟源9为同源时钟,则第一芯粒5组与第二芯粒6组内传递的时钟信号同源。

如果第一时钟源4与第二时钟源9不是同源时钟,则第一芯粒5组与第二芯粒6组交汇的芯粒采用的片间互联接口3通过弹性缓存方式进行第一时钟源4与第二时钟源9的时钟信号统一。通过弹性缓存方式将第一时钟源4的时钟信号与第二时钟源9的时钟信号进行统一,使得第一芯粒5组与第二洗粒组中的时钟同源。

在片间互联接口3上应用感性缓存方式,能够实现将非同源的时钟信号进行统一,进而能够在芯粒封装中纳入多个非同源时钟。

在上述实施方式的基础上,多个芯粒封装于中介层,所述中介层封装于封装基板1;或者,所述多个芯粒直接封装于所述封装基板1。

通常PCB基板2上设有封装基板1,封装基板1通过引脚与芯粒连接,多个芯粒直接封装于所述封装基板1,实现实现PCB基板2、封装基板1、芯粒的封装结构。在另一种实现方式中,在封装基板1上还可以设置中阶层,中阶层通过引脚与芯粒连接,实现PCB基板2、封装基板1、中阶层、芯粒的封装结构。

可选的,所述输入时钟缓冲器7的输入为差分时钟信号,所述输入时钟缓冲器7的输出为单端或差分信号,所述输出时钟缓冲器8的输入为单端或差分信号,所述输出时钟缓冲器8的输出为差分信号。

输入时钟缓冲器7的输入为差分时钟信号,输入时钟缓冲器7的输出可以为单端信号也可以为差分信号。在芯粒内部,可以根据设计需求设置输入时钟缓冲器7的输出。若存在中继时钟缓冲器,则中继时钟缓冲器在保留信号类型不变的可变的同时,对时钟信号进行传递。假设时钟信号类型不变,则输出时钟缓冲器8的输入与输入时钟缓冲器7的输出的信号类型一致,时钟信号类型为单端信号或差分信号。输出时钟缓冲器8的输出为差分信号,以便相邻芯粒的输入时钟缓冲器7接收到的输入为差分时钟信号。

可选的,所述输入时钟缓冲器7的输入和输出为单端时钟信号,输出时钟缓冲器8的输出和输入为单端时钟信号。

如果输入时钟缓冲器7的输入为单端时钟信号,则芯粒内部以及后续芯粒之间传递的时钟信号也为单端时钟信号。

上述实施方式提供的芯粒封装芯片能够适应不同类型的时钟信号,提高易用性。

在上述实施方式的基础上,多个芯粒同构或异构。如果为同构,则表示硬件结构上,多个芯粒上设置的输入时钟缓冲器7和输出时钟缓冲器8的数量以及位置相同。如果为异构,则表示硬件结构上,多个芯粒上设置的输入时钟缓冲器7和输出时钟缓冲器8的数量以及位置相同。

注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

- 用于封装上输入/输出接口的具有共用基准时钟信号的低功率、抖动和时延的时钟

- 垂直信号路径、具有该垂直信号路径的印刷电路板和具有该印刷电路板的半导体封装、以及半导体芯片