一种氮化硼本征缺陷调控方法及其在阻变存储器上的应用

文献发布时间:2024-01-17 01:13:28

技术领域

本发明属于新型存储器件技术领域,涉及一种氮化硼本征缺陷调控方法及其在阻变存储器上的应用。

背景技术

近年来信息产业发展迅速,信息处理量飞速增加,对存储器的集成密度和处理速度提出了更高的要求。目前的存储器技术采用多级存储体系,包括快速响应的易失性存储器和高度集成的非易失性存储器,但这样的复杂系统已经难以满足智能时代高速信息处理的需求,“存储墙”瓶颈难以克服。开发同时具有低功耗和快响应的新型非易失性存储器是解决“存储墙”瓶颈的可行方案。

在前期研究中,基于氧化物的非易失性存储器表现出了稳定的阻变现象和明确的阻变机理,但是活性金属离子在氧化物阻变层中地随机注入导致器件的保留能力降低。以二维材料为阻变层的阻变存储器具有快速开关、低功耗、结构简单等优势,拥有良好的透明性和弯折可塑性,器件的三明治结构可以将阻变存储器的尺寸缩小到纳米级,这些优点使其成为下一代存储器的有利候选者。

化学气相沉积(chemical vapor deposition,CVD)是目前氮化硼阻变层的生长方法之一,CVD氮化硼中有较多的缺陷,但难以调控。而商业高质量氮化硼晶体中缺陷数量又十分有限,不能作为阻变层使用,因此亟需开发缺陷可控的氮化硼阻变层生长方法。此外,阻变存储器中活性金属电极的使用也导致了器件耐久性降低,器件的稳定性有待提升,在第一次开启时需要施加一个较大的电压进行激活(forming过程)。因此,开发基于氮化硼本征缺陷的阻变存储器,并对不同缺陷密度的氮化硼阻变存储器的性能和工作机理进行研究及优化是非常必要的。

发明内容

本发明的目的在于提供一种氮化硼本征缺陷调控方法,建立了生长源中碳粉含量与硼空位缺陷密度的关系,构建了基于硼空位导电细丝原理的氮化硼阻变存储器,解决了现有的氮化硼阻变存储器中缺陷密度和电学性能关系不明确、工作电压高、器件性能不稳定的问题。

本发明采用的技术方案如下:

根据本说明书的第一方面,提供一种氮化硼本征缺陷调控方法,包括:通过常压高温金属溶剂法生长氮化硼晶体的过程中,调节生长源中碳粉的比例,实现氮化硼中硼空位缺陷密度的调控。

进一步地,所述生长源为镍铬合金、氮化硼粉末、及碳粉混合物,其中碳粉的质量占比为0-6.8%。

根据本说明书的第二方面,提供一种基于氮化硼本征缺陷的阻变存储器,其特征在于,以带有本征缺陷的氮化硼薄膜作为阻变存储器的阻变层,以惰性电极作为顶电极和底电极,形成金属/氮化硼/金属三明治结构的阻变存储器。

进一步地,所述阻变层的硼空位缺陷密度与生长源中碳粉质量占比存在对应关系。

进一步地,所述顶电极和所述底电极采用惰性金属,材质为以下任一种或多种的组合:金、钨或铂。

进一步地,所述阻变存储器中的导电细丝由硼空位聚集形成,建立阻变层的缺陷密度和导电细丝形成的依赖关系,确定生长源中碳粉的比例使得硼空位缺陷密度适中,实现稳定的高低阻态切换。

进一步地,所述阻变存储器的低阻态电阻随温度升高而降低,符合空位型导电细丝机制,证明了硼空位缺陷密度直接影响导电细丝的形成过程和物理特性,进而决定了阻变存储器的电学性能。

根据本说明书的第三方面,提供一种基于氮化硼本征缺陷的阻变存储器的制备方法,包括:运用光刻和磁控溅射技术在衬底上制备底电极阵列,之后通过转移技术将带有本征缺陷的氮化硼薄片转移到底电极上,最后通过激光直写和磁控溅射技术制备顶电极阵列。

进一步地,氮化硼薄膜转移可以使用PDMS干法转移或PVA湿法转移。

本发明的有益效果:CVD生长的氮化硼薄膜具有非常高的缺陷密度,从高质量氮化硼晶体中剥离出来的氮化硼薄膜具有非常少的缺陷密度,与这两种氮化硼材料相比,本发明通过调控碳粉在生长源中的质量占比,采用常压高温金属溶剂法制备了硼空位缺陷密度可调的氮化硼晶体,机械剥离氮化硼晶体得到的氮化硼薄膜具有相似的缺陷密度,良好的二维结构、热稳定性和化学稳定性,可兼容传统微纳加工工艺,适用于阵列集成。以不同硼空位缺陷密度的氮化硼薄膜作为阻变层构建的阻变存储器,表现出不同的器件性能:在硼空位缺陷密度较低时,空位导电细丝难以形成,观察不到阻变切换;在硼空位缺陷密度较高时,多条空位导电细丝存在竞争生长关系,细丝稳定性差;碳粉质量占比为0.6%的氮化硼薄膜,具有适中的硼空位缺陷密度,构建的阻变存储器表现出优异的阻变性能,包括低的器件开启(+2V)和关断电压(-1.4V),高的器件稳定性(达200次)和存储耐久性(达10

附图说明

图1为本发明实施例提供的氮化硼阻变存储器器件结构示意图。

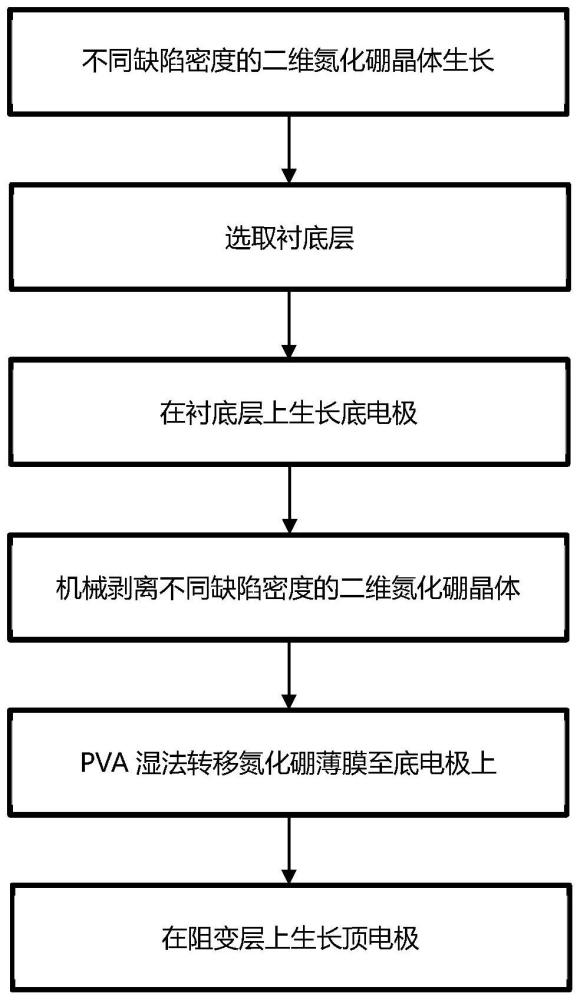

图2为本发明实施例提供的氮化硼阻变存储器器件制备工艺流程示意图。

图3为本发明实施例提供的5×5阵列氮化硼阻变存储器示意图。

图4为本发明实施例提供的氮化硼阻变存储器的forming过程。

图5为本发明实施例提供的氮化硼阻变存储器的电学I-V扫描曲线,体现了电学性能对硼空位缺陷密度的依赖特性。

图6为本发明实施例提供的掺杂碳粉质量占比为0.6%的氮化硼阻变存储器低阻态时电阻随温度的变化趋势。

图中,1-底电极、2-顶电极。

具体实施方式

以下是本发明的具体实施例,进一步阐述本发明。应理解,这些实施例仅用于说明本发明而不用于限制本发明的范围。此外应理解,在阅读了本发明讲授的内容之后,本领域技术人员可以对本发明作各种改动或修改,这些等价形式落于本申请所附权利要求书所限定的范围。

通过常压高温金属溶剂法生长氮化硼晶体的过程中,掺杂不同质量占比的碳粉,调控氮化硼中的硼空位缺陷密度,进而影响硼空位导电细丝通路的形成和阻变存储器的电学性能。

进一步地,在设计器件的三明治结构中,以具有硼空位缺陷的氮化硼薄膜作为阻变层,将惰性金属作为顶电极和底电极,构成阻变存储器阵列。

进一步地,选择平整、没有褶皱的氮化硼薄膜作为阻变层材料。

进一步地,在制备器件时,将氮化硼阻变层用干法或湿法转移到带有惰性金属底电极阵列的衬底上,再在阻变层上制备顶电极阵列。

进一步地,对单个器件施加电压,利用硼空位重新分布排列形成导电细丝。当生长源中碳粉质量占比为0.6%时,由该氮化硼薄膜构建的阻变存储器具有优异的器件性能,导电细丝的首次形成过程需要施加+4.2V的激活电压(forming电压,阻变存储器初次开启需要的电压),之后施加+2V的开启电压和-1.4V关闭电压,可以得到10

实施例1

本实施例中制备具有硼空位缺陷的氮化硼晶体的方法包括以下步骤:

制备材料前,依次使用去离子水、乙醇冲洗CVD炉管和坩埚,然后静置晾干。将氮化硼粉末放入坩埚,并加入碳粉,混合均匀后加入镍铬合金置于粉末上,所述镍铬合金、氮化硼粉末和碳粉的质量比为100:10:(0~8)。然后将坩埚放入氧化铝坩埚舟中,并将氧化铝坩埚舟放入管式炉。关闭管式炉两端进出气阀门,用真空泵抽真空至5×10

实施例2

本实施例中基于氮化硼缺陷的阻变存储器结构如图1所示,衬底为氧化硅片,表面氧化硅层厚度为285nm,单晶硅为电阻率0.001-0.005Ω·cm的p型重掺杂硅。氧化硅上方是底部电极阵列,氮化硼阻变层是实施例1中所制备的多种缺陷密度的氮化硼,阻变层上方是顶部电极阵列。底部电极阵列和顶部电极阵列采用惰性金属,包括但不限于金、铂、钨。

实施例3

图2为本发明实施例3提供的一种阻变存储器的制备方法流程示意图。本实施例中阻变存储器制备过程包括以下步骤:

(1)衬底为带有SiO

(2)利用光刻技术将预先设计好的底部电极图案和用于对准的标记图案制备在衬底上,流程如下:选用5350光刻胶,旋涂光刻胶参数为低速1000r/min共20s,高速4000r/min共30s,105℃下烘干300s。光刻功率为4mW,曝光时间为3s,显影时间为30s。交叉阵列图案中底电极宽度可设置为2-5μm,电极间距可设置为2-5μm。利用直流磁控溅射工艺在衬底层上生长20nm厚的金薄膜作为底电极。将衬底浸泡在丙酮中30min以去除光刻胶,用异丙醇冲洗衬底后烘干,得到预设图案的底电极。

(3)机械剥离不同缺陷密度的氮化硼晶体:取出实施例1生长的氮化硼晶体,放置在透明胶带上。将胶带对折撕开五次,使得氮化硼均匀分布于胶带上。将带有氮化硼的胶带平铺于步骤(2)所处理好的衬底上,使氮化硼和衬底充分接触,贴合24h后观察到在胶带和衬底间无明显气泡,撕开胶带得到带有氮化硼的衬底。分别对多种缺陷密度的氮化硼进行上述步骤操作。

(4)PVA湿法转移氮化硼至底电极上:将带有氮化硼的衬底放置在光学显微镜下,找到合适大小和厚度的氮化硼纳米片,这里选取直径为20μm~60μm,厚度为5~15nm的氮化硼纳米片。将PVA薄膜用胶带固定在PDMS膜上,使用二维材料转移平台将固定好的PVA薄膜贴合到带有目标氮化硼的衬底上,加热至60℃并自然冷却至室温后抬起粘有氮化硼的PVA薄膜,去除用于固定的胶带,使PVA和PDMS可分离,将PVA薄膜上的氮化硼对准并放置在步骤(3)制备好的底电极上,加热至80℃使PVA与PDMS分离,此时带有目标氮化硼的PVA紧贴于底电极。利用PVA溶于水的特性,将衬底放入去离子水1~2h以去除PVA薄膜。得到在底电极上带有氮化硼的双层堆垛结构。

(5)在氮化硼阻变层上生长顶电极:根据氮化硼纳米片的尺寸大小,设计合适的顶电极图案,利用激光直写和磁控溅射技术制备顶电极,具体步骤如下:选用5350光刻胶,旋涂光刻胶参数为低速1000r/min共20s,高速4000r/min共30s,将衬底放置在105℃下300s烘干。激光直写功率为30mW,显影时间为60s。利用直流磁控溅射工艺制备40nm厚的金薄膜作为顶电极。将衬底浸泡在丙酮中30min以去除光刻胶,用异丙醇冲洗衬底后烘干,得到预设图案的顶电极。图3为阵列大小5×5的氮化硼阻变存储器示意图。

选取三种缺陷密度的氮化硼晶体,该三种晶体生长过程中碳粉质量占比分别为0、0.6%和1.8%。对该三种晶体剥离成薄膜并制成阻变存储器,进行对比测试,forming过程如图4所示,生长源中碳粉质量占比为0.6%的氮化硼阻变存储器拥有最低的+4.2V的forming电压。电学性能如图5所示,从电学I-V扫描曲线可以看出,氮化硼的缺陷密度可以调节阻变存储器的开启电压、关闭电压、和开关比。其中,生长源中碳粉质量占比为0.6%和1.8%的氮化硼阻变存储器获得了更大的10

对生长源中碳粉质量占比为0.6%的氮化硼阻变存储器进行变温电学测试,如图6所示,在250K至350K的温度范围内,基于硼空位导电细丝的氮化硼阻变存储器低阻态电阻随温度的升高而降低,符合空位型导电细丝机制。

本文中所描述的具体实施例仅仅是对本发明精神作举例说明。本发明所属技术领域的技术人员可以对所描述的具体实施例做各种各样的修改或补充或采用类似的方式替代,但并不会偏离本发明的精神或者超越所附权利要求书所定义的范围。

- 一种交叉开关结构阻变存储器的优化方法

- 一种集成化阻变存储器及其制备方法

- 一种基于氮化硼/硫化钼/氮化硼三明治结构作为阻变功能层的阻变存储器

- 一种氧化物薄膜阻变存储器多级阻态的电压调控方法