介电组合物和多层电容器

文献发布时间:2024-01-17 01:13:28

本申请要求于2021年12月27日在韩国知识产权局提交的第10-2021-0188595号韩国专利申请的优先权的权益,该韩国专利申请的公开内容通过引用全部包含于此。

技术领域

本公开涉及一种介电组合物和多层电容器。

背景技术

电容器是能够在其中存储电力的元件。当向其中两个电极基本上彼此面对地设置的电容器施加电压时,在每个电极中累积电力。在施加到电容器的电压是直流(DC)电压的情况下,在累积电力的同时电流在电容器中流动,但是一旦完成电力的累积,电流就不在电容器中流动。另一方面,在施加到电容器的电压是交流(AC)电压的情况下,在电极的极性彼此交替的同时AC电流在电容器中流动。

基于设置在电极之间的绝缘体的类型,电容器可分为以下等类型:铝电解电容器,包括利用铝形成的电极和在铝电极之间的薄氧化物膜;钽电容器,使用钽作为电极材料;陶瓷电容器,在电极之间使用具有高介电常数的电介质(诸如钛酸钡);多层陶瓷电容器(MLCC),在多层结构中使用高介电常数陶瓷作为设置在电极之间的电介质;膜电容器,使用聚苯乙烯膜作为电极之间的电介质。

其中,由于多层陶瓷电容器具有优异的温度和频率特性并且可实现为具有小尺寸,因此多层陶瓷电容器最近已经用于各种领域(诸如高频电路)内的装置中。最近,一直尝试进一步减小多层陶瓷电容器的尺寸。为此,已经形成具有小厚度的介电层和内电极。

为了实现多层陶瓷电容器的尺寸减小和电容增加,有必要通过减小介电层和内电极的厚度来增加堆叠的介电层和内电极的数量。目前,介电层的厚度已经减小到约0.6μm,并且对介电层的厚度减小的研究正在不断进行。然而,介电层的厚度减小可能导致DC偏置特性以及可靠性和高温耐压特性的劣化。DC偏置特性是指电容或介电常数随着施加到MLCC的DC偏置电场的大小增加而减小的现象。在应用MLCC(例如,将MLCC应用于功率管理集成电路)的各种情况下,MLCC通常在向其施加DC偏置的状态下使用。因此,对能够在向其施加高DC偏置电场的条件下实现高介电常数或电容的MLCC以及用于制造该MLCC的介电组合物的需求日益增加。

发明内容

本公开的一方面可提供一种具有高可靠性的介电组合物和使用该介电组合物的多层电容器。

根据本公开的一方面,一种介电组合物包括:BaTiO

基于100摩尔的BaTiO

基于100摩尔的BaTiO

所述稀土元素可仅包括Dy和Eu。

根据本公开的另一方面,一种多层电容器可包括:主体,包括堆叠的介电层和多个内电极,且所述介电层介于所述多个内电极之间;以及外电极,设置在所述主体上并连接到所述多个内电极,其中,所述介电层包括介电晶粒,所述介电晶粒包括BaTiO

所述介电晶粒可具有核-壳结构,所述核-壳结构包括核部和具有与所述核部不同的成分的壳部。

所述稀土元素可包括在所述壳部中。

基于100摩尔的BaTiO

基于100摩尔的BaTiO

所述稀土元素可仅包括Dy和Eu。

根据本公开的另一方面,一种多层电容器可包括:主体,包括堆叠的介电层和多个内电极,且所述介电层介于所述多个内电极之间,其中,所述介电层包括介电晶粒,所述介电晶粒包括BaTiO

基于100摩尔的BaTiO

基于100摩尔的BaTiO

所述稀土元素可不包括摩尔含量高于Dy和Eu的其他元素。

基于100摩尔的BaTiO

基于100摩尔的BaTiO

基于100摩尔的BaTiO

基于100摩尔的BaTiO

附图说明

根据以下结合附图的具体实施方式,将更清楚地理解本公开的上述和其他方面、特征和优点,在附图中:

图1是示出根据本公开中的示例性实施例的多层电容器的示意性立体图;

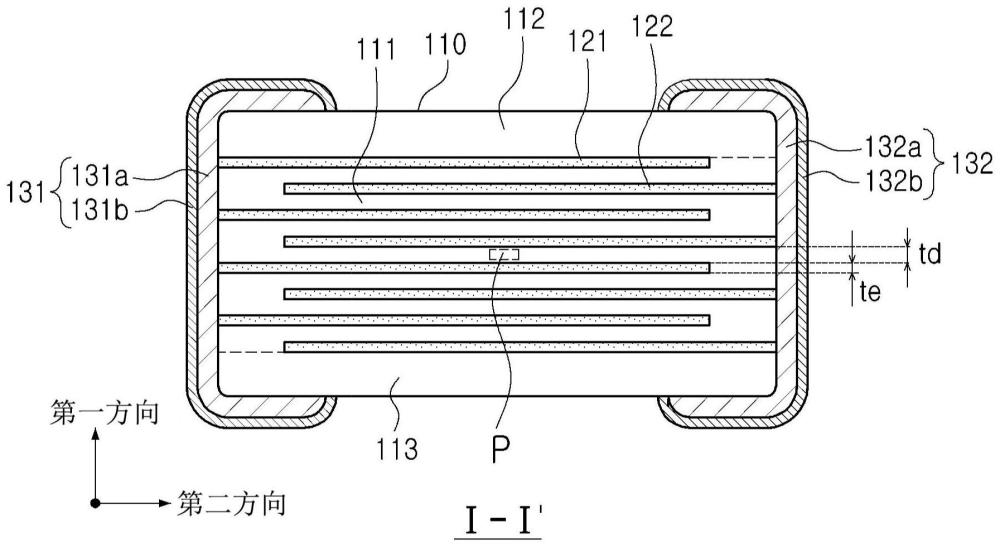

图2是沿图1的线I-I'截取的示意性截面图;

图3是沿图1的线II-II'截取的示意性截面图;

图4是示出根据本公开中的示例性实施例的多层电容器的主体的示意性分解立体图;

图5是用于解释本公开的介电层中的微结构的示意图;以及

图6A至图8B示出了电容温度系数(TCC)和平均失效时间(MTTF)的实验结果,表明Dy和Eu摩尔含量对介电可靠性的影响。

具体实施方式

在下文中,现在将参照附图详细描述本公开的示例性实施例。

根据本公开中的示例性实施例的介电组合物可包括BaTiO

介电组合物中副成分的组成条件基于主成分的功能和实验示例来设定,这将在下面描述。介电组合物通过离子之间的材料运动主要经过致密化和晶粒生长进行烧结。这里,致密化通过离子的表面扩散而发生,并且晶粒生长通过用于减小总表面积的界面运动而发生。在这种情况下,随着电介质中晶界(这是高电阻因素)的数量增加,电荷运动速率可能降低。因此,可通过细化介电晶粒以增大晶界数量来改善电介质的介电常数。然而,在电场强度增加的薄层环境中(例如,当介电层的厚度为0.5μm或更小时),即使在晶界处肖特基势垒也可能降低,导致导电性提高。可添加功函数高于BaTiO

除了考虑核-壳结构中的晶界和界面之外,为了使电介质在高电场环境中具有小的厚度和高水平的绝缘电阻,电荷具有低浓度是有利的。具体地,通过使作为MLCC的绝缘电阻劣化的主要因素的氧空位缺陷最小化,能够防止在晶粒中形成p-n结(在晶粒中形成p-n结会导致绝缘电阻劣化)。在本示例性实施例中,为了抑制晶粒中的导电现象,可使用稀土元素作为具有强n型趋势的元素。具体地,可将不同的稀土元素作为副成分添加到BaTiO

基于上述考虑和实验结果,本公开的发明人尝试优化稀土副成分的含量条件。结果,首先得出基于100摩尔的BaTiO

如上所述,在根据本示例性实施例的介电组合物中,优化了作为副成分添加的稀土元素的组合,并且由此可预期电介质不仅在微结构的均匀性和密度方面改善而且在高温可靠性和耐压方面改善。此外,稀土元素之间的含量比可根据要组合在一起的稀土元素而变化。这可能是因为根据Dy和Eu之间的离子半径和化合价的差异的缺陷化学反应。也就是说,稀土元素的含量需要根据要添加的稀土元素而变化,因为即使包含相同含量的稀土元素,具有与Ba更相似的离子半径的稀土元素也可能具有更富含施主的缺陷化学反应,产生电子并由此引起n型导电。然而,当单独使用具有强施主类型倾向的Eu或以与Dy相比过高的含量添加Eu时,电子发射可能过量,导致电介质的绝缘电阻降低。因此,优选满足上面提出的含量条件。

在下文中,将描述通过使用上述介电组合物获得的多层电容器的示例。然而,本公开的介电组合物可应用于各种电子产品,例如,电感器、压电元件、压敏电阻或热敏电阻、以及多层电容器。

图1是示出根据本公开中的示例性实施例的多层电容器的示意性立体图。图2是沿图1的线I-I'截取的示意性截面图。图3是沿图1的线II-II'截取的示意性截面图。图4是示出根据本公开中的示例性实施例的多层电容器的主体的示意性分解立体图。图5是用于解释本公开的介电层中的微结构的示意图。

参照图1至图5,根据本公开中的示例性实施例的多层电容器100可包括主体110以及外电极131和132。这里,主体110可包括堆叠的多个介电层111和多个内电极121和122,且介电层111中的每个介于内电极121和122之间。

在主体110中,介电层111和内电极121和122可交替堆叠。主体110的具体形状没有特别限制,并且主体110可具有如图所示的六面体形状等。尽管主体110由于包括在主体110中的陶瓷粉末在烧结过程中收缩而不具有包含完美直线的六面体形状,但是主体110可具有大致六面体形状。主体110可具有在第一方向上彼此面对的第一表面1和第二表面2、连接到第一表面1和第二表面2并且在第二方向上彼此面对的第三表面3和第四表面4、以及连接到第一表面1和第二表面2、连接到第三表面3和第四表面4并且在第三方向上彼此面对的第五表面5和第六表面6。形成主体110的多个介电层111可一体化到使得在不使用扫描电子显微镜(SEM)的情况下难以看到烧结状态下的相邻介电层111之间的边界的程度。

主体110可包括电容形成部Ac以及覆盖部112和113,电容形成部Ac设置在主体110中并且通过包括设置成彼此面对的第一内电极121和第二内电极122且使介电层111中的每个介于第一内电极121和第二内电极122之间来形成电容,覆盖部112和113分别在第一方向上形成在电容形成部Ac的上表面和下表面上。另外,对形成电容器的电容有贡献的电容形成部Ac可通过重复堆叠多个第一内电极121和多个第二内电极122且使介电层111中的每个介于第一内电极121和第二内电极122之间来形成。

参照图5,介电层111可包括各自具有核-壳结构的介电晶粒11,所述核-壳结构包括核部11a和具有与核部11a的成分不同的成分的壳部11b,并且也可包括各自具有非核-壳结构的介电晶粒12。当多层电容器100的介电层111使用上述介电组合物形成时,介电层111的介电晶粒11和12可包括BaTiO

当具有核-壳结构的介电晶粒11中的核部11a的直径被定义为D1时,D1可满足条件5nm≤D1≤100nm。另外,当介电晶粒11的直径被定义为D2时,D2可满足条件50nm≤D2≤600nm。在这种情况下,介电晶粒11的直径可以是通过如下方式获得的值:测量介电晶粒11中的每个的面积、将介电晶粒11转换成具有测得的面积的当量圆、并且计算该当量圆的直径。可按照类似的方式来获得核部11a的直径。关于具有核-壳结构的介电晶粒11中稀土元素(即,Dy和Eu)的含量,如图5所示,可从一个介电晶粒11的一端到相对端绘制线段,该线段具有以相等间隔布置的九个点P1、P2、P3、P4、P5、P6、P7、P8和P9,可使用STEM/EDS分析点P1、P2、P3、P4、P5、P6、P7、P8和P9处的Dy和Eu中的至少一种的含量。更具体地,在通过STEM扫描图2的区域P以获得其图像之后,可通过STEM/EDS分析来分析点P1、P2、P3、P4、P5、P6、P7、P8和P9处的要检测元素的含量。通过该分析,可确定核部11a和壳部11b之间的边界。例如,从介电晶粒11的表面向内基本上没有检测到稀土元素的区域可被确定为边界。

此外,包含在上述介电组合物中的副成分可以按氧化物或碳酸盐的形式添加,但是在烧结后可以以固溶形式存在于BaTiO

在下文中,将描述主体110的其他组件,并且当形成覆盖部112和113、边缘部114和115以及介电层111时,可使用上述介电组合物。

覆盖部112和113可包括在第一方向上设置在电容形成部Ac的上表面上的上覆盖部112和在第一方向上设置在电容形成部Ac的下表面上的下覆盖部113。上覆盖部112和下覆盖部113可通过在厚度方向上在电容形成部Ac的上表面和下表面中的每个上堆叠单个介电层或者两个或更多个介电层来形成,并且可基本上用于防止内电极由于物理应力或化学应力而损坏。上覆盖部112和下覆盖部113可包括与介电层111相同的材料,同时不包括内电极。也就是说,上覆盖部112和下覆盖部113可包括陶瓷材料,例如,钛酸钡(BaTiO

边缘部114和115可设置在电容形成部Ac的侧表面上。边缘部114和115可包括设置在电容形成部Ac的在宽度方向上的一个侧表面上的边缘部114和设置在电容形成部Ac的在宽度方向上的另一侧表面上的边缘部115。也就是说,边缘部114和115可设置在电容形成部Ac的在宽度方向上的相对侧表面上。如图3所示,边缘部114和115可指:在主体110的沿宽度和厚度(W-T)方向切割的截面中,第一内电极121和第二内电极122的两端与主体110的外表面之间的区域。边缘部114和115可基本上用于防止内电极由于物理应力或化学应力而损坏。边缘部114和115可通过将用于形成内电极的导电膏涂覆到除了要形成边缘部的位置之外的陶瓷生片上来形成。可选择地,为了抑制由于内电极121和122引起的电容形成部Ac的厚度不均匀,可通过以下方式来形成边缘部114和115:切割通过堆叠陶瓷生片(在陶瓷生片上涂覆有用于形成内电极的导电膏)而形成的层叠体,使得内电极暴露于电容形成部Ac的在宽度方向(第三方向)上的相对侧表面,然后在电容形成部Ac的在宽度方向(第三方向)上的相对侧表面中的每个上堆叠单个介电层或者两个或更多个介电层。

此外,不需要特别限制介电层111中的每个的厚度td。然而,通常,当介电层形成为具有小于0.6μm(特别是0.5μm或更小)的小厚度时,担心可靠性会降低。如上所述,根据本公开中的示例性实施例,能够确保室温下的高介电常数、优异的DC偏置特性和优异的高温耐压特性,因此,即使当介电层111中的每个的厚度为0.5μm或更小时,也可确保优异的可靠性。因此,当介电层111中的每个的厚度为0.5μm或更小时,根据本公开的可靠性改善效果可更显著。介电层111中的每个的厚度td可指设置在第一内电极121和第二内电极122之间的每个介电层111的平均厚度。可从通过使用扫描电子显微镜(SEM)扫描主体110的在长度和厚度(L-T)方向上的截面而获得的图像中测量介电层111中的每个的平均厚度。例如,对于从通过使用电子显微镜(SEM)扫描主体110的在第一方向和第二方向(厚度方向和长度方向)上的截面(在主体110的在第三方向(宽度方向)上的中心部分处切割的截面)而获得的图像中提取的任意介电层,可测量在长度方向上等间隔的30个点处的介电层的厚度以获得平均值。可在电容形成部Ac内测量等间隔的30个点处的介电层的厚度,电容形成部Ac是指第一内电极121和第二内电极122彼此叠置的区域。

内电极121和122可与介电层111交替堆叠。内电极121和122可包括第一内电极121和第二内电极122。第一内电极121和第二内电极122可交替地设置成彼此面对,且构成主体110的介电层111中的每个介于第一内电极121和第二内电极122之间,并且第一内电极121和第二内电极122分别暴露于主体110的第三表面3和第四表面4。参照图2,第一内电极121可与主体110的第四表面4间隔开并且通过主体110的第三表面3暴露,并且第二内电极122可与主体110的第三表面3间隔开并且通过主体110的第四表面4暴露。在这种情况下,第一内电极121和第二内电极122可通过设置在第一内电极121和第二内电极122之间的介电层111中的每个彼此电断开。参照图4,可通过以下方式来形成主体110:交替堆叠其上印刷有用于第一内电极121的导电膏的陶瓷生片和其上印刷有用于第二内电极122的导电膏的陶瓷生片,然后烧结。用于形成内电极121和122的材料没有特别限制,并且可以是具有优异导电性的材料。例如,内电极121和122可包括镍(Ni)、铜(Cu)、钯(Pd)、银(Ag)、金(Au)、铂(Pt)、锡(Sn)、钨(W)、钛(Ti)和它们的合金中的一种或更多种。此外,内电极121和122可通过在陶瓷生片上印刷用于内电极的导电膏来形成,该导电膏包括镍(Ni)、铜(Cu)、钯(Pd)、银(Ag)、金(Au)、铂(Pt)、锡(Sn)、钨(W)、钛(Ti)和它们的合金中的一种或更多种。可使用丝网印刷法、凹版印刷法等印刷用于内电极的导电膏,但是印刷导电膏的方法不限于此。

另外,不需要特别限制内电极121和122中的每个的厚度te。然而,通常,当内电极形成为具有小于0.6μm(特别是0.5μm或更小)的小厚度时,担心可靠性会降低。如上所述,根据本公开中的示例性实施例,能够确保室温下的高介电常数、优异的DC偏置特性和优异的高温耐压特性,因此,即使当内电极121和122中的每个的厚度为0.5μm或更小时,也可确保优异的可靠性。因此,当内电极121和122中的每个的厚度为0.5μm或更小时,根据本公开的效果可更显著,并且可容易地实现多层电容器的尺寸减小和电容增加。内电极121和122中的每个的厚度te可指第一内电极121和第二内电极122中的每个的平均厚度。可从通过使用扫描电子显微镜(SEM)扫描主体110的在长度和厚度(L-T)方向上的截面而获得的图像中测量内电极121和122中的每个的平均厚度。例如,对于从通过使用扫描电子显微镜(SEM)扫描主体110的在第一方向和第二方向(厚度方向和长度方向)上的截面(在主体110的在第三方向(宽度方向)上的中心部分处切割的截面)而获得的图像中提取的第一内电极121和第二内电极122中的任一个,可测量在长度方向上等间隔的30个点处的内电极的厚度以获得平均值。可在电容形成部Ac内测量等间隔的30个点处的内电极的厚度,电容形成部Ac是指第一内电极121和第二内电极122彼此叠置的区域。

外电极131和132可分别设置在主体110的第三表面3和第四表面4上。外电极131和132可包括第一外电极131和第二外电极132,第一外电极131和第二外电极132分别设置在主体110的第三表面3和第四表面4上,并且分别连接到第一内电极121和第二内电极122。参照图1,外电极131和132可设置为覆盖边缘部114和115在第二方向上的相对端表面。尽管在本示例性实施例中描述了多层电容器100包括两个外电极131和132,但是外电极131和132的数量、形状等可根据内电极121和122的形状或根据其他目的进行修改。此外,外电极131和132可使用任何类型的材料形成,只要其具有导电性即可,例如外电极131和132可使用金属形成,并且可考虑电特性、结构稳定性等来确定用于形成外电极131和132的具体材料。此外,外电极131和132可具有多层结构。例如,参照图2,外电极131和132可包括设置在主体110上的电极层131a和132a以及分别形成在电极层131a和132a上的镀层131b和132b。作为电极层131a和132a的更具体的示例,电极层131a和132a中的每个可以是包括导电金属和玻璃的烧制电极或包括导电金属或树脂的树脂基电极。

可选地,电极层131a和132a中的每个可通过在主体上顺序地堆叠烧制电极和树脂基电极而形成。另外,电极层131a和132a中的每个可通过将包括导电金属的片材转印到主体上或通过将包括导电金属的片材转印到烧制电极上来形成。包括在电极层131a和132a中的导电金属可以是具有优异电连接性的材料,但不特别限于此。例如,导电金属可以是镍(Ni)、铜(Cu)及它们的合金中的一种或更多种。镀层131b和132b可用于改善多层电容器的安装特性。用于形成镀层131b和132b的材料的类型没有特别限制,并且可包括Ni、Sn、Pd及它们的合金中的一种或更多种。此外,镀层131b和132b中的每个可形成为多个层。作为镀层131b和132b的更具体的示例,镀层131b和132b可以是Ni镀层或Sn镀层,或者镀层131b和132b可通过分别在电极层131a和132a上顺序堆叠Ni镀层和Sn镀层来形成,或者镀层131b和132b可通过分别在电极层131a和132a上顺序堆叠Sn镀层、Ni镀层和Sn镀层来形成。可选地,镀层131b和132b中的每个可包括多个Ni镀层和/或多个Sn镀层。

不需要特别限制多层电容器100的尺寸。然而,为了实现多层电容器的尺寸减小和电容增加两者,需要通过减小介电层和内电极的厚度来增加堆叠的介电层和内电极的数量。例如,当多层电容器100具有0402(长×宽=0.4mm×0.2mm)或更小的尺寸时,根据本公开的改善DC偏置特性和高温耐压特性的效果可更显著。因此,考虑到制造误差、外电极的尺寸等,当多层电容器100具有0.44mm或更小的长度和0.22mm或更小的宽度时,根据本公开的可靠性改善效果可更显著。这里,多层电容器100的长度可指多层电容器100在第二方向上的最大尺寸,并且多层电容器100的宽度可指多层电容器100在第三方向上的最大尺寸。

在下文中,将通过由本公开的发明人进行的实验示例更详细地描述本公开,但是呈现实验示例以帮助具体理解本公开,本公开的范围不由实验示例限制。

作为基体材料主成分,使用粒度为大于等于30nm且小于等于100nm的BaTiO

表1示出了样品的实验结果,在每个样品中,稀土副成分的含量是基于100摩尔的BaTiO

[表1]

下面将参照表1以及图6A至图8B讨论上述实验结果。在满足本示例性实施例中提出的稀土副成分的含量条件(即,0.10 如上所述,根据本公开中的示例性实施例的介电组合物当用于多层电容器中时能够改善结构特征和电特性,并改善可靠性。 虽然上面已经示出和描述了示例性实施例,但是对于本领域技术人员将易于理解的是,在不脱离由所附权利要求限定的本公开的范围的情况下,可进行修改和变化。

- 用于低温烧结的玻璃组合物、玻璃粉、介电组合物以及使用介电组合物的多层陶瓷电容器

- 用于低温烧结的玻璃组合物、玻璃粉、介电组合物以及使用介电组合物的多层陶瓷电容器