阵列基板

文献发布时间:2023-06-19 09:27:35

技术领域

本申请涉及显示技术领域,特别涉及一种阵列基板。

背景技术

液晶显示装置(Liquid Crystal Display,LCD),由于其具有机身轻薄、耗能少、工作电压低且无辐射等优点,在计算机屏幕、电视机屏幕、移动数字电话等领域得到了广泛的应用。

液晶显示装置通常具有栅极驱动电路,栅极驱动电路可产生扫描信号使得液晶显示装置实现显示扫描。相关技术中,通常将栅极驱动电路设置在阵列基板的周边边框区域,使得液晶显示装置具有较大面积的边框区域。

发明内容

本申请实施例提供一种阵列基板,可以减窄阵列基板的边框区域。

本申请实施例提供一种阵列基板,包括显示区域和复位信号线,所述复位信号线设置于所述显示区域,所述复位信号线在所述显示区域处于显示状态时保持在低电位,且在显示区域处于消隐状态时产生脉冲信号。

在本申请实施例的阵列基板中,所述阵列基板还包括多个呈阵列式排布的像素单元,所述多个像素单元设置于所述显示区域,所述多个像素单元呈阵列式排布,每一所述像素单元均具有暗纹区域,所述复位信号线的一部分位于至少一个所述像素单元的暗纹区域内。

在本申请实施例的阵列基板中,所述阵列基板包括多个GOA单元,所述多个GOA单元设置于所述显示区域的外侧,每一所述GOA单元均与所述复位信号线连接。

在本申请实施例的阵列基板中,所述阵列基板包括多个GOA单元,所述多个GOA单元设置于所述显示区域,每一所述GOA单元均与所述复位信号线连接。

在本申请实施例的阵列基板中,所述GOA单元包括第一晶体管和第二晶体管,所述第一晶体管和所述第二晶体管之间具有间隔区域,所述复位信号线的一部分位于所述间隔区域内,且所述复位信号线与所述第二晶体管的栅极连接。

在本申请实施例的阵列基板中,所述GOA单元还包括时钟信号线、栅开电压控制线和至少一条扫描线,所述时钟信号线、所述栅开电压控制线和至少一条扫描线均从所述显示区域延伸至所述显示区域的外侧。

在本申请实施例的阵列基板中,所述时钟信号线和所述栅开电压控制线相互平行设置。

在本申请实施例的阵列基板中,所述阵列基板还包括时钟控制总线、栅开电压控制总线和公共电极线,所述时钟控制总线、所述栅开电压控制总线和所述公共电极线设置于所述显示区域的外侧,且所述时钟控制总线与所述时钟信号线连接,所述栅开电压控制总线与所述栅开电压控制线连接。

在本申请实施例的阵列基板中,所述CF基板公共电极线、所述时钟控制总线、所述栅开电压控制总线和所述公共电极线从所述显示区域的外侧朝所述显示区域的方向依次排列且平行设置。

在本申请实施例的阵列基板中,所述显示区域包括相对设置的第一侧边和第二侧边,所述复位信号线的个数为两条,其中一条所述复位信号线靠近所述第一侧边设置,另一个所述复位信号线靠近所述第二侧边设置。

本申请实施例的阵列基板通过将复位信号线设置于显示区域,相比于直接将复位信号线设置在阵列基板的周边边框区域,可以减小复位信号线对阵列基板的周边边框区域的占用,从而减窄阵列基板的周边边框区域。

附图说明

为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍。显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

图1为本申请实施例提供的阵列基板的第一种结构示意图。

图2为本申请实施例提供的阵列基板的第二种结构示意图。

图3为图2所示阵列基板中像素单元以及GOA单元的结构示意图。

图4为本申请实施例提供的阵列基板的第三种结构示意图。

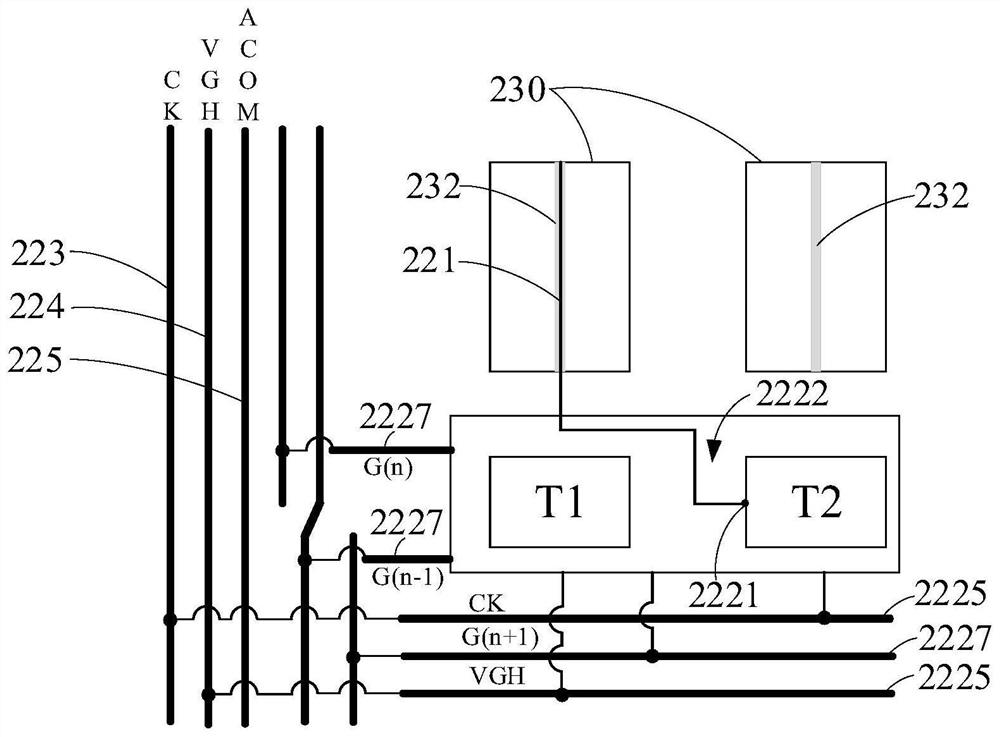

图5为图3所示像素单元以及GOA单元中GOA单元的结构示意图。

图6为本申请实施例提供的阵列基板的第四种结构示意图。

图7为本申请实施例提供的阵列基板的第五种结构示意图。

图8为本申请实施例提供的显示面板的第一种结构示意图。

图9为本申请实施例提供的显示面板的第二种结构示意图。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

本申请实施例提供一种阵列基板,如图1所示,图1为本申请实施例提供的阵列基板的第一种结构示意图。阵列基板200可以包括显示区域210,显示区域210可以用于显示画面。可以理解的是,显示区域210为阵列基板200的有效显示区域(Active Area,AA),显示区域210可以设置有像素阵列,像素阵列包括多个以矩阵方式排布的像素单元。

阵列基板200还可以包括GOA(Gate Driver on Array,阵列基板栅极驱动)电路220,GOA电路220是将采用GOA技术将驱动电路直接制造在阵列(Array)基板上所形成的电路结构。GOA电路220可以包括复位信号线221,复位信号线221设置于显示区域210,复位信号线221在显示区域210处于显示状态时(比如显示画面时)保持在低电位,且在显示区域210处于消隐状态时产生脉冲信号,以驱动GOA电路复位。一般在相邻两个显示帧之间会设置有消隐时间(Blanking time),复位信号线221在消隐时间产生脉冲信号,而在显示区域210处于显示状态时,复位信号线221始终处于低电位,避免对显示区域210所显示的帧画面产生影响,使得显示区域210可以正常显示。

相关技术中,通常将复位信号线221设置于显示区域210的外侧,或者说阵列基板200的非显示区域中,这样会导致阵列基板200的非显示区域的面积较大,从而使得阵列基板200的边框变宽。本申请实施例从实际应用出发,将GOA电路220中的复位信号线221设置于显示区域210,相比于相关技术,在阵列基板200的非显示区域中可以至少减少一根信号线的占用面积,从而缩小阵列基板200的非显示区域对阵列基板的占用面积,以达到减窄阵列基板200的边框的目的。

结合图2和图3所示,图2为本申请实施例提供的阵列基板的第二种结构示意图,图3为图2所示阵列基板中像素单元以及GOA单元的结构示意图。阵列基板200还可以包括多个像素单元230,多个像素单元230设置于显示区域210内,多个像素单元230呈阵列式排布设置,每一像素单元230均具有暗纹区域232,复位信号线221的一部分位于至少一个像素单元230的暗纹区域232内。

可以理解的是,由于受到TFT(Thin Film Transistor,薄膜晶体管)和CF(ColorFilter,彩色滤光片)两侧的光配向和ITO(Indium Tin Oxide,铟锡氧化物)边缘电场的双重作用,像素单元230内部会形成一些配向暗纹区域。复位信号线221的一部分设置于至少一个像素单元230的暗纹区域232内,比如可以将复位信号线221的一部分设置于一个像素单元230、两个像素单元230、五个像素单元230或十个像素单元230的暗纹区域232内,并将其他部分设置于像素单元230的外部区域,比如相邻两个像素单元230之间的区域。本申请实施例中对复位信号线221穿设于多少个像素单元230的暗纹区域232并不予以限定。

请继续参阅图2,GOA电路220还可以包括多个GOA单元222,多个GOA单元222可以相互级联,多个GOA单元222均设置于显示区域210的外侧。显示区域210可以为规则形状,比如显示区域210可以为矩形形状,显示区域210可以具有相对设置的第一侧边212和第二侧边214,阵列基板200可以具有第一非显示区域240,第一非显示区域240设置于显示区域210的边缘且相对于第二侧边214靠近第一侧边212。多个GOA单元222均设置于第一非显示区域240,多个GOA单元222可以相互级联。

其中,每一GOA单元222均与复位信号线221连接,复位信号线221可以对GOA单元222进行控制,以控制GOA单元222复位。比如,每一GOA单元222可以均设置有复位信号端2221,每一GOA单元222通过复位信号端2221与复位信号线221连接,复位信号线221可以在显示区域210处于消隐状态时产生脉冲信号并通过复位信号端2221将该脉冲信号输入至GOA单元222中,以控制GOA单元222复位。

需要说明的是,GOA单元222的设置位置并不限于此,替代性地,比如,如图4所示,图4为本申请实施例提供的阵列基板的第三种结构示意图。多个GOA单元222可以设置于显示区域210内。多个GOA单元222可以相互级联。每一GOA单元222均与复位信号线221连接,复位信号线221可以对GOA单元222进行控制,以控制GOA单元222复位。

本申请实施例中,GOA电路220中的复位信号线221和GOA单元222均设置于显示区域210内,其可以直接在显示区域210内相互连接,相比于图3所示的阵列基板,本申请实施例可以减少显示区域210的开口率,而且还可以减少图3所示中GOA单元和复位信号线221之间的连接线,进而减少GOA电路220对显示区域210的占用空间,提升像素单元230的穿透率。

结合图3和图5所示,图5为图3所示像素单元以及GOA单元中GOA单元的结构示意图。GOA单元222可以包括多个晶体管,比如GOA单元222可以包括第一晶体管T1和第二晶体管T2,第一晶体管T1和第二晶体管T2间隔设置在显示区域210内,或者说第一晶体管T1和第二晶体管T2之间具有间隔区域2222,复位信号线221的一部分位于间隔区域2222内。比如复位信号线221可以穿设过像素单元230的暗纹区域232后,再在间隔区域2222走线至第二晶体管T2的位置,并与第二晶体管T2的栅极连接。

GOA单元还可以包括第三晶体管T3、第四晶体管T4,第五晶体管T51、第六晶体管T52、第七晶体管T53、第八晶体管T54、第九晶体管T6、第十晶体管T7、第十一晶体管T8和电容Cb。

其中,第一晶体管T1的栅极和第一晶体管T1的漏极均与第n-1级GOA单元222的扫描信号线G(n-1)连接以接收第n级GOA单元的扫描线的输入信号,第一晶体管T1的源极与第二晶体管T2的漏极以及第n级GOA单元222的节点Q(n)连接,第二晶体管T2的源极与电源负电压VSS连接。第五晶体管T51的栅极、第五晶体管T51的漏极和第七晶体管T53的漏极均与栅开电压控制线连接,第五晶体管T51的源极与第七晶体管T53的栅极连接,第七晶体管T53的源极与第八晶体管T54的漏极和第九晶体管T6的栅极连接,第八晶体管T54的栅极和第六晶体管T52的栅极均与第n级GOA单元222的节点Q(n)连接,第六晶体管T52的漏极与第七晶体管T53的栅极连接,第六晶体管T52的源极、第八晶体管T54的源极均与电源负电压VSS连接,第九晶体管T6的源极、第十晶体管T7的源极均与电源负电压VSS连接,第九晶体管T6的漏极与第n级GOA单元的扫描信号线G(n)连接以向扫描信号线G(n)输出信号,第十晶体管T7与栅极与第七晶体管T53的源极连接,第十晶体管T7的漏极与第n级GOA单元222的节点Q(n)连接,第三晶体管T3的栅极和第四晶体管T4的栅极均与第n+1级GOA单元222的扫描信号线G(n+1)连接以接收第n+1级GOA单元222的扫描线的输入信号,第三晶体管T3的源极和第四晶体管T4的源极均与电源负电压VSS连接,第三晶体管T3的漏极与第n级GOA单元的扫描信号线G(n)连接以向扫描信号线G(n)输出信号,第四晶体管T4的漏极与第n级GOA单元222的节点Q(n)连接,第十一晶体管T8的栅极与第四晶体管T4的漏极连接,第十一晶体管T8的漏极与第n级GOA单元222的时钟信号线CK(n)连接,第十一晶体管T8的源极与第n级GOA单元的扫描信号线G(n)连接以向扫描信号线G(n)输出信号,电容Cb并联连接在第十一晶体管T8的栅极和第十一晶体管T8的源极之间。

需要说明的是,图5所示的GOA单元222的电路结构仅为示例性的,本申请实施例的GOA单元222的电路结构也可以为其他结构。

请继续参阅图2和图3,GOA单元222还可以包括时钟信号线(CK)2225、栅开电压控制线(VGH)2226和至少一条扫描线2227(诸如扫描线G(n-1)、扫描线G(n)和扫描线G(n+1)),时钟信号线(CK)2225、栅开电压控制线(VGH)2226和至少一条扫描线2227相互平行设置。时钟信号线2225、栅开电压控制线(VGH)2226和至少一条扫描线2227均从显示区域210延伸至显示区域210的外侧(比如延伸至第一非显示区域240),并与其对应的信号线连接。以节省对显示区域210的占用空间。

例如,GOA电路220还可以包括时钟控制总线(CK)223和栅开电压控制总线(VGH)224,时钟控制总线(CK)223和栅开电压控制总线(VGH)224均设置于显示区域210的外侧,比如时钟控制总线(CK)223和栅开电压控制总线(VGH)224均可以设置在第一非显示区域240,且时钟控制总线(CK)223和栅开电压控制总线(VGH)224相互平行设置。其中时钟控制总线(CK)223可以传输时钟信号,其可以与每一GOA单元222的时钟信号线(CK)2225连接,以对每一GOA单元222进行控制,进而控制每一像素单元230可以根据时钟信号进行帧画面的显示。栅开电压控制总线(VGH)224可以用于传输栅开电压信号,其可以与每一GOA单元222的栅开电压控制线(VGH)2226连接,以对每一GOA单元222进行控制,该栅开电压信号可以为每一GOA单元222中的晶体管提供电压信号,以打开每一GOA单元222中的晶体管,从而控制像素单元230显示画面或不显示画面。

GOA电路220还包括公共电极线(ACOM)225,请继续参阅图2均设置于所述显示区域210的外侧(比如设置于第一非显示区域240)。其中,时钟控制总线(CK)223、栅开电压控制总线(VGH)224和公共电极线(ACOM)225从显示区域210的外侧朝显示区域210的方向依次排列设置,而且时钟控制总线(CK)223、栅开电压控制总线(VGH)224和公共电极线(ACOM)225从显示区域210相互平行设置,以减小GOA电路220的走线对显示区域210外侧(诸如第一非显示区域240)的占用空间,有利于减小显示区域210边缘区域(诸如第一非显示区域240)的面积,以起到减窄边框的效果。

如图6和图7所示,图6为本申请实施例提供的阵列基板的第四种结构示意图,图7为本申请实施例提供的阵列基板的第五种结构示意图。本申请实施例的GOA电路220的个数可以为两个,其中一个GOA电路220可以靠近第一侧边212设置,另一个GOA电路220可以靠近第二侧边214设置。比如阵列基板200可以包括显示区域210、第一非显示区域240和第二非显示区域250,第一非显示区域240设置在第一侧边212的边缘,第二非显示区域250设置在第二侧边214的边缘,其中一个GOA电路220设置于第一非显示区域240内,另一个GOA电路220设置于第二非显示区域250内,两个GOA电路220共同对多行像素单元230进行控制,比如其中一个GOA电路220可以负责控制奇数行的像素单元230,另一个GOA电路220可以负责控制偶数行的像素单元。相比于只在第一非显示区域240设置GOA电路,本申请实施例的设计方式更合理,也更方便走线。

可以理解的是,每一GOA电路220均包括一条复位信号线221,即本申请实施例的复位信号线221的条数为两条,其中一条复位信号线221设置于显示区域210中靠近第一侧边212的位置,另一条复位信号线221设置于显示区域中靠近所述第二侧边214的位置。

本申请实施例还提供一种显示面板,示例性地,如图8所示的显示面板20,图8为本申请实施例提供的显示面板的第一种结构示意图。显示面板20包括阵列基板200、彩膜基板400和液晶层600,彩膜基板400设置于阵列基板200的一侧,液晶层600夹设于阵列基板200和彩膜基板400之间。阵列基板200为如上申请实施例所述的阵列基板。

如图9所示,图9为本申请实施例提供的显示面板的第二种结构示意图。彩膜基板400包括CF公共电极线(CFCOM)420,CF公共电极线(CFCOM)420设置于显示区域210的外侧,CF公共电极线(CFCOM)420、时钟控制总线(CK)223、栅开电压控制总线(VGH)224和公共电极线(ACOM)225从显示区域210的外侧朝显示区域210的方向依次排列且平行设置。

以上对本申请实施例提供的阵列基板以及显示面板进行了详细介绍。本文中应用了具体个例对本申请的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本申请。同时,对于本领域的技术人员,依据本申请的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本申请的限制。