时标同步系统、时标同步方法及星载导航接收机

文献发布时间:2023-06-19 09:54:18

技术领域

本发明涉及卫星通信领域,特别涉及一种时标同步系统、时标同步方法及星载导航接收机。

背景技术

在现有的星载导航接收机中,一般存在多个相互独立的时钟信号源,例如在一些星载导航接收机中,用于对测距电文信号进行发送和接收的导航任务处理模块使用10.23MHz(兆赫兹)测距时钟源,而用于对数据进行运算处理的信号处理单元则使用本地时钟源。由于10.23MHz测距时钟源和本地时钟源使用不同的硬件单元提供,同时10.23MHz测距时钟源还根据相对论效应以及其它因素进行了频率的微小补偿,因此,与10.23MHz测距时钟源相干的基准1PPS(Pulse Per Second,秒脉冲)信号与本地时钟源分频得到的本地1PPS信号会随着时间而漂移。另外,由于在星载导航接收机开机时,本地时钟源的初始相位是随机的,其不一致性约为本地时钟源的一个时钟周期,因此,即使将本地1PPS信号简单地同步至基准1PPS信号,本地时钟源与10.23MHz测距时钟源的相位差也难以保持一致,基准1PPS与本地1PPS信号的相位差在每次开关机后都不相同,从而导致了星载导航接收机在每次开关机后所测得的伪距不一致。

发明内容

本发明旨在至少解决现有技术中存在的技术问题之一。为此,本发明提出一种时标同步系统、时标同步方法及星载导航接收机,应用于10.23MHz测距时钟源与本地时钟源不同源的星载导航接收机,能够使本地时钟源产生的本地1PPS信号与测距时钟源相干的基准1PPS信号同步,并且能够使星载导航接收机在每次开关机后伪距测量结果一致。

根据本发明第一方面实施例的时标同步系统,包括:

基准信号模块,用于接收基准时钟信号和基准秒脉冲信号并生成上升沿与所述基准秒脉冲信号同步的标准时钟信号和清零信号;

数字控制振荡器,用于输出同步时钟信号;

早迟信号模块,与所述数字控制振荡器和所述基准信号模块信号连接,用于将所述同步时钟信号转换为早迟信号,并用于对所述同步时钟信号进行计数和输出进位信号;

相关器,与所述基准信号模块和所述早迟信号模块信号连接,用于计算所述早迟信号和所述标准时钟信号的误差量;

相位频率控制模块,与所述数字控制振荡器、所述早迟信号模块和所述相关器信号连接,用于根据所述误差量调整所述同步时钟信号的频率和相位;

第一计数器,与所述基准信号模块和所述早迟信号模块信号连接,用于对所述进位信号进行计数和输出本地秒脉冲信号。

根据本发明第一方面实施例的时标同步系统,至少具有如下有益效果:

基准信号模块接收10.23MHz测距时钟源输出的基准时钟信号和基准秒脉冲信号并生成与基准秒脉冲信号上升沿同步的标准时钟信号,基准信号模块输出标准时钟信号至相关器。数字控制振荡器与本地时钟源信号连接,在相位频率控制模块的控制下输出同步时钟信号至早迟信号模块。早迟信号模块在接收到同步时钟信号后,通过移相和做差的方式得到早迟信号,并通过对同步时钟信号进行计数得到进位信号,早迟信号模块输出早迟信号至相关器以及输出进位信号至第一计数器。相关器对早迟信号和标准时钟信号进行相关运算并计算出早迟信号和标准时钟信号的误差量,相关器将误差量输出至相位频率控制模块,相位频率控制模块根据误差量调整同步时钟信号的频率和相位,使同步时钟信号的频率与标准时钟信号的频率一致,并且使同步时钟信号的相位与标准时钟信号的相位之差在任何时候都能够保持一致,而不受本地时钟源开关机初相的影响。本实施例的时标同步系统通过数字控制振荡器、早迟信号模块、相位频率控制模块和相关器构成闭环的时钟同步回路,通过对早迟信号与标准时钟信号进行相关计算的方式,动态调整同步时钟信号的频率和相位,使同步时钟信号的频率同步于10.23MHz测距时钟源的频率,同时使同步时钟信号与基准秒脉冲信号的相位差始终保持一致而不受本地时种源开关机初相的影响,使星载导航接收机在每次开关机后伪距测量结果一致。另外,第一计数器对早迟信号模块输出的进位信号进行计数,满足计数条件后输出本地秒脉冲信号,当基准信号模块接收到基准秒脉冲信号时向早迟信号模块和第一计数器发送清零信号,使早迟信号模块和第一计数器在新的基准秒脉冲信号周期内对同步时钟信号重新进行计数,由于在数字控制振荡器、早迟信号模块、相位频率控制模块和相关器所构成的闭环时钟同步回路中对同步时钟信号、基准时钟信号和基准秒脉冲信号进行了同步处理,因此当第一计数器和早迟信号模块设置的计数周期与基准秒脉冲信号的周期相同时,第一计数器能够输出与基准秒脉冲信号精确同步的本地秒脉冲信号。

进一步地,所述基准信号模块包括方波生成器和缓存器,所述缓存器与所述早迟信号模块和所述第一计数器信号连接,所述方波生成器与所述相关器信号连接,所述缓存器用于接收所述基准秒脉冲信号并输出所述清零信号,所述方波生成器用于将所述基准秒脉冲信号和所述基准时钟信号转换成波峰值和波谷值与所述早迟信号相同的所述标准时钟信号,所述标准时钟信号为上升沿与所述基准秒脉冲信号同步且频率为所述基准时钟信号二分之一的方波信号。

进一步地,所述早迟信号模块包括第二计数器和比较器,所述第二计数器与所述比较器、所述数字控制振荡器、所述第一计数器和所述基准信号模块信号连接,所述比较器与所述相位频率控制模块和所述相关器信号连接,所述第二计数器用于对所述同步时钟信号进行计数并输出所述进位信号和早信号,所述早信号的频率为所述同步时钟信号的二分之一,所述比较器用于接收所述早信号并生成相位滞后于所述早信号的迟信号,所述比较器对所述早信号和所述迟信号进行比较后输出阶梯状的所述早迟信号,所述早迟信号的频率为所述同步时钟信号的二分之一。

根据本发明第二方面实施例的时标同步方法,应用于时标同步系统,所述时标同步系统包括基准信号模块、数字控制振荡器、早迟信号模块、相关器、相位频率控制模块和第一计数器,所述早迟信号模块与所述数字控制振荡器、所述基准信号模块、所述相位频率控制模块、所述相关器和所述第一计数器信号连接,所述相关器与所述基准信号模块和所述相位频率控制模块信号连接,所述相位频率控制模块与所述数字控制振荡器信号连接,所述第一计数器与所述基准信号模块信号连接;

所述时标同步方法包括:

所述基准信号模块获取基准秒脉冲信号和基准时钟信号,向所述相关器输出上升沿与所述基准秒脉冲信号同步的标准时钟信号,并且向所述早迟信号模块和所述第一计数器发送清零信号;

所述数字控制振荡器获取本地时钟信号和所述相位频率控制模块存储的频率控制字和相位控制字,向所述早迟信号模块发送同步时钟信号;

所述早迟信号模块获取所述清零信号和所述同步时钟信号,对所述早迟信号模块进行复位和对所述同步时钟信号进行计数,所述早迟信号模块向所述相关器输出早迟信号,当满足计数条件,所述早迟信号模块向所述第一计数器输出进位信号;

所述相关器获取所述标准时钟信号和所述早迟信号,计算所述早迟信号和所述标准时钟信号的误差量,向所述相位频率控制模块输出所述误差量;

所述相位频率控制模块获取所述误差量,调整所述频率控制字和所述相位控制字;

所述第一计数器获取所述清零信号和所述进位信号,对所述第一计数器进行复位和对所述进位信号进行计数,当满足计数条件,所述第一计数器输出本地秒脉冲信号。

根据本发明第二方面实施例的时标同步方法,至少具有如下有益效果:

执行本实施例时标同步方法的数字控制振荡器、早迟信号模块、相位频率控制模块和相关器构成闭环的时钟同步回路:基准信号模块在接收到10.23MHz测距时钟源输出的基准时钟信号和与10.23MHz测距时钟源相干的基准秒脉冲信号后向相关器输出上升沿与基准秒脉冲信号同步的标准时钟信号,并向早迟信号模块和第一计数器发送清零信号;数字控制振荡器在本地时钟源输出的本地时钟信号的驱动下,对相位频率控制模块中存储的频率控制字和相位控制字进行运算并向早迟信号模块输出当前频率控制字和相位控制字所对应的同步时钟信号;早迟信号模块通过对同步时钟信号进行移相和比较得到早迟信号并输出至相关器;相关器对标准时钟信号和早迟信号的特定位置进行相关运算并计算出误差量,相关器将误差量输出至相位频率控制模块;相位频率控制模块根据误差量调整频率控制字和相位控制字的数值,从而达到控制数字控制振荡器所输出的同步时钟信号的频率和相位的目的;通过本实施例的时标同步方法能够使连接本地时钟源的数字控制振荡器输出频率与基准时钟信号频率一致并且与基准秒脉冲信号相差恒定的同步时钟信号,避免本地时钟源的开关机初相对伪距测量结果的影响。早迟信号模块对同步时钟信号进行计数,当满足计数条件时,向第一计数器输出进位信号,第一计数器对进位信号进行计数,当满足计数条件时,第一计数器输出本地秒脉冲信号,而当基准信号模块接收到基准秒脉冲信号时,会向早迟信号模块和第一计数器发送清零信号,使早迟信号模块和第一计数器清零并在新的基准秒脉冲信号周期内对同步时钟信号进行计数,与此同时,在数字控制振荡器、早迟信号模块、相位频率控制模块和相关器所构成的闭环时钟同步回路中使用到的标准时钟信号的上升沿与基准秒脉冲信号同步,因此使用本实施例的时标同步方法可以使由本地时钟源所产生的本地秒脉冲信号与10.23MHz测距时钟源相干的基准秒脉冲信号精确地同步。

进一步地,所述基准信号模块包括方波生成器和缓存器,所述缓存器与所述早迟信号模块和所述第一计数器信号连接,所述方波生成器与所述相关器信号连接;

所述基准信号模块获取基准秒脉冲信号和基准时钟信号,向所述相关器输出与所述基准秒脉冲信号上升沿同步的标准时钟信号,并向所述早迟信号模块和所述第一计数器发送清零信号,包括:

所述缓存器获取基准秒脉冲信号,向所述早迟信号模块和所述第一计数器输出清零信号;

所述方波生成器获取基准时钟信号和基准秒脉冲信号,输出波峰值和波谷值与所述早迟信号相同的标准时钟信号,所述标准时钟信号为上升沿与所述基准秒脉冲信号同步且频率为所述基准时钟信号二分之一的方波信号。

进一步地,所述早迟信号模块包括第二计数器和比较器,所述第二计数器与所述比较器、所述数字控制振荡器、所述第一计数器和所述基准信号模块信号连接,所述比较器与所述相位频率控制模块和所述相关器信号连接;

所述早迟信号模块获取所述清零信号和所述同步时钟信号,对所述早迟信号模块进行复位和对所述同步时钟信号进行计数,所述早迟信号模块向所述相关器输出早迟信号,当满足计数条件时,所述早迟信号模块向所述第一计数器输出进位信号,包括:

所述第二计数器获取所述清零信号并对所述第二计数器进行复位;

所述第二计数器获取所述同步时钟信号,对所述同步时钟信号进行计数,当满足计数条件时,向所述第一计数器输出进位信号;

所述第二计数器获取所述同步时钟信号,向所述比较器输出频率为所述同步时钟信号二分之一的早信号;

所述比较器获取所述早信号和所述相位频率控制模块存储的相差控制字,产生滞后于所述早信号的迟信号;

所述比较器对所述早信号和所述迟信号进行差值运算,并向所述相关器输出频率为所述同步时钟信号二分之一的阶梯状的早迟信号。

进一步地,所述相关器获取所述标准时钟信号和所述早迟信号,计算所述早迟信号和所述标准时钟信号的误差量,向所述相位频率控制模块输出所述误差量,包括:

所述相关器获取所述标准时钟信号上升沿后的所述早迟信号波形,计算和输出第一误差量;

所述相关器获取所述标准时钟信号下降沿后的所述早迟信号波形,计算和输出第二误差量。

进一步地,所述相位频率控制模块获取所述误差量,调整所述频率控制字的数值和所述相位控制字的数值,包括:

所述相位频率控制模块获取所述第一误差量,对所述相位控制字的数值进行调整;

所述相位频率控制模块获取所述第二误差量,对所述频率控制字的数值进行调整。

进一步地,所述迟信号滞后于所述早信号的时间为所述早信号的周期的十分之二。

根据本发明第三方面实施例的星载导航接收机,包括上述第一方面实施例的时标同步系统。本实施例的星载导航接收机通过使用上述第一方面实施例的时标同步系统,能够使本地时钟源产生的本地1PPS信号与测距时钟源相干的基准1PPS信号同步,并且在每次开关机后伪距测量结果一致。

本发明的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

附图说明

本发明的上述和/或附加的方面和优点从结合下面附图对实施例的描述中将变得明显和容易理解,其中:

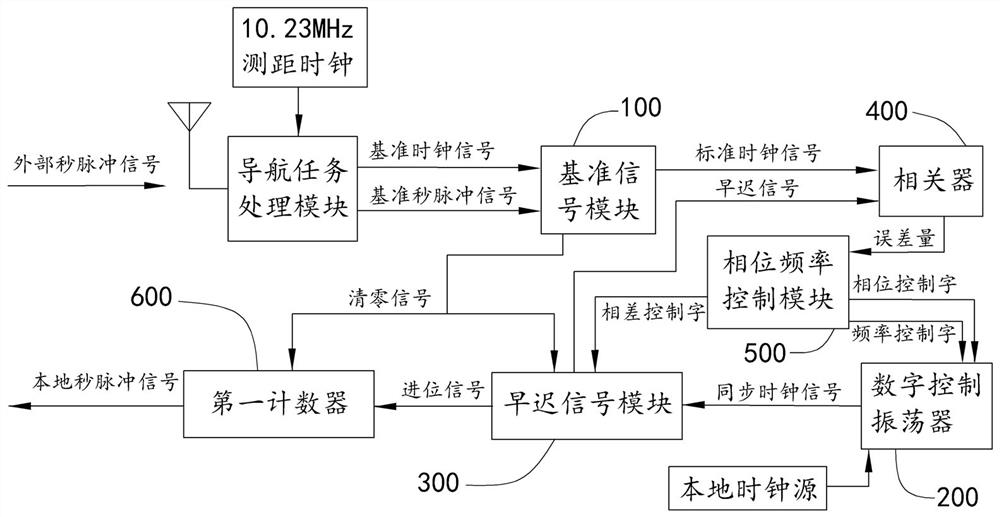

图1为本发明的一个实施例提供的时标同步系统原理框图;

图2为本发明的另一个实施例提供的时标同步系统原理框图;

图3为本发明的一个实施例提供的时标同步系统各信号波形的时序图;

图4为本发明的一个实施例提供的时标同步方法的示意图;

图5为本发明的另一个实施例提供的时标同步方法的示意图;

图6为本发明的另一个实施例提供的时标同步方法的示意图;

图7为本发明的另一个实施例提供的时标同步方法的示意图;

图8为本发明的另一个实施例提供的时标同步方法的示意图;

图9为本发明的一个实施例提供的误差量计算示意图;

图10为本发明的另一个实施例提供的误差量计算示意图。

具体实施方式

下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,仅用于解释本发明,而不能理解为对本发明的限制。

在本发明的描述中,若干的含义是一个或者多个,多个的含义是两个以上,大于、小于、超过等理解为不包括本数,以上、以下、以内等理解为包括本数。如果有描述到第一、第二只是用于区分技术特征为目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量或者隐含指明所指示的技术特征的先后关系。

本发明的描述中,除非另有明确的限定,设置、连接等词语应做广义理解,所属技术领域技术人员可以结合技术方案的具体内容合理确定上述词语在本发明中的具体含义。

下面结合附图详细描述本发明第一方面实施例的时标同步系统。

参照图1,本发明的一个实施例提供的时标同步系统,包括基准信号模块100、数字控制振荡器200、早迟信号模块300、相关器400、相位频率控制模块500和第一计数器600,早迟信号模块300与基准信号模块100、数字控制振荡器200、相关器400、相位频率控制模块500和第一计数器600信号连接,相关器400与基准信号模块100和相位频率控制模块500信号连接,相位频率控制模块500与所述数字控制振荡器200信号连接,第一计数器600与基准信号模块100信号连接。

基准信号模块100接收来自导航任务处理模块使用的10.23MHz测距时钟源所输出的基准时钟信号和与10.23MHz测距时钟源相干的基准秒脉冲信号并生成与基准秒脉冲信号上升沿同步的标准时钟信号,其中,基准时钟信号的频率为10.23MHz,基准秒脉冲信号的频率为1Hz(赫兹),标准时钟信号的波峰值和波谷值与早迟信号的波峰值和波谷值相等,基准信号模块100将标准时钟信号输出至相关器400并将基准秒脉冲信号作为清零信号输出至早迟信号模块300和第一计数器600。数字控制振荡器200与本地时钟源信号连接,在数字控制振荡器200内设置有相位累加单元和波形存储单元,相位累加单元在本地时钟源输出的本地时钟信号的控制下,对相位频率控制模块500内存储的频率控制字不断累加得到以频率控制字为步进的数字相位,再加上相位频率控制模块500内存储的相位控制字,以相位控制字单元作为相位偏移量,得到要输出的当前相位,然后将当前相位作为地址值送入波形存储单元,通过查表获得当前相位对应的波形幅度值,数字控制振荡器200在频率控制字和相位控制字的共同作用下形成同步时钟信号,其中,同步时钟信号的频率由频率控制字控制,同步时钟信号的相位由相位控制字控制,最后数字控制振荡器200将同步时钟信号输出至早迟信号模块300,为了使同步时钟信号与基准时钟信号快速同步,同步时钟信号的初始频率值预设为10.23MHz。早迟信号模块300在接收到同步时钟信号后,将同步时钟信号分作两路,早迟信号模块300根据相位频率控制模块500内存储的相差控制字对其中一路同步时钟信号进行相位延时,然后对两路同步时钟信号进行相减运算得出早迟信号,早迟信号模块300将早迟信号输出至相关器400。相关器400在接收到早迟信号和标准时钟信号后,在标准时钟信号的上升沿附近和下降沿附近分别取适量的早迟信号样本与标准时钟信号进行比较,并计算早迟信号波峰中点与标准时钟信号上升沿的误差量以及早迟信号波谷中点与标准时钟信号下降沿的误差量。相关器400将误差量发送至相位频率控制模块500,相位频率控制模块500根据误差量调整相位控制字和频率控制字的值,最终使早迟信号的波峰中点与标准时钟信号上升沿重合和使早迟信号的波谷中点与标准时钟信号的下降沿重合。由此,通过数字控制振荡器200、早迟信号模块300、相关器400和相位频率控制模块500所构成的闭环时钟同步回路可以使同步时钟信号的频率与基准时钟信号同步,并且使同步时钟信号与基准秒脉冲信号的相位差保持一致,使伪距的测量结果不受本地时钟源开关机初相的影响。

另外,早迟信号模块300对同步时钟信号进行计数,当满足计数周期,早迟信号模块300向第一计数器600输出进位信号,第一计数器600对进位信号进行计数,当满足计数周期,第一计数器600输出本地秒脉冲信号,而基准信号模块100在接收到基准秒脉冲信号时向早迟信号模块300和第一计数器600发送清零信号,使早迟信号模块300和第一计数器600在新的基准秒脉冲信号周期内对同步时钟信号重新进行计数,由于基准信号模块100使标准时钟信号的上升沿与基准秒脉冲信号同步,标准时钟信号与同步时钟信号在数字控制振荡器200、早迟信号模块300、相关器400和相位频率控制模块500所构成的闭环时钟同步回路中实现了频率和相位的同步,因此当第一计数器600和早迟信号模块300设置的计数周期与基准秒脉冲信号的周期相同时,第一计数器600能够输出与基准秒脉冲信号精确同步的本地秒脉冲信号。通过本实施例的时标同步系统能够输出与基准秒脉冲信号精确同步的本地秒脉冲信号。

参照图2,本发明的另一个实施例提供的时标同步系统,在上述实施例的基础上,基准信号模块100包括方波生成器110和缓存器120,早迟信号模块300包括第二计数器310和比较器320,缓存器120与第二计数器310和第一计数器600信号连接,方波生成器110与相关器400信号连接,数字控制振荡器200、第二计数器310、比较器320、相关器400和相位频率控制模块500依次信号连接构成闭环的时钟同步回路。缓存器120用于接收与10.23MHz测距时钟源相干的基准秒脉冲信号,对基准秒脉冲信号进行缓存后作为清零信号输出至早迟信号模块300和第一计数器600,对基准秒脉冲信号进行缓存能够避免清零信号影响第一计数器600对本地秒脉冲信号的输出,以及避免基准秒脉冲信号与本地时钟源不同源而产生的亚稳态现象,保证清零信号能够正常触发早迟信号模块300和第一计数器600进行清零动作。

第二计数器310为模204600计数器,当数字控制振荡器200向第二计数器310输出满204600个周期的同步时钟信号,第二计数器310向第一计数器600输出进位信号,第一计数器600为模50计数器,当第二计数器310向第一计数器600输出50次进位信号,第一计数器600输出本地秒脉冲信号,由于同步时钟信号的频率为10.23MHz,因此第一计数器600每输出一次本地秒脉冲信号的周期为一秒。由于第二计数器310每接收一个周期的同步时钟信号,其计数位的最低位加一,即第二计数器310的计数位的最低位每隔一个同步时钟信号周期翻转一次,由此能够将第二计数器310的计数位的最低位作为早信号输出至比较器320,早信号为频率是同步时钟信号的二分之一的方波信号,即5.115MHz的方波信号。比较器320根据相位频率控制模块500的相差控制字,对早信号进行移相,得到相位滞后于早信号的迟信号,比较器320通过对比早信号和迟信号,输出幅值为早信号与迟信号差值的阶梯状早迟信号至相关器400,早迟信号的频率值为5.115MHz。

方波生成器110接收来自导航任务处理模块使用的10.23MHz测距时钟源所输出的基准时钟信号和与10.23MHz测距时钟源相干的基准秒脉冲信号,输出标准时钟信号,具体地,方波生成器110对基准时钟信号进行计数,每接收一个周期的基准秒脉冲信号对输出电平翻转一次,从而生成频率为基准时钟信号频率二分之一的标准时钟信号,即5.115MHz的方波信号,而当有基准秒脉冲信号到来,方波生成器110输出标准时钟信号的上升沿,使标准时钟信号与基准秒脉冲信号同步。为了便于相关器400对早迟信号和标准时钟信号的波形进行比较,方波生成器110输出的标准时钟信号的波峰值和波谷值与早迟信号的波峰值和波谷值相等。

通过本实施例的方波生成器110、缓存器120、第二计数器310和比较器320生成早迟信号、标准时钟信号和清零信号,电路结构简单,易于实现而且能够确保本实施例的时钟同步系统稳定运行。

本领域技术人员可以理解,图1和图2中示出的结构并不构成对时标同步系统的限定,还可以包括比图1和图2所示更多或更少的部件,或者组合某些部件,或者不同的部件布置。例如,在图1和图2中示出的基准信号模块100或方波生成器110和缓存器120、数字控制振荡器200、早迟信号模块300或第二计数器310和比较器320、相关器400、相位频率控制模块500和第一计数器600可以是由具有特定功能的元器件,如加法器芯片、乘法器芯片、数字控制振荡器芯片、比较器芯片、计数器芯片,触发器芯片、延时芯片、存储芯片、模数转换器芯片或数模转换器芯片等组合而成;也可以是由电阻、电容、电感、晶体管和场效应管等分立元件所构成的加法器电路、乘法器电路、数字控制振荡器电路、比较器电路、计数器电路,触发器电路、延时电路、存储电路、模数转换器电路或数模转换器电路等具有特定功能的电路所组合而成;还可以是由Soc(System on Chip,片上系统),FPGA(Field-ProgrammableGate Array,现场可编程门阵列),DSP(Digital Signal Processing/Processor,数字信号处理)或MCU(Micro Control Unit,微控制器单元)等集成电路实现。本发明不对时标同步系统的硬件实现形式作限定。

下面结合附图详细描述本发明第二方面实施例的时标同步方法。

参照图1、图3和图4,本发明的一个实施例提供的时标同步方法,该方法应用于时标同步系统,时标同步系统包括基准信号模块100、数字控制振荡器200、早迟信号模块300、相关器400、相位频率控制模块500和第一计数器600,早迟信号模块300与基准信号模块100、数字控制振荡器200、相关器400、相位频率控制模块500和第一计数器600信号连接,相关器400与基准信号模块100和相位频率控制模块500信号连接,相位频率控制模块500与数字控制振荡器200信号连接,第一计数器600与基准信号模块100信号连接,该方法包括但不限于以下步骤:

S100,基准信号模块100获取基准秒脉冲信号和基准时钟信号,向相关器400输出上升沿与基准秒脉冲信号同步的标准时钟信号,并向早迟信号模块300和第一计数器600发送清零信号;

S200,数字控制振荡器200获取本地时钟信号和相位频率控制模块500存储的频率控制字和相位控制字,向早迟信号模块300发送同步时钟信号;

S300,早迟信号模块300获取清零信号和同步时钟信号,对早迟信号模块300进行复位和对同步时钟信号进行计数,早迟信号模块300向相关器400输出早迟信号,当满足计数条件,早迟信号模块300向第一计数器600输出进位信号;

S400,相关器400获取标准时钟信号和早迟信号,计算早迟信号和标准时钟信号的误差量,向相位频率控制模块500输出误差量;

S500,相位频率控制模块500获取误差量,调整频率控制字和相位控制字;

S600,第一计数器600获取清零信号和进位信号,对第一计数器600进行复位和对进位信号进行计数,当满足计数条件,第一计数器600输出本地秒脉冲信号。

执行本实施例的时标同步方法的数字控制振荡器200、早迟信号模块300、相关器400和相位频率控制模块500构成闭环的时钟同步回路。具体地,当基准信号模块100接收到10.23MHz测距时钟源输出的频率为10.23MHz的基准时钟信号和与10.23MHz测距时钟源相干的基准秒脉冲信号,向相关器400输出上升沿与基准秒脉冲信号同步的标准时钟信号,并向早迟信号模块300和第一计数器600发送清零信号;数字控制振荡器200的相位累加单元在本地时钟源输出的本地时钟信号的驱动下,对相位频率控制模块500中存储的频率控制字进行累加运算,并且把累加的结果与相位控制字进行加法运算,然后根据运算结果从数字控制振荡器200的波形存储单元中查找对应的波形幅度值,最后向早迟信号模块300输出当前频率控制字和相位控制字所对应的同步时钟信号,为了使同步时钟信号能够快速与基准时钟信号同步,同步时钟信号的预设频率值为10.23MHz;早迟信号模块300在接收到同步时钟信号后,将同步时钟信号分作两路,早迟信号模块300根据相位频率控制模块500内存储的相差控制字对其中一路同步时钟信号进行相位延时,然后对两路同步时钟信号进行相减运算得出早迟信号,早迟信号模块300将早迟信号输出至相关器400;相关器400在接收到早迟信号和标准时钟信号后,在标准时钟信号的上升沿和下降沿附近分别对早迟信号的幅值和标准时钟信号的幅值进行比较,并将早迟信号和标准时钟信号的误差量发送至相位频率控制模块500;相位频率控制模块500根据误差量调整频率控制字和相位控制字的数值,从而达到控制数字控制振荡器200所输出的同步时钟信号的频率和相位的目的;由此,通过本实施例的时标同步方法,使数字控制振荡器200、早迟信号模块300、相关器400和相位频率控制模块500构成闭环的时钟同步回路,并产生频率与基准时钟信号同步的同步时钟信号,使同步时钟信号与基准秒脉冲信号的相位差保持一致,使伪距的测量结果不受本地时钟源开关机初相的影响。

另外,早迟信号模块300对同步时钟信号进行计数,当满足计数周期,早迟信号模块300向第一计数器600输出进位信号,第一计数器600对进位信号进行计数,当满足计数周期,第一计数器600输出本地秒脉冲信号,而基准信号模块100在接收到与10.23MHz测距时钟源相干的基准秒脉冲信号时向早迟信号模块300和第一计数器600发送清零信号,使早迟信号模块300和第一计数器600在新的基准秒脉冲信号周期内对同步时钟信号重新进行计数,因此当第一计数器600和早迟信号模块300设置的计数周期与基准秒脉冲信号的周期相同时,基准秒脉冲信号和本地秒脉冲信号同步。进一步地,由于基准信号模块100使标准时钟信号的上升沿与基准秒脉冲信号同步,标准时钟信号与同步时钟信号在数字控制振荡器200、早迟信号模块300、相关器400和相位频率控制模块500所构成的闭环时钟同步回路中实现了频率和相位的同步,因此,第一计数器600能够输出与基准秒脉冲信号精确同步的本地秒脉冲信号。时标同步系统通过本实施例的时标同步方法能够输出与基准秒脉冲信号精确同步的本地秒脉冲信号。

参照图2、图3和图5,本发明的另一个实施例提供的时标同步方法,在上述实施例的基础上,基准信号模块100包括方波生成器110和缓存器120,缓存器120与早迟信号模块300和第一计数器600信号连接,方波生成器110与相关器400信号连接,进一步地,图5所示方法为图4中步骤S100的具体流程,该方法包括但不限于以下步骤:

S110,缓存器120获取基准秒脉冲信号,向早迟信号模块300和第一计数器600输出所述清零信号;

S120,方波生成器110获取基准时钟信号和基准秒脉冲信号,输出波峰值和波谷值与早迟信号相同的标准时钟信号,标准时钟信号为上升沿与基准秒脉冲信号同步且频率为基准时钟信号二分之一的方波信号。

通过本实施例的时标同步方法,能够避免清零信号影响第一计数器600对本地秒脉冲信号的输出,以及避免基准秒脉冲信号与本地时钟源不同源而产生的亚稳态现象,保证清零信号能够正常触发早迟信号模块300和第一计数器600进行清零动作。同时,能够使基准信号模块100输出的标准时钟信号易于与早迟信号作比较,简化电路设计。

具体地,执行该方法的缓存器120接收与10.23MHz测距时钟源相干的基准秒脉冲信号,对基准秒脉冲信号进行缓存后作为清零信号输出至早迟信号模块300和第一计数器600;执行该方法的方波生成器110接收来自导航任务处理模块使用的10.23MHz测距时钟源所输出的基准时钟信号和与10.23MHz测距时钟源相干的基准秒脉冲信号,对基准时钟信号进行计算,每接收一个周期的基准时钟信号对输出电平翻转一次,从而生成频率为基准时钟信号频率二分之一的标准时钟信号,即5.115MHz的方波信号,而当有基准秒脉冲信号到来,方波生成器110使标准时钟信号的上升沿与基准秒脉冲信号同步,方波生成器110使标准时钟信号的波峰值和波谷值与早迟信号的波峰值和波谷值相等。

参照图2、图3和图6,本发明的另一个实施例提供的时标同步方法,在上述实施例的基础上,早迟信号模块300包括第二计数器310和比较器320,第二计数器310与比较器320、数字控制振荡器200、第一计数器600和基准信号模块100信号连接,比较器320与相位频率控制模块500和相关器400信号连接,进一步地,图6所示方法为图4中步骤S300的具体流程,该方法包括但不限于以下步骤:

S310,第二计数器310获取清零信号并对第二计数器310进行复位;

S320,第二计数器310获取同步时钟信号,对同步时钟信号进行计数,当满足计数条件时,向第一计数器600输出进位信号;

S330,第二计数器310获取同步时钟信号,向比较器320输出频率为同步时钟信号二分之一的早信号;

S340,比较器320获取早信号和相位频率控制模块500存储的相差控制字,产生滞后于早信号的迟信号;

S350,比较器320对早信号和迟信号进行差值运算,并向相关器400输出频率为同步时钟信号二分之一的阶梯状的早迟信号。

具体地,执行本实施例时标同步方法的第二计数器310为模204600计数器,同步时钟信号的预设频率值或与基准时钟信号同步后的频率值为10.23MHz,当数字控制振荡器200向第二计数器310输出满204600个周期的同步时钟信号,第二计数器310向第一计数器600输出进位信号,第一计数器600为模50计数器,当第二计数器310向第一计数器600输出50次进位信号,第一计数器600输出本地秒脉冲信号,因此第一计数器600每输出一次本地秒脉冲信号的周期为一秒。由于第二计数器310每接收一个周期的同步时钟信号,其计数位的最低位加一,即第二计数器310的计数位的最低位每隔一个同步时钟信号周期翻转一次,由此能够将第二计数器310的计数位的最低位作为早信号输出至比较器320,由此得到的早信号为频率是同步时钟信号频率二分之一的方波信号,即5.115MHz的方波信号,与标准时钟信号的频率相仿。比较器320根据相位频率控制模块500的相差控制字,对早信号进行移相,得到相位滞后于早信号的迟信号,比较器320通过对比早信号和迟信号,输出幅值为早信号与迟信号差值的阶梯状早迟信号至相关器400,早迟信号的频率值与早信号一致,即为5.115MHz。通过本实施例能够使第二计数器310和比较器320产生变化周期与标准时钟信号相仿的早迟信号,便于相关器400进行相关运算,应用本实施时标同步方法的第二计数器310和比较器320电路结构简单,易于实现。

参照图2、图7和图8,本发明的另一个实施例提供的时标同步方法,进一步地,图7所示方法为图4中步骤S400的具体流程,该方法包括但不限于以下步骤:

S410,相关器400获取标准时钟信号上升沿后的早迟信号的波形,计算和输出第一误差量;

S420,相关器400获取标准时钟信号下降沿后的早迟信号的波形,计算和输出第二误差量。

图8所示方法为图4中步骤S500的具体流程,该方法包括但不限于以下步骤:

S510,相位频率控制模块500获取第一误差量,对相位控制字的数值进行调整;

S520,相位频率控制模块500获取第二误差量,对频率控制字的数值进行调整。

具体地,参考图9和图10,首先,在标准时钟信号上升沿后对早迟信号的样本进行分析,当标准时钟信号上升沿出现时,以早迟信号的波峰宽度为取样范围,比较早迟信号与标准时钟信号的幅值,若某一样本的早迟信号与标准时钟信号幅值相等,则该样本的比较结果为-1,若某一样本的早迟信号与标准时钟信号幅值不相等,则比较结果为1,通过对所有样本的比较结果进行累加,可以得出第一误差量。相位频率控制模块500根据第一误差量调整相位控制字,若第一误差量为零,则早迟信号的波峰中点与标准时钟信号上升沿重合,相位控制字的值不变;若第一误差量大于零,相位频率控制模块500使相位控制字的值递增,最终使早迟信号的波峰中点与标准时钟信号上升沿重合;若第一误差量小于零,相位频率控制模块500使相位控制字的值递减,最终使早迟信号的波峰中点与标准时钟信号上升沿重合。接着,在标准时钟信号下降沿后对早迟信号的样本进行分析,当标准时钟信号下降沿出现时,以早迟信号的波谷宽度为取样范围,比较早迟信号与标准时钟信号的幅值,若某一样本的早迟信号与标准时钟信号幅值相等,则该样本的比较结果为1,若某一样本的早迟信号与标准时钟信号幅值不相等,则比较结果为-1,通过对所有样本的比较结果进行累加,可以得出第二误差量。相位频率控制模块500根据第二误差量调整频率控制字,若第二误差量为零,则早迟信号的波谷中点与标准时钟信号下降沿重合,频率控制字的值不变。若第二误差量小于零,相位频率控制模块500使频率控制字的值递减,即增大数字控制振荡器200的相位累加器的溢出周期,减少同步时钟信号的频率,最终使早迟信号的波谷中点与标准时钟信号下降沿重合;若第二误差量大于零,相位频率控制模块500使频率控制字的值递增,即减少数字控制振荡器200的相位累加器的溢出周期,增大同步时钟信号的频率,最终使早迟信号的波谷中点与标准时钟信号下降沿重合。还需要说明的是存储相位控制字和频率控制字的寄存器的位数是有限的,当相位控制字或频率控制字递增使寄存器发生溢出时,寄存器会被清零并重新开始循环计数,从而使同步时钟信号的相位和频率有较宽的调整范围。由此,通过数字控制振荡器200、早迟信号模块300、相关器400和相位频率控制模块500所构成的闭环时钟同步回路可以使同步时钟信号的频率与基准时钟信号同步,并且使同步时钟信号与基准秒脉冲信号的相位差保持一致,使伪距的测量结果不受本地时钟源开关机初相的影响。

进一步地,迟信号滞后于早信号的时间为早信号的周期的十分之二。

通过本实施例的时标同步方法,早迟信号模块300使迟信号滞后于早信号的时间为早信号周期的十分之二,使得由早信号和迟信号做差而得的早迟信号的波峰宽度和波谷宽度为早信号周期的十分之二,而早信号是由同步时钟信号二分频所得,因此,早迟信号的波峰宽度和波谷宽度为同步时钟信号周期的十分之四。当早迟信号与标准时钟信号同步时,早迟信号波峰中点与标准时钟信号的上升沿重合,早迟信号的波峰超前于标准时钟信号上升沿半个波峰宽度,即同步时钟信号周期的十分之二,因此当同步时钟信号与标准时钟信号同步时,同步时钟信号的上升沿超前于标准时钟信号十分之二的同步时钟信号周期,同时,标准时钟信号的上升沿与基准秒脉冲信号同步,因此,同步时钟信号的上升沿超前于基准秒脉冲信号十分之二的同步时钟信号周期,同步时钟信号的上升沿与基准秒脉冲信号存在时间差。由于基准秒脉冲信号用于对早迟信号模块300和第一计数器600进行清零,本地秒脉冲信号是由早迟信号模块300和第一计数器600对同步时钟信号计数所得,且计数周期与基准秒脉冲信号的周期相同,因此将同步时钟信号上升沿与基准秒脉冲信号错开能够防止早迟信号模块300和第一计数器600在未满足计数周期时被清零导致本地秒脉冲信号无法正常输出。

此外,本发明的一个实施例还提供了一种星载导航接收机,该星载导航接收机包括现场可编程门阵列、数字信号处理器和存储介质,现场可编程门阵列与数字信号处理器信号连接,存储介质内部集成于和/或外部电连接于可编程逻辑阵列和/或数字信号处理器。利用现场可编程门阵列和数字信号处理器的功能模块以及存储介质的存储资源实现上述第一方面实施例中的基准信号模块100或方波生成器110和缓存器120、数字控制振荡器200、早迟信号模块300或第二计数器310和比较器320、相关器400、相位频率控制模块500和第一计数器600;存储介质存储有可执行指令和控制参数,并能够使现场可编程门阵列和数字信号处理器能够协同执行上述第二方面实施例的时标同步方法,例如执行以上描述的图4中的方法步骤S100、S200、S300、S400、S500和S600,图5中的方法步骤S110和S120,图6中的方法步骤S310、S320、S330、S340和S350,图7中的方法步骤S410和S420以及图8中的方法步骤S510和S520。本实施例的星载导航接收机的本地时钟源产生的本地秒脉冲信号的频率与测距时钟源相干的基准秒脉冲信号的频率同步且相位差保持一致,能够在每次开关机后对伪距测量的结果保持一致。

上面结合附图对本发明实施例作了详细说明,但是本发明不限于上述实施例,在所述技术领域普通技术人员所具备的知识范围内,还可以在不脱离本发明宗旨的前提下做出各种变化。

- 时标同步系统、时标同步方法及星载导航接收机

- 时标同步系统、时标同步方法及星载导航接收机