半导体装置

文献发布时间:2023-06-19 10:03:37

关联申请

本申请享受以日本专利申请2019-153475号(申请日:2019年8月26日)为基础申请的优先权。本申请通过参照该基础申请,包含基础申请的全部内容。

技术领域

实施方式涉及半导体装置。

背景技术

以往以来,制造出了设有对电压进行变换的电平移位电路的半导体装置。这样的半导体装置中,希望电平移位电路长期间稳定地动作。

发明内容

实施方式提供电平移位电路能够长期间稳定地动作的半导体装置。

实施方式的半导体装置具备n型阱、p型阱、设置在上述n型阱上的p型的第1~第4层、设置在上述p型阱上的n型的第5~第12层、第1~第6栅极电极、第1栅极绝缘膜、比上述第1栅极绝缘膜薄的第2栅极绝缘膜、以及第1~第8布线。上述第1栅极电极设置在上述n型阱中的上述第1层与上述第2层之间的区域的正上区域。上述第2栅极电极设置在上述n型阱中的上述第3层与上述第4层之间的区域的正上区域。上述第3栅极电极设置在上述p型阱中的上述第5层与上述第6层之间的区域的正上区域。上述第4栅极电极设置在上述p型阱中的上述第7层与上述第8层之间的区域的正上区域。上述第5栅极电极设置在上述p型阱中的上述第9层与上述第10层之间的区域的正上区域。上述第6栅极电极设置在上述p型阱中的上述第11层与上述第12层之间的区域的正上区域。上述第1栅极绝缘膜设置在上述n型阱与上述第1栅极电极之间、上述n型阱与上述第2栅极电极之间、上述p型阱与上述第3栅极电极之间、以及上述p型阱与上述第4栅极电极之间。上述第2栅极绝缘膜设置在上述p型阱与上述第5栅极电极之间、以及上述p型阱与上述第6栅极电极之间。上述第1布线连接于上述n型阱、上述第1层以及上述第3层。上述第2布线连接于上述第4层、上述第8层以及上述第1栅极电极。上述第3布线连接于上述第2层、上述第6层以及上述第2栅极电极。上述第4布线连接于上述第5层以及上述第10层。上述第5布线连接于上述第3栅极电极以及上述第5栅极电极。上述第6布线连接于上述第7层以及上述第12层。上述第7布线连接于上述第4栅极电极以及上述第6栅极电极。上述第8布线连接于上述p型阱、上述第9层以及上述第11层。

实施方式的半导体装置具备增强型的第1~第6晶体管。上述第1以及上述第4晶体管是p沟道型。上述第2、第3、第5以及第6晶体管是n沟道型。上述第3晶体管的耐压比上述第2晶体管的耐压低。上述第6晶体管的耐压比上述第5晶体管的耐压低。上述第1晶体管的源极上被施加第1电源电位。上述第2晶体管的漏极连接于上述第1晶体管的漏极,栅极上被输入第1输入信号。上述第3晶体管的漏极连接于上述第2晶体管的源极,源极上被施加比上述第1电源电位低的第2电源电位,栅极上被施加上述第1输入信号。上述第4晶体管的源极连接于上述第1电源电位,漏极连接于上述第1晶体管的栅极,栅极连接于上述第1晶体管的漏极。上述第5晶体管的漏极连接于上述第4晶体管的漏极,栅极上被输入与上述第1输入信号处于互补关系的第2输入信号。上述第6晶体管的漏极连接于上述第5晶体管的源极,源极上被施加上述第2电源电位,栅极上被输入上述第2输入信号。从上述第4晶体管的漏极输出第1输出信号,从上述第1晶体管的漏极输出与上述第1输出信号处于互补关系的第2输出信号。

附图说明

图1是示意地表示实施方式的半导体装置的截面图。

图2是表示实施方式的半导体装置的部分放大截面图。

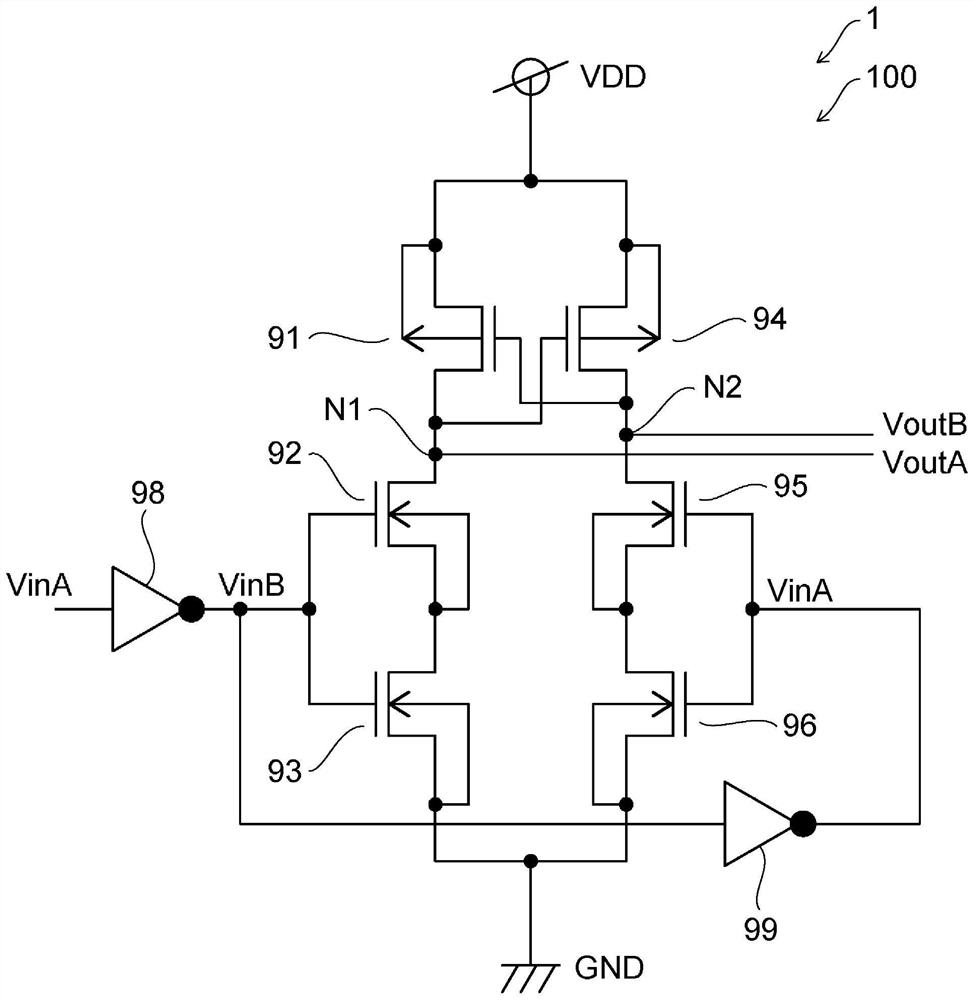

图3是表示形成于实施方式的半导体装置的电平移位电路的电路图。

图4(a)~图4(d)是表示通过电离放射线在栅极绝缘膜形成固定电荷的工序的图。

图5(a)是横轴取栅极电压、纵轴取漏极电流而表示由固定电荷引起的阈值的变化的曲线图,图5(b)是横轴取时间、纵轴取阈值的绝对值而表示阈值的随时间的变化的曲线图。

具体实施方式

以下,对本发明的实施方式进行说明。

图1是示意地表示本实施方式的半导体装置的截面图。

图2是表示本实施方式的半导体装置的部分放大截面图。

如图1所示,本实施方式的半导体装置1中,设有导电型例如为p型的半导体基板10。在半导体基板10上的一部分设有导电型为n型的n型阱11,在半导体基板10上的其他一部分设有导电型为p型的p型阱12。以下的说明中,“p

在p型阱12,设有高耐压区域13以及低耐压区域14。高耐压区域13的杂质浓度与低耐压区域14的杂质浓度相比,相同或低。例如,高耐压区域13配置在n型阱11与低耐压区域14之间。例如,高耐压区域13与n型阱11以及低耐压区域14相接。

在n型阱11上,导电型为p

半导体基板10、n型阱11、p型阱12、p

半导体装置1中,至少形成有第1晶体管91~第6晶体管96这六个晶体管。第1晶体管91~第6晶体管96是增强型的MOSFET(Metal-Oxide-Semiconductor Field-EffectTransistor:金属氧化物半导体场效应晶体管)。

如后述那样,这些晶体管之中的第1晶体管91以及第4晶体管94是设置于n型阱11的p沟道型晶体管。第2晶体管92以及第5晶体管95是设置于p型阱12的高耐压区域13中的n沟道型晶体管。第3晶体管93以及第6晶体管96是设置于p型阱12的低耐压区域14中的n沟道型晶体管。第3晶体管93的耐压比第1晶体管91的耐压以及第2晶体管92的耐压低。第6晶体管96的耐压比第4晶体管94的耐压以及第5晶体管95的耐压低。

p

在p

在n型阱11与p型阱12之间设有STI(Shallow Trench Isolation:元件分离绝缘体)41。此外,在n型阱11上以及p型阱12上,形成有用于将各晶体管相对于周围进行划分的STI。例如,在p

在n

在n型阱11中的p

在p型阱12中的n

如图1以及图2所示,在n型阱11上以及p型阱12的高耐压区域13上,设有栅极绝缘膜61。栅极绝缘膜61至少配置在n型阱11与栅极电极51之间、n型阱11与栅极电极52之间、p型阱12与栅极电极53之间、以及p型阱12与栅极电极54之间。栅极绝缘膜61作为第1晶体管91、第4晶体管94、第2晶体管92、以及第5晶体管95的栅极绝缘膜发挥功能。

在p型阱12的低耐压区域14上设有栅极绝缘膜62。栅极绝缘膜62至少配置在p型阱12与栅极电极55之间、以及p型阱12与栅极电极56之间。栅极绝缘膜62作为第3晶体管93、以及第6晶体管96的栅极绝缘膜发挥功能。

栅极绝缘膜62比栅极绝缘膜61薄。例如,栅极绝缘膜61的厚度t1是栅极绝缘膜62的厚度t2的4倍以上7倍以下。因此,如上所述,第3晶体管93以及第6晶体管96的耐压比第1晶体管91、第4晶体管94、第2晶体管92、以及第5晶体管95的耐压低。栅极绝缘膜61及62例如由硅氧化物等的绝缘材料形成,例如是硅的热氧化膜。在栅极绝缘膜61与栅极绝缘膜62的边界(未图示),形成有由多栅极工序引起的阶差。

在栅极绝缘膜61及62上,以覆盖栅极电极51~56的方式设有层间绝缘膜65。在层间绝缘膜65内设有布线71~78。布线71~78的形状是任意的,例如分别包括沿水平方向延伸的布线部分和沿垂直方向延伸的接触部分。

布线71经由n

布线72连接于p

布线73连接于p

布线74连接于n

布线75连接于栅极电极53以及栅极电极55。布线75被输入输入信号VinB。

布线76连接于n

布线77连接于栅极电极54以及栅极电极56。布线77被输入输入信号VinA。输入信号VinA与输入信号VinB处于互补关系。

布线78经由p

通过上述的结构,在半导体装置1中形成电平移位电路。

图3是表示形成于本实施方式的半导体装置的电平移位电路的电路图。

如图3所示,在形成于半导体装置1的电平移位电路100,设有p沟道型的第1晶体管91、n沟道型的第2晶体管92、n沟道型的第3晶体管93、p沟道型的第4晶体管94、n沟道型的第5晶体管95、以及n沟道型的第6晶体管96。这些晶体管的结构如上所述。这些晶体管全部为增强型。第3晶体管93以及第6晶体管96的耐压比第1晶体管91、第2晶体管92、第4晶体管94、以及第5晶体管95的耐压低。

第1晶体管91、第2晶体管92、以及第3晶体管93串联连接在正的电源电位VDD(第1电源电位)与接地电位GND(第2电源电位)之间,第4晶体管94、第5晶体管95、以及第6晶体管96也串联连接在电源电位VDD与接地电位GND之间。

以下,更详细地说明电平移位电路100的电路结构。

对于第1晶体管91以及第4晶体管94的各沟道(n型阱11),经由布线71以及n

对于第1晶体管91的源极(p

第2晶体管92的漏极(n

第3晶体管93的漏极(n

对于第4晶体管94的源极(p

第5晶体管95的漏极(n

第6晶体管96的漏极(n

此外,在电平移位电路100设有逆变器98以及逆变器99。逆变器98的输出端连接于第2晶体管92的栅极(栅极电极53)、第3晶体管93的栅极(栅极电极55)、以及逆变器99的输入端。逆变器99的输出端连接于第5晶体管95的栅极(栅极电极54)、以及第6晶体管96的栅极(栅极电极56)。

由此,如果向逆变器98的输入端施加输入信号VinA,则由逆变器98以及逆变器99生成处于互补关系的输入信号VinA以及输入信号VinB。输入信号VinB被输入至第2晶体管92的栅极(栅极电极53)以及第3晶体管93的栅极(栅极电极55)。输入信号VinA被输入至第5晶体管95的栅极(栅极电极54)以及第6晶体管96的栅极(栅极电极56)。

从第1晶体管91的漏极(p

例如,输出信号VoutA与输出信号VoutB的电位差的绝对值大于输入信号VinA与输入信号VinB的电位差的绝对值。一例中,输入信号VinA以及VinB的高电平为1.5V,低电平为0V。此外,电源电位VDD为5V。因而,输出信号VoutA以及VoutB的高电平为约5V,低电平为约0V。

接着,对本实施方式的半导体装置1的动作进行说明。

首先,对电平移位动作进行说明。

构成电平移位电路100的第1晶体管91~第6晶体管96全部为增强型,因此在栅极-源极间的电位为零时,成为截止状态。

在输入信号VinA为低电平时,输入信号VinB为高电平,因此n沟道型的第2晶体管92以及第3晶体管93成为导通状态,连接点N1的电位接近接地电位GND。由此,p沟道型的第4晶体管94成为导通状态。此外,通过低电平的输入信号VinA,n沟道型的第5晶体管95以及第6晶体管96成为截止状态。由此,连接点N2的电位接近电源电位VDD,p沟道型的第1晶体管91成为截止状态。其结果,输出信号VoutA的电位成为大致接地电位GND(低电平),输出信号VoutB的电位成为大致电源电位VDD(高电平)。

另一方面,在输入信号VinA为高电平时,n沟道型的第5晶体管95以及第6晶体管96为导通状态。由此,连接点N2的电位接近接地电位GND,p沟道型的第1晶体管91成为导通状态。此外,输入信号VinB成为低电平,因此n沟道型的第2晶体管92以及第3晶体管93成为截止状态。由此,连接点N1的电位接近电源电位VDD,p沟道型的第4晶体管94成为截止状态。其结果,输出信号VoutA的电位成为大致电源电位VDD(高电平),输出信号VoutB的电位成为大致接地电位GND(低电平)。

接着,对由电离放射线带来的影响进行说明。

图4(a)~图4(d)是表示通过电离放射线在栅极绝缘膜形成固定电荷的工序的图。

图5(a)是横轴取栅极电压、纵轴取漏极电流而表示由固定电荷引起的阈值的变化的曲线图,图5(b)是横轴取时间、纵轴取阈值的绝对值而表示阈值的随时间的变化的曲线图。

如图4(a)所示,如果电离放射线R入射到半导体装置1内,则在半导体基板10、n型阱11、p型阱12、p

然后,如图4(b)所示,空穴-电子对再结合。此时,硅部分由于连接于接地电位等外部电位,因此空穴-电子对容易再结合而消失。相对于此,栅极绝缘膜由于是绝缘性的且没有连接于外部电位,因此空穴-电子对难以再结合,空穴以及电子容易残留。

接着,如图4(c)所示,随着电平移位电路100的驱动,如果栅极电极上被施加正电位,则栅极绝缘膜中的电子经由栅极电极被排出至外部。但是,空穴实质上不被排出,残留在栅极绝缘膜中。

此外,如图4(d)所示,栅极电极上被施加正电位,由此栅极绝缘膜中的空穴朝向与硅部分的界面移动,被陷阱点捕获。由此,正的电荷被固定在栅极绝缘膜中。这样,通过重复进行电离放射线R的入射和电平移位电路100的驱动,正的固定电荷被积蓄在栅极绝缘膜中。

其结果,如图5(a)所示,晶体管的阈值变化。例如,在n沟道型晶体管的情况下阈值降低。由此,在输入信号为低电平时,n沟道型晶体管不会完全成为截止状态,电平移位电路100的动作变得不稳定。另一方面,在n沟道型晶体管的情况下阈值上升。

如图5(b)所示,由电离放射线引起的阈值的随时间变化的程度根据晶体管的导电型而不同,还依赖于栅极绝缘膜的膜厚。n沟道型晶体管的阈值的变化量比p沟道型晶体管的阈值的变化量大。此外,n沟道型晶体管中也是栅极绝缘膜越薄,则电荷的捕获量越减少,因此固定电荷难以被积蓄,阈值的变化量小。

本实施方式的半导体装置1中,设置包括厚的栅极绝缘膜61的第2晶体管92和包括薄的栅极绝缘膜62的第3晶体管93,向这些晶体管的栅极输入相同的输入信号VinB。此外,设置包括厚的栅极绝缘膜61的第5晶体管95和包括薄的栅极绝缘膜62的第6晶体管96,向这些晶体管的栅极输入相同的输入信号VinA。

如果从半导体装置1的制造时经过时间而被入射相当量的电离放射线,则包括厚的栅极绝缘膜61的第2晶体管92以及第5晶体管95中阈值降低,在输入信号为低电平时不会充分成为截止状态。但是,包括薄的栅极绝缘膜62的第3晶体管93以及第6晶体管96的阈值不怎么降低,因此在输入信号为低电平时能够实现充分的截止状态。

另外,包括薄的栅极绝缘膜62的第3晶体管93以及第6晶体管96的耐压比包括厚的栅极绝缘膜61的第2晶体管92以及第5晶体管95的耐压低。因此,电平移位电路100中,将包括薄的栅极绝缘膜62的第3晶体管93连接于比包括厚的栅极绝缘膜61的第2晶体管92低电位侧,将包括薄的栅极绝缘膜62的第6晶体管96连接于比包括厚的栅极绝缘膜61的第5晶体管95低电位侧。因此,随着电平移位电路100的驱动,施加于薄的栅极绝缘膜62的电压比施加于厚的栅极绝缘膜61的电压低。由此,能够抑制薄的栅极绝缘膜62绝缘损坏。

像这样,在由第2晶体管92以及第3晶体管93构成的电路整体、以及由第5晶体管95以及第6晶体管96构成的电路整体中,能够确保需要的耐压,并且能够抑制截止状态中的漏电流。此外,关于p沟道型晶体管,电离放射线的影响本来就小。其结果,作为电平移位电路100整体,能够进行抑制了电离放射线的影响的稳定的动作。

此外,本实施方式中,将构成电平移位电路100的第1晶体管91~第6晶体管96全部设为增强型,因此在输入信号VinA为低电平时,能够使第1晶体管91、第5晶体管95、以及第6晶体管96可靠地成为截止状态,并且在输入信号VinA为高电平时,能够使第2晶体管92、第3晶体管93、以及第4晶体管94可靠地成为截止状态。此外,通过将各晶体管设为增强型,即使因电离放射线而阈值有些降低,也能够抑制截止状态中的漏电流的增加。

接着,对本实施方式的效果进行说明。

如上所述,本实施方式中,将构成电平移位电路100的n沟道型晶体管设为包括厚的栅极绝缘膜61的晶体管和包括薄的栅极绝缘膜62的晶体管的二段结构。由此,能够作为电平移位电路100整体而确保耐压,并且抑制由电离放射线引起的阈值的降低,抑制经年恶化。此外,通过由增强型晶体管构成电平移位电路100,能够可靠地实现各晶体管的截止状态,并且抑制由电离放射线引起的漏电流的增加。

根据以上说明的实施方式,能够实现电平移位电路能够长期间稳定地动作的半导体装置。

以上,说明了本发明的实施方式,但该实施方式是作为例子来提示的,并没有要限定发明的范围。该新的实施方式能够以其他多种形态实施,在不脱离发明的主旨的范围内能够进行各种省略、置换、变更。该实施方式及其变形包含于发明的范围及主旨,并且包含于权利要求书所记载的发明及其等价物的范围内。

- 晶体、结晶性氧化物半导体、包含结晶性氧化物半导体的半导体膜、包含晶体和/或半导体膜的半导体装置以及包含半导体装置的系统

- 半导体光发射装置的制造方法、半导体光发射装置、半导体装置的制造方法、半导体装置、一种装置的制造方法、以及一种装置