用于去激活半导体装置中的延迟锁定环更新的设备及方法

文献发布时间:2023-06-19 10:06:57

技术领域

本发明涉及半导体装置。

背景技术

半导体存储器装置,例如DRAM(动态随机存取存储器),包含各自具有安置在字线与位线之间的交叉点处的存储器单元的存储器单元阵列。所述存储器装置还包含延迟锁定环(DLL)以调整外部时钟信号与内部锁相时钟信号之间的锁相电平,使得输入/输出(I/O)驱动器接收与外部时钟信号一起到达的数据。

存储器装置中的各种状况,例如温度、电力供应器中的电压、传播延迟等,可能致使DLL更新电路中的锁相电平变动。例如,可将共同电压供应提供到存储器装置中的存储器单元阵列中的每一者。当发生存储器单元阵列的激活时,对存储器单元阵列的相关联操作可能不利地影响存储器装置的状况,且因此致使DLL更新电路可变地改变锁相电平。然而,存储器装置的某些状况变化可能是显著的以致使DLL更新电路比正常情况更困难地工作。例如,当发生对存储器单元阵列的刷新操作时,共同电力供应器可能由于与存储器刷新操作相关联的显著负载变化而变化。例如,在存储器刷新期间可一次激活八个行(字线)。因此,VDD电压可能降低且VSS电压可能浮动。这个电力供应器变化可能导致DLL更新电路中的锁相电平显著变动。当存储器操作完成时,可能需要时间来将DLL更新电路中的锁相电平调整到所要电平。因而,即使当存储器不处于刷新操作时,对存储器单元阵列的某些动作,例如刷新操作,也可能影响DLL更新的性能。

发明内容

在一个方面,本发明涉及一种设备,其包括:多个存储器单元阵列,每一存储器单元阵列经耦合到输入/输出(I/O)驱动器电路;延迟锁定环(DLL)更新电路,其经配置以将内部时钟提供到所述I/O驱动器电路;及DLL控制电路,其经耦合到所述DLL更新电路且经配置以响应于一或多个存储器单元阵列的激活而去激活所述DLL更新电路。

在另一方面,本发明涉及一种设备,其包括:触发电路,其经配置以至少响应于延迟锁定环(DLL)更新触发或刷新命令变为无效而提供内部更新触发;及DLL控制电路,其经耦合到所述触发电路且经配置以:响应于由所述触发电路提供的所述内部更新触发而激活DLL更新电路;且响应于所述刷新命令变为有效而去激活所述DLL更新电路

在另一方面,本发明涉及一种方法,其包括:接收第一延迟锁定环(DLL)更新触发;响应于所述第一DLL更新触发而激活对多个存储器单元阵列中的一或多者的DLL更新;响应于内部刷新命令的激活而去激活所述DLL更新。

在进一步方面,本发明涉及一种设备,其包括内部时钟生成器电路,其中所述内部时钟生成器电路包括:延迟锁定环(DLL)控制电路,其包括:多个D触发器电路,其串联耦合且经配置以响应于DLL更新触发而提供有效DLL更新信号,其中至少基于所述多个D触发器电路中的D触发器的数目确定所述有效DLL更新信号的持续时间;及输出电路,其经耦合到所述多个D触发器电路,所述输出电路经配置以:当内部刷新命令无效时,传递所述有效DLL更新信号;且当所述内部刷新命令有效时,提供无效DLL更新信号。

附图说明

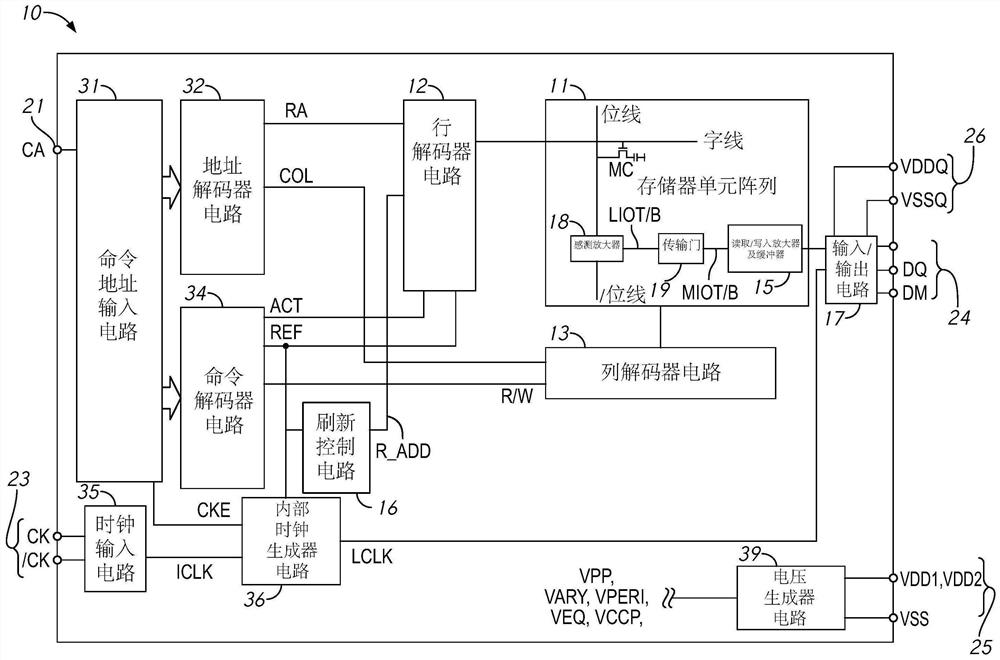

图1是根据本发明中所描述的一些实例的半导体装置的框图。

图2是根据本发明中所描述的一些实例的半导体装置的实例布局的图。

图3是根据本发明中所描述的一些实例的DLL控制电路的图。

图4是根据本发明中所描述的一些实例的DLL控制电路的实例实施方案。

图5是根据本发明中所描述的一些实例的在DLL控制电路的操作期间的各种信号的时序图。

图6是根据本发明中所描述的一些实例的DLL控制电路的另一实施例的图。

图7是根据本发明中所描述的一些实例的在DLL控制电路的操作期间的各种信号的时序图。

具体实施方式

在本发明的一些实施例中,可在激活一或多个存储器单元阵列(例如,进行存储器刷新操作)时去激活DLL的调整。在本发明的一些实施例中,可在DLL的下一调整时间期间调整DLL。在本发明的一些实施例中,可在去激活一或多个存储器单元阵列时调整DLL。

半导体装置可包含耦合到更新触发生成器及DLL更新电路的DLL控制电路。DLL控制电路可从更新触发生成器接收更新触发信号。更新触发信号可包含多个触发(例如,脉冲)。DLL控制电路可响应于更新触发信号中的更新触发而激活DLL更新电路。DLL控制电路可经配置以当激活一或多个存储器单元阵列(例如,存储器刷新操作)时去激活DLL更新电路。DLL更新电路可在被激活时对一或多个存储器单元阵列执行DLL更新且在被去激活时不对所述存储器单元阵列执行DLL更新。在一些实施例中,一旦去激活DLL更新电路,DLL更新电路就保持去激活直到更新触发信号中的下一更新触发到达为止。在其它实施例中,一旦去激活一或多个存储器单元阵列(例如,对一或多个存储器单元阵列的刷新操作完成),DLL控制电路就可重新激活DLL更新电路。

图1是根据本发明中所描述的一些实例的半导体装置10的框图。在本发明的一些实施例中,半导体装置10可为动态随机存取存储器(DRAM)。半导体装置10包含存储器单元阵列11。存储器单元阵列11包含彼此交叉的多个字线WL及多个位线BL,其中存储器单元(MC)经安置在交叉点处。字线WL的选择由行解码器电路12实行,且位线BL的选择由列解码器电路13实行。

进一步参考图1,感测放大器18经耦合到对应位线BL且经耦合到本地I/O线对LIOT/B。本地IO线对LIOT/B经由传输门TG 19耦合到主IO线对MIOT/B,传输门TG19用作读取/写入放大器及缓冲器15的开关。转向半导体装置10中包含的多个外部端子的解释,多个外部端子包含命令及地址端子21、时钟端子23、数据端子24及电力供应器端子25及26。

向命令及地址端子21供应命令及地址信号CA。提供到命令及地址端子21的CA信号包含命令及地址。CA信号中包含的地址经由命令/地址输入电路31传输到地址解码器电路32。地址解码器电路32接收所述地址且将经解码行地址信号RA供应到行解码器电路12,且将经解码列地址信号COL供应到列解码器电路13。

提供到命令及地址端子21的CA信号中包含的命令经由命令/地址输入电路31输入到命令解码器电路34。命令解码器电路34对命令进行解码以提供各种内部命令信号。例如,内部命令可包含用于选择字线的行命令信号及用于选择位线的列命令信号。

当发出行激活命令且及时向行地址供应激活命令并及时向列地址供应读取命令时,从由这些行地址及列地址指定的存储器单元阵列11中的存储器单元MC读取读取数据。更具体来说,行解码器电路12选择由行地址RA指示的字线WL使得相关联存储器单元MC随后连接到位线BL。读取数据DQ经由读取/写入放大器15及输入/输出电路17从数据端子24输出到外部。类似地,当发出行激活命令且及时向行地址供应激活命令并及时向列地址供应写入命令时,输入/输出电路17可在数据端子24处接收写入数据DQ。写入数据DQ经由输入/输出电路17及读取/写入放大器15供应到存储器单元阵列11且写入由行地址及列地址指定的存储器单元MC中。

装置10可包含用于实行刷新操作的刷新控制电路16。在刷新操作期间,可刷新与一或多个字线相关联的存储器单元。字线的刷新可被称为刷新,且刷新操作可包含多个刷新。刷新操作可为自动刷新操作及/或其它刷新操作。在一些实施例中,刷新命令可从外部发布到装置10且提供到命令解码器电路34,命令解码器电路34将所述命令提供到刷新控制电路16及行解码器电路12。在一些实施例中,可由装置10的组件(例如,由刷新控制电路16或命令解码器电路34在内部)周期性地提供刷新命令。刷新控制电路16可将刷新地址R_ADD提供到行解码器电路12,所述刷新地址R_ADD可指示用于执行刷新操作的行地址。如将更详细地描述,在刷新操作期间可跨多个存储器垫及/或存储器组刷新由刷新地址R_ADD指示的字线(例如,子字线)。

向时钟端子23分别供应外部时钟信号CK及/CK。这些外部时钟信号CK及/CK彼此互补且供应到时钟输入电路35。时钟输入电路35接收外部时钟信号CK及/CK且提供内部时钟信号ICLK。将内部时钟信号ICLK供应到内部时钟生成器36且因此基于所接收的内部时钟信号ICLK及来自命令/地址输入电路31的时钟启用信号CKE提供相控内部时钟信号LCLK。作为非限制性实例,DLL电路可包含在内部时钟生成器36中。相控内部时钟信号LCLK经供应到输入/输出电路17且用作用于确定读取数据DQ的输出时序的时序信号。

在一些实例中,内部时钟生成器36可包含耦合到DLL更新电路的DLL控制电路。可向DLL控制电路提供来自更新触发生成器(例如,CLK输入电路35或内部时钟生成器36内部的振荡器)的更新触发信号。更新触发信号可包含周期性地到达的多个触发(例如,脉冲)。可将更新触发信号提供到DLL控制电路以激活半导体装置的DLL更新电路。DLL更新电路可经配置以通过考虑所述电路中的各种延迟来执行DLL更新且提供相控内部时钟信号LCLK来控制何时提供IO电路17的输入/输出(I/O)驱动器处的数据的时序。

在一些实例中,还可向内部时钟生成器电路36中的DLL控制电路提供内部刷新信号(例如,刷新命令)。可响应于更新触发周期性地执行DLL更新,而独立于存储器单元的激活(例如,刷新命令)提供更新触发。DLL控制电路可经配置以响应于有效刷新信号(例如,处于高逻辑电平)而去激活正在进行的DLL更新。在一些实例中,一旦响应于内部刷新信号而去激活DLL更新,就可在内部刷新信号变为无效(例如,处于低逻辑电平)时再次激活DLL更新。在其它情况下,一旦去激活DLL更新,DLL更新就可保持去激活直到下一更新触发为止。

向电力供应器端子25供应电力供应电压VDD1、VDD2(统称为VDD)及VSS。将这些电力供应电压VDD1、VDD2及VSS供应到内部电压生成器电路39。内部电压生成器电路39提供各种内部电压VPP、VARY、VPERI、VEQ及VCCP。

内部电势VCCP是主要在行解码器电路12中使用的电势。内部电势VARY及VEQ是将由感测放大器18、传输门19及/或读取/写入放大器15使用的电势。当激活感测放大器18时,通过将成对位线中的一者驱动到VARY电平且将另一者驱动到VSS电平来放大经读出读取数据。内部电势VPERI用作例如命令/地址输入电路31的大多数外围电路的电力供应器电势。通过使用具有比外部电势VDD低的电势的内部电势VPERI作为这些外围电路的电力供应器电势,可降低半导体装置10的功耗。

向电力供应器端子26供应电力供应电压VDDQ及VSSQ。将这些电力供应电压VDDQ及VSSQ供应到输入/输出电路17。电力供应电压VDDQ及VSSQ可为分别与供应到电力供应器端子25的电力供应电压VDD2及VSS相同的电压。然而,专用电力供应电压VDDQ及VSSQ可用于输入/输出电路17使得由输入/输出电路17生成的电力供应噪声不会传播到装置10的其它电路块。

图2是根据本发明的实施例的半导体装置200的存储器单元阵列的实例布局的图。在本发明的一些实施例中,半导体装置200包含由阵列控制器204控制的多个存储器阵列202(1)、202(2)、…、202(N)。存储器阵列可包含在存储器单元阵列11中(在图1中)。阵列控制器204可包含在半导体装置10中的电路中,例如行解码器电路12、列解码器电路13、地址解码器电路32、命令解码器电路34(图1)或其它电路。通过共同VDD及VSS线向存储器阵列202(1)、…、202(N)及阵列控制器204提供电源电压。通过VDD电力供应器210及VSS电力供应器212分别向VDD线及VSS线提供电源电势VDD及VSS。在一些实例中,VDD电力供应器210及VSS电力供应器212可包含在电压生成器电路39中(图1)。

半导体装置200可进一步包含DLL控制电路208。在一些实例中,可向DLL控制电路208提供来自更新触发生成器206(例如,振荡器)的更新触发信号。更新触发信号中的多个更新触发可致使DLL控制电路208周期性地激活半导体装置的DLL更新电路(未展示)。DLL更新电路可经配置以通过考虑所述电路中的各种延迟且在系统时钟(例如,图1中的ICLK)与相控内部时钟信号(例如,图1中的LCLK)之间提供相位同步以控制何时提供存储器单元阵列的输入/输出(I/O)驱动器处的数据的时序来执行DLL更新。

在一些实例中,还可向DLL控制电路208提供内部刷新信号(例如,刷新命令)。可响应一或多个更新触发周期性地执行DLL更新,而独立于存储器单元的激活(例如,刷新)提供更新触发。在一些情况下,DLL更新正在进行且刷新信号变为有效从而指示刷新操作。在此情况下,DLL控制电路208可经配置以响应于有效刷新信号而去激活DLL更新。在一些实例中,一旦由于刷新信号而去激活DLL更新,就可在内部刷新信号变得无效时再次激活DLL更新。在其它情况下,一旦去激活DLL更新,DLL更新就可保持去激活直到下一更新触发到达为止。参考图3到7描述DLL控制电路208的进一步细节。

图3是根据本发明中所描述的一些实例的DLL控制电路的图。在一些实例中,DLL控制电路300可经耦合到DLL更新电路302且经配置以将DLL更新信号提供到DLL更新电路。DLL控制电路300可包含更新定序器308,更新定序器308经配置以从更新触发生成器306接收更新触发信号,且提供DLL更新信号以响应于更新触发信号中的更新触发而激活DLL更新电路302。在一些实例中,更新触发生成器可为经配置以生成多个更新触发的振荡器。每一更新触发可包含脉冲。换句话说,更新触发信号可包含多个脉冲。

在一些实例中,DLL更新电路302可在内部时钟生成器电路(例如,图1中的36)中实施且经配置以提供相控内部时钟信号LCLK,所述相控内部时钟信号LCLK经提供到I/O驱动器304以将数据馈送到存储器单元阵列/从存储器单元阵列读取数据。在一些实例中,DLL更新电路302可包含经配置以基于内部时钟ICLK将相变提供到LCLK的可调延迟线56。DLL更新电路302还可包含延迟控制逻辑54,延迟控制逻辑54经耦合到可调延迟线56且经配置以将相位值提供到可调延迟线56以控制所述可调延迟线的延迟量。

在一些实例中,DLL更新电路302可包含相位检测电路58,相位检测电路58经配置以比较内部时钟CLK与通过副本/模型延迟电路52提供的相控内部时钟LCLK之间的相位。将比较结果提供到延迟控制逻辑54以将相位值提供到可调延迟线56。在一些实例中,副本/模型延迟电路52可考虑从可调延迟线56的输出到I/O驱动器304的进一步延迟。进一步延迟可由所述电路中的传播、时钟树延迟及/或其它可能延迟引起。可在副本/模型延迟电路52中对这些可能延迟进行建模。因而,当由延迟线56提供的LCLK中的经调整延迟已到达I/O驱动器304时,其将与内部时钟ICLK对齐以促进存储器单元阵列中的准确数据操作(读取/写入)。

在一些实例中,DLL更新电路302可包含经配置以激活/去激活DLL更新电路的激活电路50。激活电路50可包含具有耦合到可调延迟线56的输出的输入端子的AND门。激活电路50的第二输入端子可经耦合到DLL控制电路以接收DLL更新信号。激活电路50可经耦合到副本/模型延迟电路52。当DLL更新信号有效(例如,处于高逻辑电平)时,激活电路50可将可调延迟线56的输出传递到副本/模型延迟电路52。当DLL更新信号无效(例如,处于低逻辑电平)时,激活电路50可阻断可调延迟线56的输出,而替代地将无效信号(例如,低逻辑电平)提供到副本/模型延迟电路52。

在一些实例中,DLL更新电路302中的延迟控制逻辑54也可经耦合到DLL控制电路以接收DLL更新信号。延迟控制逻辑54可经配置以响应于无效DLL更新信号(例如,低逻辑电平)而被去激活,使得在可调延迟线56中将不存在进一步延迟调整。当DLL更新信号变为有效(例如,切换到高逻辑电平)时,可再次激活延迟控制逻辑54。图3中的各种组件仅是DLL更新电路的实例实施方案。其它实施方案也是可能的。

进一步参考图3,更新定序器308可经配置以接收更新触发信号及存储器单元阵列的激活信号,且提供DLL更新信号以响应于更新触发信号而激活DLL更新电路,且响应于存储器单元阵列的激活而去激活DLL更新电路。在一些实例中,存储器单元阵列的激活信号可为刷新命令。更新定序器308还可经耦合到CLK输入电路(例如,图1中的35)以经由缓冲器60接收内部时钟,例如ICLK。

图4是根据本发明中所描述的一些实例的DLL控制电路的实例实施方案。在一些实例中,电路400实施更新定序器(例如,图3中的308)。电路400可包含串联耦合的一系列D触发器,例如402(1)、…、402(5),其中串联耦合的多个触发器中的触发器的Q输出经耦合到后一触发器的时钟输入。向第一触发器(例如,402(1))的时钟输入提供时钟。例如,在其中电路400包含在更新定序器308中的发明中,经由缓冲器60向第一触发器的时钟输入提供时钟ICLK。对于多个触发器(例如,402(1)到402(4))中的触发器中的每一者,但最后一个触发器(402(5))除外,Q输出经由反相缓冲器环回到输入端子。例如,触发器402(1)的输出经由反相缓冲器406(1)循环到输入端子。触发器402(2)、402(3)及402(4)分别经由反相缓冲器406(2)、406(3)及406(4)以类似方式配置。最后一个触发器(例如,402(5))的输入端子经耦合到接地。电路400可进一步包含经配置以提供DLL更新信号的输出电路408。在一些实例中,输出电路408可包含具有两个输入的AND门。

如图4中所展示,起始信号线可在置位端子处耦合到多个触发器中的触发器中的每一者,且停止信号线可在复位端子处耦合到每一触发器。可将来自更新触发生成器(例如,图2中的206、图3中的306)的更新触发信号提供到起始信号线。可将存储器激活信号(例如,刷新命令)提供到停止信号线。响应于有效起始信号(例如,更新触发脉冲),可将所有触发器402置位为高逻辑电平,例如值1。在停止信号无效(例如,处于低逻辑电平)时,通过输出电路408传递最后一个触发器402(5)的输出处的信号Out以提供DLL更新信号。每一D触发器的输出处的高逻辑电平由每一相应触发器锁存且仅在上升时钟边缘到达时才可变化(变为低逻辑电平)。因为触发器402(2)、402(3)、402(4)及402(5)中的每一者的时钟端子经耦合到前一触发器的输出端子,所以每一锁存电路402(2)到402(5)处提供的输出改变值所需要的时间可为前一触发器的两倍。例如,在每一脉冲之后,更新触发信号(在起始信号线处)变为低逻辑电平,D触发器402(1)的输出在时钟信号的每个时钟循环处使其值交替。换句话说,触发器402(1)的输出将需要两个时钟循环来完成从高逻辑值到低逻辑值并返回到高逻辑值的完整循环。

进一步参考图4,因为将触发器402(1)的输出馈送到后一触发器402(2)的时钟端子中,所以后一继触发器402(2)的输出在时钟信号的每两个时钟循环处使其值交替。类似地,触发器402(3)的输出在每四个时钟循环处使值交替,触发器402(4)的输出在每八个时钟循环处使值交替,且来自最后一个触发器402(5)的输出信号Out在时钟信号的第八时钟循环完成时从高逻辑电平变为低逻辑电平(因为输入D经耦合到接地)。因此,Out信号(传递到DLL更新)对应于更新触发信号中的脉冲,但是具有更大宽度。图4中展示仅五个触发器,然而,取决于DLL更新信号的所要宽度,可使用更少或更多触发器来提供DLL更新。

在一些实例中,当停止信号线上的激活信号(例如,刷新命令)变为有效(例如,从低逻辑电平变为高逻辑电平)时,多个D触发器402(1)到402(5)中的每一者变为无效(例如,处于低逻辑电平)。因此,输出电路408将通过AND门408的反相输入提供输出DLL更新信号作为低逻辑电平信号。这有效地去激活DLL更新电路(例如,图3中的302)。

图5是根据本发明中所描述的一些实例的在DLL控制电路的操作期间的各种信号的时序图。在一些实例中,DLL控制电路300(在图3中)及/或DLL控制电路400(在图4中)可如参考图5所描述那样操作。图5将作为实例参考图3及4的DLL更新控制电路进行描述。

在操作中,更新触发信号可包含多个触发(例如,脉冲),例如在时间T0及T3的脉冲。如图3中所展示,可由更新触发生成器306(例如,振荡器)提供更新触发信号。生成更新触发信号的其它方法也可为可用的。响应于更新触发信号中的每一脉冲,参考图4,多个串联耦合D触发器(例如,402(1)、…、402(5))可经配置以生成DLL更新信号作为在时间T1的更宽脉冲。DLL更新信号的宽度可由串联耦合的多个D触发器中使用的D触发器的数目控制(参见图4)。换句话说,可使用更少或更多触发器来将DLL更新信号的宽度配置为所要宽度。

参考图3,DLL更新脉冲通过激活电路50提供到副本/模型延迟电路52。响应于DLL更新信号在时间T1变为有效,激活DLL更新电路302,且副本/模型延迟电路52提供副本时钟信号(如图5中所展示),所述副本时钟信号经提供到相位检测电路58以比较如参考图3所描述的相位。在图5的实例中,由延迟控制逻辑54提供的相位值(锁相电平)在DLL更新时间期间变化以调整可调延迟线56,其被展示为锁相电平从高于锁定电平变为低于锁定电平并再次变化。

返回到图5,更新触发信号中的下一脉冲可在时间T3到达。类似地,DLL更新信号在时间T4变为有效,其中DLL更新信号中的脉冲的宽度由更新定序器308控制且参考图4进行详细描述。在时间T5,存储器单元阵列变为有效。例如,在T5激活内部刷新命令(例如,如由上升边缘所指示)。内部刷新信号经提供到更新定序器(图3中的308)的停止端子及串联耦合触发器(例如,图4中的触发器402)的复位端子。如图4中所描述,内部刷新信号的激活致使DLL更新信号的输出无效(例如,处于低逻辑电平)。如图5中所展示,DLL更新信号响应于有效内部刷新信号在时间T6变为无效。与在时间T1的DLL更新信号相比,DLL更新信号的脉冲宽度响应于内部刷新命令的激活而减小。DLL更新信号的去激活可能致使DLL更新电路去激活(例如,去激活图3中的激活电路50及延迟控制逻辑54),直到下一更新触发到达为止。

进一步参考图5,响应于内部刷新信号的激活,电力供应器VDD或VSS可能由于电路负载变化而变化。在一些实例中,内部刷新信号的激活可能致使电压电势VDD降低且电压电势VSS浮动。通过在T6切断DLL更新,锁相电平(例如,图3中的延迟控制逻辑54的输出)将保持恒定。这可能由于存储器单元阵列的激活(例如,内部刷新命令)而有效地隔离VDD/VSS的影响,使得DLL更新受到最小影响。如图5中所述,一旦DLL更新信号变为无效(例如,低逻辑电平),DLL更新信号就将保持无效直到下一有效更新触发为止。换句话说,一旦DLL更新电路经去激活,其就将保持去激活直到下一有效更新触发为止。

图6是根据本发明中所描述的一些实例的DLL控制电路的另一实施例的图。在一些实例中,DLL控制电路600可经配置以响应于更新触发而去激活DLL更新电路且所述去激活持续达刷新命令的持续时间。例如,可在内部刷新信号变为无效时再次激活DLL更新电路602。当存储器刷新操作完成时(此时刷新操作对VDD/VSS的影响将减弱),DLL更新电路可经配置以再次激活。现在,进一步解释DLL控制电路600的实施例的细节。

在一些实例中,DLL控制电路600可包含经配置以提供DLL更新信号的更新定序器608。DLL控制电路600可进一步包含耦合到更新触发生成器606及更新定序器608的触发电路622。更新触发生成器606(例如,振荡器)可经配置以生成更新触发信号。更新触发信号可包含提供到触发电路622的多个激活脉冲。触发电路622还可经耦合到内部刷新命令线且经配置以提供内部更新触发信号(例如更新触发2信号),所述内部更新触发信号经提供到更新定序器608。与更新触发信号类似,内部更新触发信号(例如,更新触发2)可包含多个触发(例如,脉冲)。更新定序器608可以与更新定序器308(在图3中)类似的方式配置且经耦合到更新触发生成器606,不同之处在于触发电路622经耦合在更新触发生成器606与更新定序器608之间以提供内部更新触发信号更新触发2。

进一步参考图6,在一些实例中,触发电路622可包含逻辑门614,逻辑门614组合两个信号以提供内部更新触发信号,例如更新触发2。在一些实例中,逻辑门614可为具有分别耦合到脉冲生成器624及更新触发生成器606的两个输入的OR门。在一些实例中,更新触发生成器606可以与更新触发生成器306(在图3中)类似的方式配置。例如,更新触发生成器606可为振荡器。更新触发信号可包含多个脉冲。所述脉冲中的每一者传递通过逻辑门614以在更新触发2信号中提供相应脉冲。更新触发2信号进一步提供到更新定序器608。与在本发明中参考图3所描述的内容类似,更新定序器608可生成DLL更新信号,例如响应于从更新触发生成器606提供的脉冲的延迟脉冲。

另外及/或替代地,脉冲生成器624可经耦合到DLL控制电路600的输出以接收DLL更新信号。脉冲生成器624可包含经配置以锁存更新触发信号且在输出处提供存储更新信号的锁存电路610,所述存储更新信号进一步提供到组合器电路612的第一输入。存储更新信号通过延迟电路616进一步提供到组合电路612的第二输入。

在一些实例中,锁存电路610可为RS触发器,其中置位端子经耦合到置位电路626且复位端子经耦合到复位电路628。置位电路626也可经耦合到内部刷新命令线。在一些实例中,置位电路626可包含AND门,所述AND门经配置以从DLL控制电路600接收DLL更新信号及从内部刷新命令线接收内部刷新信号且提供存储置位脉冲。触发电路622还可包含复位电路628。复位电路628可经耦合到内部刷新命令线以接收内部刷新信号且将存储复位脉冲提供到RS触发器电路610的复位端子。在此配置中,更新触发信号中的脉冲将致使触发电路622在更新触发2信号中提供脉冲。更新触发2信号中的有效脉冲可致使DLL控制电路600提供有效DLL更新信号(例如,处于高逻辑电平)。当DLL更新信号有效时(在更新触发信号中的后续脉冲到达之前),无效内部刷新信号(例如,处于低逻辑电平)致使置位电路626以低逻辑电平提供存储置位信号直到内部刷新信号变为有效(例如,从低逻辑电平切换到高逻辑电平)为止。此时,置位电路626的输出处的存储置位信号切换到逻辑高电平直到DLL更新信号变为无效(例如,切换到逻辑低电平)为止。响应于存储置位信号中的脉冲,RS触发器电路610的输出处的存储更新从低逻辑电平切换到高逻辑电平。

在一些实例中,组合器电路612是其中第一反相输入的AND门。在此情况下,当组合存储更新信号中的反相脉冲(例如,处于低逻辑电平)与存储更新信号中的延迟脉冲(例如,处于高逻辑电平)时,经组合存储触发信号是跟在存储更新信号的下降边缘之后的脉冲,其中所述脉冲的宽度由延迟电路616中的延迟控制。因此,更新触发2信号经提供为跟在存储更新信号的下降边缘之后的脉冲。复位电路628可以与脉冲生成器624类似的方式配置且经配置以响应于有效内部刷新信号(例如,处于高逻辑电平)而在存储复位信号中生成脉冲。存储复位信号中的脉冲可能致使RS触发器电路610的输出复位,这可能致使存储更新信号变为无效(例如,处于逻辑低电平)。存储更新信号的这个下降边缘可在存储触发信号及更新触发2信号中提供脉冲。

总的来说,响应于由更新触发生成器606提供的更新触发脉冲或响应于内部刷新信号的下降边缘而提供更新触发2信号中的脉冲。这个更新触发2信号有效地充当更新定序器608的更新触发信号。更新定序器608以与更新定序器308(在图3及4中)类似的方式配置及操作且响应于更新触发2信号中的脉冲而提供DLL更新脉冲信号。与DLL控制电路(图3中的300)类似,DLL控制电路600还提供DLL更新信号以激活或去激活DLL更新电路602,其中DLL更新信号(脉冲)的上升边缘激活DLL更新电路且DLL更新信号(脉冲)的下降边缘去激活DLL更新电路。DLL更新电路602可以与DLL更新电路302(图3)类似的方式配置。DLL更新电路的其它配置也是可能的。

图7是根据本发明中所描述的一些实例的在DLL更新控制电路的操作期间的各种信号的时序图。在一些实例中,图6的DLL更新控制电路可如参考图7所描述那样操作。图7将作为实例参考图6的DLL更新控制电路进行描述。

在操作中,更新触发信号可包含多个触发(例如,脉冲),例如在时间T0及T3的脉冲。如图6中所展示,更新触发信号可由更新触发生成器606(例如,振荡器)提供。生成更新触发信号的其它方法也可为可用的。如同图3,图4中的电路400也可为图6中的更新定序器608的实例实施方案。参考图4,响应于更新触发信号中的每一脉冲,多个串联耦合D触发器(例如,402(1)、…、402(5))可经配置以在时间T1将DLL更新信号生成为(比更新触发的脉冲宽度)更宽的脉冲。DLL更新的宽度可由串联耦合的多个D触发器中包含的D触发器的数目控制(参见图4)。换句话说,可使用更少或更多触发器来将DLL更新信号的宽度配置为所要宽度。

参考图6,DLL更新脉冲通过激活电路50提供到副本/模型延迟电路52。响应于有效DLL更新信号,激活DLL更新电路602,且副本/模型延迟电路52生成对应副本时钟(如图7中所展示),所述副本时钟经提供到相位检测电路58以比较如参考图3及6所描述的相位。

返回到图7,更新触发信号中的下一脉冲可在时间T3到达。类似地,由DLL控制电路(例如,图6中的600)提供的DLL更新信号在时间T4变为有效脉冲,其中所述脉冲的宽度由更新定序器608控制且参考图4进行详细描述。此时,RS触发器电路(图6中的610)的置位端子由于置位电路626(在图6中)而变为无效,这致使RS触发器提供低逻辑电平电压。在时间T5,存储器单元阵列的激活已到达。例如,在T5(例如,在上升边缘)激活内部刷新命令。将内部刷新命令提供到更新定序器(图6中的608)的停止端子,例如串联耦合触发器(例如,图4中的D触发器402)的复位端子。如图4中所描述,内部刷新命令的激活致使DLL更新的输出无效(例如,处于低逻辑电平)。如图7中所展示,DLL更新信号在时间T6变为无效。无效DLL更新信号将去激活DLL更新电路(例如,通过去激活图6中的激活电路50及延迟控制逻辑54),直到下一更新触发(例如,更新触发2)为止。此外,响应于内部刷新信号的激活,置位电路(图6中的626)提供有效脉冲,所述有效脉冲触发存储更新信号使其变为有效(例如,从低逻辑电平切换到高逻辑电平)。存储更新信号保持有效直到内部刷新信号失效为止。

进一步参考图7,内部刷新命令在时间T7变为无效(例如,从高逻辑电平切换到低逻辑电平)。这致使复位电路(图6中的628)在存储复位信号中提供脉冲,其随后致使存储更新信号变为无效。响应于存储更新信号变为无效(例如,从高逻辑电平切换到低逻辑电平),脉冲生成器624在时间T8在存储触发信号中提供脉冲。这有效地在更新触发2信号中提供脉冲,其致使DLL控制电路在时间T9提供有效DLL更新信号。有效DLL更新信号随后重新激活DLL更新电路(例如,图6中的602)。如上所述,DLL更新电路的激活不等待由更新触发生成器(例如,图6中的606)提供的更新触发信号(例如,更新触发)中的下一脉冲。相反,DLL更新电路的激活(重新激活)是响应于内部刷新命令的下降边缘。换句话说,在内部刷新命令的持续时间内去激活DLL更新电路。

进一步参考图7,响应于内部刷新信号的激活,电力供应器VDD或VSS可能由于电路负载变化而变化。在一些实例中,内部刷新信号的激活可能致使电压电势VDD降低且电压电势VSS浮动。通过在T6切断DLL更新,锁相电平(例如,图3中的相位检测电路58的输出)将停止调整。这可由于存储器单元阵列的激活(例如,内部刷新信号)而有效地隔离VDD/VSS的影响且使得DLL更新受到最小影响。如图7中所述,一旦DLL更新信号变为无效(例如,低逻辑电平),DLL更新信号就将保持无效直到对存储器单元阵列完成刷新操作为止。换句话说,一旦去激活DLL更新电路,其就将保持去激活直到完成存储器的刷新操作为止。

从前述内容将明白,尽管本文中已出于说明目的而描述本发明的特定实施例,但是可在不脱离本发明的精神及范围的情况下进行各种修改。例如,也可在存储器的其它激活(例如ACT、READ及/或WRITE命令的激活)后去激活DLL更新。因此,本发明的范围不应限于本文中所描述的特定实施例中的任一者。

参考图1到7所描述的各种实施例提供优于现存系统的优点,其中响应于某些存储器操作(例如,刷新操作)的激活而去激活对一或多个存储器单元阵列的DLL更新。这会在某些存储器操作期间最小化对DLL更新的影响,这有助于在这些存储器操作完成之后将DLL更新电路中的锁相水平维持在所要范围内。因而,某些存储器操作,例如刷新操作,在刷新操作完成之后可能不会不利地影响DLL更新的性能。

下文阐述某些细节以提供对本发明的各种实施例的实例的充分理解。然而,应明白,可在没有这些特定细节的情况下实践本文中所描述的实例。此外,本文中所描述的本发明的特定实例不应被解释为将本发明的范围限于这些特定实例。在其它情况下,未详细展示熟知电路、控制信号、时序协议及软件操作以免不必要地模糊本发明的实施例。另外,例如“耦合(couples及coupled)”的术语表示两个组件可直接或间接电耦合。间接耦合可能暗示两个组件通过一或多个中间组件耦合。

- 用于去激活半导体装置中的延迟锁定环更新的设备及方法

- 用于激活和去激活安全系统中的视频摄像机的方法和装置