一种驱动电路的控制开关、阵列基板和显示面板

文献发布时间:2023-06-19 11:19:16

技术领域

本申请涉及显示技术领域,尤其涉及一种驱动电路的控制开关、阵列基板和显示面板。

背景技术

目前,显示技术被广泛应用于电视、手机以及公共信息的显示,用于显示画面的显示面板也多种多样,而且可以显示丰富多彩的画面。越来越多的显示面板,例如薄膜晶体管液晶显示面板(Thin Film Transistor-Liquid Crystal Display,简称TFT-LCD),有机发光显示面板(Organic Light Emitting Diode,简称OLED)等,都需要利用阵列基板行驱动(Gate Driver on Array,简称GOA)技术,将阵列基板行驱动电路集成在显示面板中的阵列基板上,形成对显示面板的扫描驱动,从而可以从材料成本和制作工艺两方面降低产品成本。

通常在制作GOA电路时,将薄膜晶体管中的源极、漏极与源极引线同层设置且同时蚀刻形成,但是在进行蚀刻工艺时容易出现蚀刻不均匀的问题;而且随着GOA电路的集成度越来越高,使得源极和漏极之间的沟道间距越来越小,因此当蚀刻不均匀时,容易导致源极引线同时与源极、漏极连接,使得源极和漏极发生短路。

发明内容

本申请的目的是提供一种驱动电路的控制开关、阵列基板和显示面板,防止驱动电路在蚀刻不均匀时导致源极和漏极短路。

本申请公开了一种驱动电路的控制开关,所述控制开关包括薄膜晶体管,所述驱动电路还包括与所述薄膜晶体管连接的源极引线,所述薄膜晶体管包括源极、漏极和栅极,所述源极包括至少两个并列设置的源极分支,以及连接各个所述源极分支的源极主干,且与所述源极引线直接连接的所述源极分支为第一源极分支,所述第一源极分支与所述源极主干的端部连接;所述漏极与所述源极同层设置,包括至少一个漏极分支,以及连接各所述漏极分支的漏极主干,所述漏极分支与所述源极分支并列且交替设置以形成沟道,且与所述第一源极分支相邻设置的所述漏极分支为第一漏极分支;所述栅极与所述源极、漏极对应设置;其中,所述源极引线的延长线位于所述第一漏极分支和所述源极主干之间。

可选的,所述薄膜晶体管与两条所述源极引线连接,所述第一源极分支的数量有两条,两条所述第一源极分支分别连接到所述源极主干的两端,且与两条所述源极引线一一对应连接;所述第一漏极分支位于两条所述第一源极分支之间,两条所述源极引线的延长线均位于所述第一漏极分支和所述源极主干之间,且不与所述第一漏极分支重叠。

可选的,不与所述源极引线直接连接的所述源极分支为第二源极分支,且所述第二源极分支并列设置在两条所述第一源极分支之间,与所述源极主干连接;不与所述第一源极分支相邻设置的所述漏极分支为第二漏极分支,所述第一漏极分支的数量有两条,且两条所述第一漏极分支分别与所述漏极主干的两端连接,所述第二漏极分支并列设置在两条所述第一漏极分支之间,与所述漏极主干连接;所述第一漏极分支设置在相邻所述第一源极分支和所述第二源极分支之间,所述第二漏极分支设置在相邻两条所述第二源极分支之间;当所述第二源极分支的数量只有一条时,所述第二漏极分支的数量为零。

可选的,两条所述源极引线位于同一直线上。

可选的,所述薄膜晶体管与一条所述源极引线连接,所述第一源极分支的数量只有一条;不与所述源极引线直接连接的所述源极分支为第二源极分支,所述第二源极分支的数量至少有一条;所述第一漏极分支设置在所述第一源极分支和所述第二源极分支之间,所述源极引线的延长线位于所述第一漏极分支和所述源极主干之间,且不与所述第一漏极分支重叠。

可选的,不与所述第一源极分支相邻设置的所述漏极分支为第二漏极分支,所述第二漏极分支的数量至少有一条,所述第一漏极分支和一条所述第二漏极分支分别与所述漏极主干的两端连接;所述第二漏极分支设置在相邻两条所述第二源极分支之间。

可选的,所述第二漏极分支与所述源极主干之间的距离,小于所述第一漏极分支与所述源极主干之间的距离。

可选的,所述第二漏极分支与所述第一漏极分支的长度之差,和所述源极引线的宽度相等;其中,所述第一漏极分支、第二漏极分支的长度方向为所述第一漏极分支、第二漏极分支的延伸方向。

本申请还公开了一种阵列基板,包括如上所述的驱动电路,以及被所述驱动电路驱动的扫描线。

本申请还公开了一种显示面板,包括如上所述的阵列基板,与所述阵列基板相对设置的彩膜基板,以及设置在所述阵列基板和彩膜基板之间的液晶层。

本申请通过对驱动电路中薄膜晶体管和源极引线进行改进,使得源极引线的延长线位于第一漏极分支和所述源极主干之间,且不与漏极分支重叠;当对源极、漏极和源极引线所在的膜层进行蚀刻时,即使存在蚀刻不均匀的问题,导致源极引线的顶部突出于第一源极分支,其突出位置也只会延伸到第一漏极分支和所述源极主干之间,不会与第一漏极分支相交,因此不会导致源极和漏极短路。

附图说明

所包括的附图用来提供对本申请实施例的进一步的理解,其构成了说明书的一部分,用于例示本申请的实施方式,并与文字描述一起来阐释本申请的原理。显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。在附图中:

图1是一种阵列基板的平面示意图;

图2是图1中M位置的局部放大图;

图3是一种示例性的GOA局部示意图;

图4是另一种示例性的GOA局部示意图;

图5是基于图3在理想状态下的示意图;

图6是基于图4在理想状态下的示意图;

图7是本申请一实施例提供的含有第一种类型薄膜晶体管的驱动电路的局部示意图;

图8是本申请一实施例提供的含有第二种类型薄膜晶体管的驱动电路的局部示意图;

图9是本申请一实施例提供的含有三种类型薄膜晶体管的驱动电路的局部示意图;

图10是本申请另一实施例提供的含有第一种类型薄膜晶体管驱动电路的局部示意图;

图11是本申请另一实施例提供的含有第二种类型薄膜晶体管驱动电路的局部示意图。

图12是本申请一实施例提供的一种显示面板的示意图。

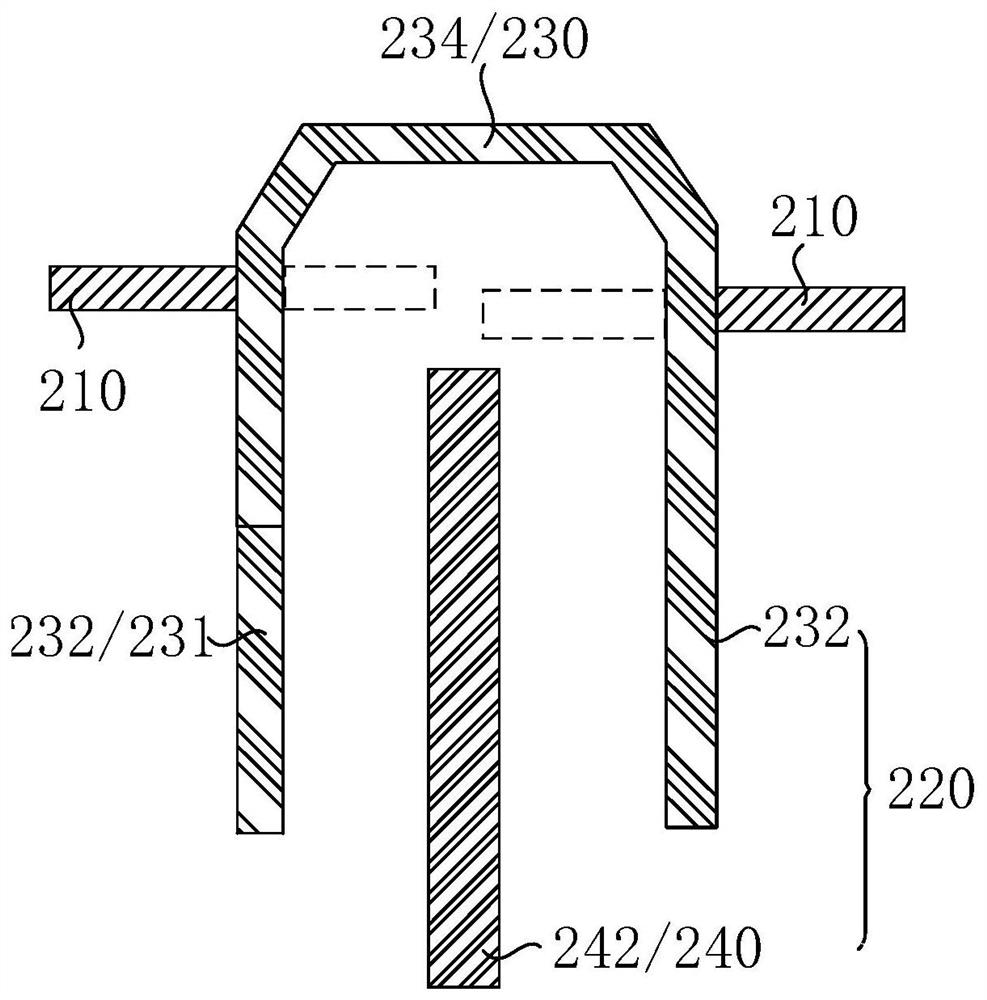

其中,100、阵列基板;200、驱动电路;201、第一薄膜晶体管;202、第二薄膜晶体管;203、第三薄膜晶体管;204、第四薄膜晶体管;210、源极引线;220、薄膜晶体管;230、源极;231、源极分支;232、第一源极分支;233、第二源极分支;234、源极主干;240、漏极;241、漏极分支;242、第一漏极分支;243、第二漏极分支;244、漏极主干;260、栅极;300、扫描线;400、显示面板;500、彩膜基板;600、液晶层。

具体实施方式

需要理解的是,这里所使用的术语、公开的具体结构和功能细节,仅仅是为了描述具体实施例,是代表性的,但是本申请可以通过许多替换形式来具体实现,不应被解释成仅受限于这里所阐述的实施例。

在本申请的描述中,术语“第一”、“第二”仅用于描述目的,而不能理解为指示相对重要性,或者隐含指明所指示的技术特征的数量。由此,除非另有说明,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征;“多个”的含义是两个或两个以上。术语“包括”及其任何变形,意为不排他的包含,可能存在或添加一个或更多其他特征、整数、步骤、操作、单元、组件和/或其组合。

另外,“中心”、“横向”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系的术语,是基于附图所示的方位或相对位置关系描述的,仅是为了便于描述本申请的简化描述,而不是指示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本申请的限制。

此外,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,或是两个元件内部的连通。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本申请中的具体含义。

下面参考附图和可选的实施例对本申请作详细说明,需要说明的是,在不相冲突的前提下,以下描述的各实施例之间或各技术特征之间可以任意组合形成新的实施例。

如图1和图2所示,是一种阵列基板的平面示意图,在阵列基板100的显示区设有扫描线300,在阵列基板100的非显示区设有驱动电路200,具体可为阵列基板行驱动电路,驱动电路200含有帧起始信号线(STV)、栅电压控制线(VGL)、时钟信号线(CKV)和多个GOA单元,GOA单元的输入端与STV、VGL和CKV连接,输出端与扫描线300连接,对扫描线300驱动;栅电压控制线通过源极引线210与GOA单元中的一个薄膜晶体管220连接,对薄膜晶体管220充电。

具体的,所述GOA单元包括第一薄膜晶体管201、第二薄膜晶体管202、第三薄膜晶体管203和第四薄膜晶体管204,所述第一薄膜晶体管201的源极230分别通过两条所述源极引线210与所述栅电压控制线、所述第二薄膜晶体管202的源极230连接,所述第一薄膜晶体管201的漏极240分别与所述第三薄膜晶体管203的源极230、第四薄膜晶体管204的栅极260连通,所述第一薄膜晶体管201的栅极260与所述第二薄膜晶体管202的栅极260连接;所述第二薄膜晶体管202的漏极240与所述第四薄膜晶体管204的源极230连接,所述第二薄膜晶体管202的栅极260与所述第四薄膜晶体管204的栅极260连接;所述第三薄膜晶体管203的漏极240与所述帧起始信号线连通,所述第四薄膜晶体管204的漏极240与所述时钟信号线连通。

在图2中示出的GOA单元中,含有四个相互连通的薄膜晶体管,以及其它的走线,图中可以看出有三个空白区域,即区域A、区域B和区域C;在区域B和区域C之间,两个薄膜晶体管220通过源极引线210连通,在将金属层蚀刻成源极230、漏极240和其它金属线图案前,需要在源极230、漏极240和其它金属线图案上形成蚀刻阻挡层,然后利用显影液形成阻挡层图案,由于区域B和区域C的面积较大,需要消耗较多的显影液,使得区域D和区域E吃到的显影能量变少,进而使区域D和区域E对应的阻挡层不易蚀刻完全,最后在蚀刻金属层图案时出现蚀刻不均匀的问题,导致区域D和区域E对应的源极230和漏极240发生短路。

如图3和图4所示,是两种示例性的GOA局部示意图,当区域D和区域E对应的金属图案未蚀刻均匀时,图3和图4中源极引线210会延伸到薄膜晶体管220的源极230沟道中,甚至是与漏极240连通,导致源极230和漏极240短路。

图5和图6分别是当理想状态下,基于图3和图4的示意图,但是这样需要消耗较多的显影液,以保证区域D和区域E对应的阻挡层蚀刻完全,从而使得后续在蚀刻金属图案时,源极引线210不会突出于源极230,不会延伸到源极230沟道中。

鉴于此,本申请提供一种在蚀刻不均匀时仍然不会导致源极230和漏极240短路的驱动电路200的控制开关,结合图1、图2、以及图7-图11所示,所述控制开关包括薄膜晶体管220,所述驱动电路200还包括与所述薄膜晶体管220连接的源极引线210,所述薄膜晶体管220含有源极230、漏极240和栅极260,源极230包括至少两个并列设置的源极分支231,以及连接各源极分支231的源极主干234,且与所述源极引线210直接连接的所述源极分支231为第一源极分支232,所述第一源极分支232与所述源极主干234的端部连接;漏极240与所述源极230同层设置,包括至少一个漏极分支241,以及连接各所述漏极分支241的漏极主干244,所述漏极分支241与所述源极分支231并列且交替设置以形成沟道,且与所述第一源极分支232相邻设置的所述漏极分支241为第一漏极分支242;所述栅极260与源极230、漏极240对应设置;其中,所述源极引线210的延长线位于所述第一漏极分支242和所述源极主干234之间。

需要说明的是,当漏极分支241只有一条时,漏极主干244是漏极分支241的一部分,与驱动电路200中的其它结构连接。而且,栅极260可以位于源极230和漏极240的下方,在薄膜晶体管220中形成底栅结构,栅极260也可以位于源极230和漏极240的上方,在薄膜晶体管220中形成顶栅结构。

目前,源极引线210通常与第一源极分支232垂直连接,由于对驱动电路200的集成度要求越来越高,源极230和漏极240之间的沟道间距变得越来越小,当由于各种原因导致对源极230、漏极240和源极分支231所在的金属膜层蚀刻不均时,例如图2中由于区域B和区域C的空白区域较大,需要消耗的蚀刻液更多,使得区域D和区域E中的蚀刻液不足,导致区域D和区域E中金属图案出现蚀刻不均匀的问题。此时未将源极引线210的端部蚀刻干净,导致源极引线210的端部从第一源极分支232中突出,由于源极230和漏极240之间的沟道间距较小,容易使得源极引线210与漏极240连接,使得源极230和漏极240短路。而且,目前设计中由于源极引线210的宽度尺寸通常较大,以增加对薄膜晶体管220的充电效果,这样使得源极引线210更加容易受到蚀刻不均匀的影响,并且从第一源极分支232中突出的面积较大,增大了源极230和漏极240短路的风险。

本申请通过对驱动电路200中薄膜晶体管220和源极引线210进行改进,使得源极引线210的延长线位于第一漏极分支242和所述源极主干234之间,且不与漏极分支241重叠;当对源极230、漏极240和源极引线210所在的膜层进行蚀刻时,即使存在蚀刻不均匀的问题,导致源极引线210的顶部突出于第一源极分支232,其突出位置也只会延伸到第一漏极分支242和所述源极主干234之间,不会与第一漏极分支242相交,因此不会导致源极230和漏极240短路。本方案对源极230和漏极240沟道宽度,以及对源极引线210的宽度不做限定,因此可以同时使得驱动电路200满足高集成度、高充电效果、不易短路等优点,提高了在同类型产品中的竞争力。

在图7-9中,一个薄膜晶体管220同时与两条源极引线210连接,此时,第一源极分支232有两条,第一漏极分支242至少有一条。在图10-11中,一个薄膜晶体管220只与一条源极引线210连接,此时,第一源极分支232只有一条,第二源极分支233至少有一条,第一漏极分支242只有一条。这两种连接情况可以适用于一个驱动电路200中,也可以适用于不同驱动电路200中,具体根据使用情况进行设计。

如图7所示,源极230只有两条与源极引线210一一对应连接的第一源极分支232,以及连接两条第一源极分支232的源极主干234;漏极240只有一条第一漏极分支242,第一漏极分支242位于两条第一源极分支232之间;两个第一源极分支232都在第一漏极分支242和源极主干234之间,同时不与第一漏极分支242有重叠部。薄膜晶体管220采用最简单的双沟道结构,源极230的形状类似于U型,第一漏极分支242与两个第一源极分支232之间形成两个沟道。由于两个源极引线210都与同一条第一漏极分支242进行对比,只要不与第一漏极分支242接触即可,因此在对蚀刻图案的设计上更为简单。

如图8所示,此时源极230包括两条第一源极分支232、一条第二源极分支233和一条源极主干234,两个第一源极分支232分别与源极主干234的两端连接,且分别与两条源极引线210一一对应连接,第二源极分支233并列地设置在两条所述第一源极分支232之间,与所述源极主干234的中部连接;所述漏极240包括两条第一漏极分支242和一条漏极主干244,两条第一漏极分支242分别与漏极主干244的两端连接;每一条漏极分支241都位于相邻两条第一源极分支232和第二源极分支233之间。本实施例中,源极230的形状类似于W型,漏极240的形状类似与U型,每一条源极引线210都可在第一源极分支232与相邻的第二源极分支233之间形成的区域内延伸,而不会与其它结构接触;因此,当蚀刻不均匀的问题较为严重时,也有足够的容错空间,防止源极引线210延伸过长导致源极230和漏极240短路。

如图9所示,此时源极230包括两条第一源极分支232、两条第二源极分支233和一条源极主干234,两条第一源极分支232分别与源极主干234的两端连接,且分别与两条源极引线210一一对应连接,两条第二源极分支233并列地设置在两条所述第一源极分支232之间,与源极主干234连接;漏极240包括两条第一漏极分支242、一条第二漏极分支243和一条漏极主干244,两条第一漏极分支242分别与漏极主干244的两端连接,第二漏极分支243并列地设置在两条第一漏极分支242之间,与漏极主干244的中部连接;每条所述第一漏极分支242都位于相邻两条第一源极分支232和第二源极分支233之间,所述第二漏极分支243位于相邻两条第二源极分支233之间。本实施例中,源极230的形状类似于三个并列的U型结构,漏极240的形状类似于W型,相对于图7和图8而言,图9中薄膜晶体管220的电学性能更好;当然,本申请还可以在图9的基础上继续增加第二源极分支233和第二漏极分支243的数量,使得薄膜晶体管220的电学性能进一步提高。

如图10所示,源极230只有一个与源极引线210连接的第一源极分支232,一个不与源极引线210连接的第二源极分支233,以及连接第一源极分支232和第二源极分支233的源极主干234;漏极240只有一个第一漏极分支242,第一漏极分支242并列设置在第一源极分支232和第二源极分支233之间,与第一源极分支232和第二源极分支233分别形成两个沟道;源极引线210的延长线位于所述第一漏极分支242和所述源极主干234之间,且不与所述第一漏极分支242重叠。本实施例中薄膜晶体管220同样为最简单的双沟道类型,但是与图7不同的是,由于图10中的薄膜晶体管只与一条源极引线210连接,因此源极引线具有较大的延伸空间,不容易与其它结构短接。

如图11所示,此时漏极240包括一条与源极引线210连接的第一源极分支232,两个不与源极引线210连接的第二源极分支233,以及连接第一源极分支232和第二源极分支233的源极主干234,其中一个第二源极分支233和第一源极分支232连接到源极主干234的两端,另一个第二源极分支233连接到源极主干234的中部;漏极240包括一条第一漏极分支242、一条第二漏极分支243和一条漏极主干244,第一漏极分支242和第二漏极分支243分别与漏极主干244的两端连接;第一漏极分支242并列地设置在相邻的第一源极分支232和第二源极分支233之间,第二漏极分支243并列地设置在相邻的两条第二源极分支233之间。为了进一步增加薄膜晶体管220的电学性能,还可以在图11的基础上进一步继续增加第二源极分支233和第二漏极分支243的数量。

本申请既可以通过减短第一漏极分支242的长度来增加第一漏极分支242与源极主干234的间距,从而使得源极引线210的延长线可以做到第一漏极分支242和所述源极主干234之间,且不与所述第一漏极分支242重叠;还可以通过减小源极引线210的宽度,使得源极引线210的延长线做到第一漏极分支242和所述源极主干234之间时,源极引线210的延长线且不与所述第一漏极分支242重叠;也可以通过减小源极主干234的宽度,使得源极引线210的延长线做到第一漏极分支242和所述源极主干234之间时,源极引线210的延长线且不与所述第一漏极分支242重叠;也可以通过上述两种或两种以上方式的结合方式来达到相同的技术效果。

在图7-11中,优选采用减短第一漏极分支242长度的方式,来增加第一漏极分支242与源极主干234的间距;此方式不会影响源极引线210的充电效果,也不会影响源极230和漏极240的电学均匀效果,而且相比于其他的方式而言,这一方式可以任意控制漏极240的长度,由于漏极240的长度较大,因此能够使得第一漏极分支242与源极主干234的间距较大。而在图9和图11中,第二漏极分支243的长度不需要改变,此时所述第二漏极分支243与所述源极主干234之间的距离,小于所述第一漏极分支242与所述源极主干234之间的距离;这样的设计使得虽然减小了第一漏极分支242的长度,但是源极230和漏极240之间的沟道间距并不会受到较大的影响,对薄膜晶体管220的影响较小。

具体的,可以使第一漏极分支242减短的距离与源极引线240的宽度相等,也就是说所述第二漏极分支243与所述第一漏极分支242的长度之差,和所述源极引线210的宽度相等;其中,所述第一漏极分支242、第二漏极分支243的长度方向为所述第一漏极分支242、第二漏极分支243的延伸方向。这样的紧密排布充分利用第一漏极分支242与源极主干234之间的空白区域,有利于缩小薄膜晶体管220的体积,且第二漏极分支243与源极引线210的顶部(靠近源极主干的一侧)平齐,方便在制作图案时进行对准设计,从而减小蚀刻阻挡层图案的蚀刻难度,提高对源极230、漏极240和源极引线210所在的金属层进行蚀刻时的均匀效果。

而且,当薄膜晶体管220与两条源极引线210连接时,两条源极引线210可以设置在同一直线上,可以使得两条第一漏极分支242的减短距离相同,这样既方便提高薄膜晶体管220两端源极230和漏极240的均匀效果,又能够同时将两个第一漏极分支242的长度做到最大程度,以免一个第一漏极分支242长,一个第一漏极分支242短,降低薄膜晶体管220的电学性能。当然,两条源极引线210也可以不设置在同一直线上,防止两条源极引线210短接,做成短路的风险。

在本申请中,所有源极分支231和漏极分支241均为条状结构,可为矩形、椭圆形或其它形状,源极分支231的延伸方向与源极主干234的延伸方向相互垂直,漏极分支241的延伸方向与漏极主干244的延伸方向互相垂直;当然,源极分支231的延伸方向与源极主干234的延伸方向之间的夹角可以形成锐角,同时漏极分支241的延伸方向与漏极主干244的延伸方向之间的夹角也为锐角。源极引线210与第一源极分支232之间可以垂直设置,也可以倾斜设置。

另外,源极分支231、源极主干234、漏极分支241和漏极主干244的宽度都相等,相邻第二源极分支233与漏极分支241之间的沟道宽度也相等,从而提高薄膜晶体管220的导电性能。由于本申请只需要减小第一漏极分支242的长度就能够克服由于蚀刻不均匀所导致的源极230和漏极240短路的问题,因此可以进一步减小源极分支231和漏极分支241之间的沟道宽度,减小第二漏极分支243与源极主干234之间的间距,减小源极主干234和漏极主干244的间距,来进一步提高驱动电路200中的集成度,减小显示面板中驱动电路200的占用面积,进一步减小显示面板的窄边框。

如图12所示,是一种显示面板的示意图,作为本申请的另一实施例,还公开了一种显示面板400,所述显示面板400包括图1所示的阵列基板100,与所述阵列基板100相对设置的彩膜基板500,以及设置在所述阵列基板100和彩膜基板500之间的液晶层600;所述阵列基板100的非显示区含有上述驱动电路200。另外,本申请中的薄膜晶体管220不仅适用于非显示区中的阵列基板行驱动电路,同样适用于所述阵列基板100显示区中的主动开关。

本申请的技术方案可以广泛用于各种显示面板,如TN(Twisted Nematic,扭曲向列型)显示面板、IPS(In-Plane Switching,平面转换型)显示面板、VA(VerticalAlignment,垂直配向型)显示面板、MVA(Multi-Domain Vertical Alignment,多象限垂直配向型)显示面板,当然,也可以是其他类型的显示面板,均可适用上述方案。

需要说明的是,本申请的发明构思可以形成非常多的实施例,但是申请文件的篇幅有限,无法一一列出,因而,在不相冲突的前提下,以上描述的各实施例之间或各技术特征之间可以任意组合形成新的实施例,各实施例或技术特征组合之后,将会增强原有的技术效果。

以上内容是结合具体的可选实施方式对本申请所作的进一步详细说明,不能认定本申请的具体实施只局限于这些说明。对于本申请所属技术领域的普通技术人员来说,在不脱离本申请构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本申请的保护范围。

- 一种驱动电路的控制开关、阵列基板和显示面板

- 一种驱动电路的控制开关、阵列基板和显示面板