切换装置及存储器装置

文献发布时间:2023-06-19 11:27:38

技术领域

本发明是有关于一种切换装置及存储器装置,使用于集成电路之中,包括集成电路存储器装置(integrated circuit memory device)。

背景技术

切换装置具有许多应用,例如集成电路之中的晶体管以及二极管。新的非易失性存储器(nonvolatile memory,NVM)技术的兴起,例如相变化存储器及电阻式存储器(resistive memory),已被令人兴奋的应用所激励(motivated),例如存储级存储器(storage class memory)、固态硬盘(solid-state disk)、嵌入式非易失性存储器(embedded nonvolatile memory)以及类神经计算(neuromorphic computing)。许多的这些应用在巨形「交叉点」阵列(vast crosspoint array)之中是显示密集叠层的(packeddensely),可提供许多的千兆位组(gigabyte)。

此阵列之中,准确读取或低功率(low-power)写入的任何小子集阵列的存取是需要强非线性(strong nonlinearity)的IV特性,以使通过选择的装置的电流大幅超过通过未选择的装置的残余漏电(residual leakage)。此非线性可通过在每一交叉点添加一分立式存取装置(discrete access device)被明确地包括,或使用亦显示高非线性IV特性(highly nonlinear IV characteristic)的非易失性存储器装置(NVM device)被隐含地包括。

其他类型的切换装置基于双向材料(ovonic material)是已知为双向定限开关(ovonic threshold switch),其特征是于切换阈值电压(switching threshold voltage)的电阻大幅下降,当电压下降至低于一保持临界值(holding threshold),阻挡状态(blocking state)下复原(recovery)为高电阻。

切换装置已被使用于例如是各种可编程电阻式存储器装置(programmableresistance memory device)之中,包括一交叉点架构(crosspoint architecture)中所组织的多个单元(cell)的高密度阵列。一些交叉点架构使用多个存储器单元(memory cell),例如包括一相变化存储器元件(phase change memory element)或串联一双向定线开关的其他电阻式存储器元件(resistive memory element)。其他架构(architecture)是被使用,包括各种2维及3维阵列结构,亦可使用切换装置以选择阵列之中的存储器元件。此外,双向定限开关已被提出,用于各种其他用途,包括所谓的类神经计算。

使用于集成电路的材料的热稳定性(thermal stability)可以是一重要特性。举例而言,集成电路的后段工艺(back end of line,BEOL)之中,高达400℃的温度可被产生,可超过结晶转换温度(crystallization transition temperature)或可劣化双向材料的稳定性。此外,设备的元件中,集成电路可在焊接接合(solder bonding)或其他高温元件工艺期间被曝露于高温。此外,集成电路可在所属领域之中的操作期间被曝露于高温。举例而言,GeTe

提供具有相对高阈值电压(threshold voltage)、低漏电流(leakage current)、快速切换速度(switching speed)、以及在制造期间与所属领域中的操作期间所受到(encounter)的温度的良好热稳定性的切换装置,是期望的。

发明内容

一种电压感测切换装置(voltage sensitive switching device),包括一第一电极;一第二电极;以及一切换层(switching layer),位于第一电极以及第二电极之间,切换层包括碳C、砷As、硒Se及锗Ge的一组成物(composition),此组成物在高于400℃的温度是稳定的。一类组成物是用作一集成电路中的一切换层,其中碳C、砷As、硒Se、锗Ge的量是被结合,碳C、砷As、硒Se、锗Ge的量以及切换层的厚度有效地使其具有超过400℃的结晶转换温度(为了一薄膜的热循环的说明的目的而测量)。一些实施例中,结晶转换温度是超过450℃。一些实施例中,结晶转换温度是超过500℃。

一类组成物,包括砷As、硒Se、锗Ge以及10at%至30at%的范围的组成物的碳C。本文所述的材料包括一子类别(sub-class),包括10at%至30at%的范围的碳C、20at%至35at%的范围的砷As、35at%至55at%的范围的硒Se以及8at%至25at%的范围的锗Ge。此类组成物的成员(member)之中,一切换层之中的C、As、Se及Ge的量是被结合,C、As、Se及Ge的量以及切换层的厚度有效地使其具有高热稳定性以及高结晶转换温度。

在存取选择的开关的操作期间,当控制电路是用于一阈值电压,通过施加一电压至一选择的开关以使选择的开关之中的切换层之上的电压高于阈值电压,且通过施加一电压至一未选择的开关以使未选择的开关之中的切换层之上的电压低于阈值电压,组成物用于转换一阈值电压是有效的。

一存储器装置(memory device),包括一第一电极;一第二电极;一存储器元件;以及一切换层,例如是上述的切换层,位于第一电极以及第二电极之间而串联于存储器元件。存储器装置可包括一势垒层(亦称作一缓冲层(buffer layer)),位于存储器元件以及切换层之间。存储器装置可用作一集成电路装置(integrated circuit device)之上的3D交叉点存储器(3D crosspoint memory),其具有非常高的密度。

此外,切换装置可使用于各种其他种类的装置。

通过阅读以下附图、详细说明以及权利要求书,可见本发明的其他方面以及优点。

附图说明

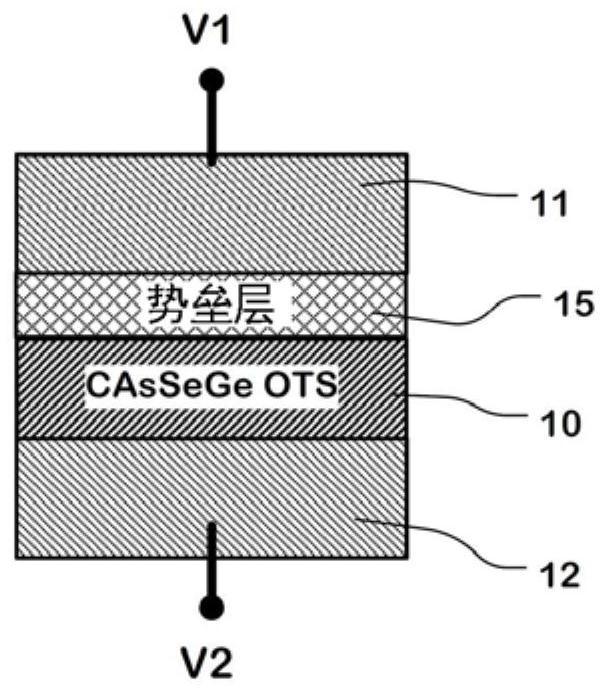

图1A是包括一组成物的一切换层的切换装置的剖面的示意图,此组成物包括CAsSeGe材料。

图1B是包括一组成物的切换装置的剖面的示意图,此切换装置是本文所述的「蕈状单元」构造。

图2是四元组成物图表,绘示本文所述的一类材料。

图3是材料A的电阻对温度的图表,绘示结晶转换温度。

图4是材料C的表面粗糙度对温度的图表,绘示热稳定性。

图5是包括本文所述的材料的OTS开关的循环的外加电压/感应电流的图表。

图6是本文所述的OTS开关的盒形图,绘示高于3V的瞬时阈值电压(transientthreshold voltage)。

图7是开启电流以及关闭电流的位准的图表,绘示超过10

图8是一交叉点存储器装置中的存储器单元的示意性3D透视图,交叉点存储器装置包括本文所述的切换装置。

图9是一交叉点存储器装置的交替叠层构造的示意性层图,交叉点存储器装置包括本文所述的切换装置。

图10是制造本文所述的切换装置的示意性流程图。

图11是包括一3D存储器的集成电路存储器装置的示意性方块图,3D存储器使用本文所述的切换装置。

【符号说明】

5:区域

10:切换层

11:第一电极

12:第二电极

15:势垒层

20:切换层

21:第一电极

22:第二电极

25:势垒层

101:底电极层

102:势垒层

103:OTS切换层

104:势垒层

105:存储器材料层

106:顶部势垒层

110:第一存取线

120:第二存取线

125:存储器单元

160:顶电极层

161:底电极层

162:势垒层

163:OTS切换层

164:势垒层

165:存储器材料层

166:势垒层

171、172:覆盖层

210、212、214、216、218:步骤

300:集成电路

302:阵列

304:列/层译码器

306:字线

308:行/层译码器

310:位线

312:总线

314:方块

316:总线

318:数据输入线

320:其他电路

322:数据输出线

324:控制器

326:偏压电路电压源以及电流源

501:第一循环

Tx:结晶转换温度

V1、V2:电压

具体实施方式

为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

本发明的实施例的详细叙述是参照图1A~图11被提供。

图1A是一切换装置的示意图,此切换装置包括本文所述的一碳砷硒锗(CAsSeGe)材料的一切换层10。切换装置包括一第一电极11与一第二电极12、以及串联在第一电极及第二电极之间的一势垒层15与一切换层10。电压V1可被施加至第一电极11,电压V2可被施加至第二电极12。

图1B是「蕈状单元(mushroom cell)」构造的一切换装置的示意图,此切换装置包括一第一电极21与第二电极22、以及串联在第一电极21与第二电极22之间的一势垒层25与一切换层20。此实施例中,第二电极22是通过一介电层耦接至一导体(conductor),此导体可用于连接至一驱动器或用于操作切换装置的其他电压源。在「蕈状单元」构造中,第二电极22以及切换层20具有一接触面积,此接触面积相当小于第一电极21以及切换层20的对应接触面积。此较小的接触面积用于(serve to)集中电流通过较小区域中的切换层,可致能(enable)切换元件的更低的电流操作。

对于图1A及图1B的切换装置,当穿过在第一电极11、21及第二电极12、22之间的切换层的电压(V1-V2)超过切换层的阈值电压,接着切换装置是被开启。当穿过第一电极11、21及第二电极12、22的电压是低于切换层的保持阈值电压(holding threshold voltage),切换装置返回到高阻抗关闭状态(impedance,off state)。图1A及图1B所绘示的切换装置可具有高非线性电流对电压特性(nonlinear current versus voltagecharacteristic),使这些切换装置适合用来作为在高密度存储器装置及其他设定中的切换元件。

势垒层15可提供一或多个的阻力(resistance)、附着力(adhesion)以及扩散势垒功能(diffusion barrier function)。势垒层15可具有导电材料层,此导电材料层具有约5至约50纳米(nm)的厚度,优选约20nm。势垒层15可以是一组成物,此组成物包括碳(包括实质上的纯碳(pure carbon)),或此组成物是双向定限开关材料的顶表面上的硅及碳、或包括其他材料。势垒层15的其他实施例材料可以是一金属氮化物,例如氮化钛(titaniumnitride,TiN)、氮化钽(tantalum nitride,TaN)、氮化钨(tungsten nitride,WN)、氮化钼(molybdenum nitride,MoN)、氮化铌(niobium nitride,NbN)、氮化硅钛(titaniumsilicon nitride,TiSiN)、氮化铝钛(titanium aluminum nitride,TiAlN)、氮化硼钛(titanium boron nitride,TiBN)、氮化硅锆(zirconium silicon nitride,ZrSiN)、氮化硅钨(tungsten silicon nitride,WSiN)、氮化硼钨(tungsten boron nitride,WBN)、氮化铝锆(zirconium aluminum nitride,ZrAlN)、氮化硅钼(molybdenum silicon nitride,MoSiN)、氮化铝钼(molybdenum aluminum nitride,MoAlN)、氮化硅钽(tantalum siliconnitride,TaSiN)或氮化铝钽(tantalum aluminum nitride,TaAlN)。除了金属氮化物,势垒层15可包括材料,例如碳、掺杂多晶硅(doped polysilicon)、钨(W)、铜(Cu)、钛(Ti)、钼(Mo)、钽(Ta)、硅化钛(titanium silicide,TiSi)、硅化钽(tantalum silicide,TaSi)、钨化钛(titanium tungsten,TiW)、氮氧化钛(titanium oxynitride,TiON)、氮氧化铝钛(titanium aluminum oxynitride,TiAlON)、氮氧化钨(tungsten oxynitride,WON)或氮氧化钽(tantalum oxynitride,TaON)。

一些实施例中,一第二势垒层可设置在双向定限开关材料的第二表面(例如底表面)上,此第二表面相对于所述提及的第一表面。

切换层10、20是一双向定限开关,此双向定限开关具有碳C、砷As、硒Se、锗Ge的一组成物,热稳定至超过400℃的温度。一类组成物是用作一集成电路中的一切换层10,其中碳C、砷As、硒Se、锗Ge的量是被结合,碳C、砷As、硒Se、锗Ge的量以及切换层10的厚度有效地使其具有超过400℃的结晶转换温度。一些实施例中,结晶转换温度可以是超过450℃。一些实施例中,结晶转换温度可以是超过500℃。

图2是材料C、As、Se及Ge的金字塔形四元组成物(quaternary composition)图表。图表之中,砷、硒及锗的浓度可通过位于金字塔底部的三轴上的位置来代表,砷位于图表中的后方。碳的浓度是通过金字塔的垂直位置来代表。

此图表大致上绘示代表一类别的碳砷硒锗材料的区域5,区域5在高温下是稳定的并具有阈值电压、低关闭状态电流(off-state current)以及在厚度低于100nm的切换耐久度(switching endurance)。一些实施方式中,区域5更佳地具有厚度低于50nm的切换耐久度。其中,厚度在用于本文所述的集成电路存储器单元(integrated circuit memorycell)之中可以是关键的。

图2中,材料A、B、C以及砷硒锗(AsSeGe)的材料是被绘示,其具有如以下表格所示的组成物。

具有30nm的厚度的区域5之中的材料A及C是被测试,作为一切换层是显示令人意外(surprising)且意料不到地(unexpectedly)的良好性能以及超过400℃的温度的良好的热稳定性。材料A及C的测试显示渐增的(increasing)结晶转换温度以及渐增的碳浓度的趋势,建立区域5之中的材料的范围可具有高热稳定性以及高结晶转换温度的期望。

为进行对照(for comparison),具有30nm厚度的上方表格之中的砷硒锗(AsSeGe)材料具有约4伏特(V)的阈值电压Vth以及在2V的约7pA的关闭电流(Ioff)。具有30nm厚度的材料A具有约2.95V的阈值电压Vth以及在2V的约2nA的关闭电流。具有30nm厚度的材料C具有约2.6V的阈值电压Vth以及在2V的约0.6nA的关闭电流。因此,在低于100nm的厚度,对于一些实施方式而言更佳地在低于50nm的厚度,材料A及C具有适合用作存储器装置之中的双向定限开关(OTS)装置及OTS切换元件的特性,显示渐增的阈值电压以及渐增的碳浓度。具有在材料A的特性及材料C的特性之间的特性的材料B因此亦应适合用作存储器装置之中的OTS装置及OTS切换元件。实施例可用作具有小于50nm厚度的一切换层,组成物包括As、Se、Ge及C,As、Se、Ge及C的量是使用施加的电压脉冲(applied voltage pulse)在阈值电压Vt<4V且在小于5ns的持续期间进行有效切换。

一类组成物是包括砷As、硒Se、锗Ge及碳C,碳C位于基于此组成物的10at%至30at%的实验结果的外插法(extrapolation)的范围之中,在超过400℃的令人惊讶且不可预期的高温是稳定的。一些实施例中,多个材料是被结合,这些材料的浓度可以有效地具有超过450℃的结晶转换温度。一些实施例中,多个材料是被结合,这些材料的浓度可以有效地具有超过500℃的结晶转换温度。

具有在20及21at%之间的砷浓度的材料A、B及C一般地位于区域5之中,在超过400℃的令人惊讶且不可预期的高温是稳定的。一些实施例中,结晶转换温度可以超过450℃。一些实施例中,结晶转换温度可以超过500℃

位于区域5之中的材料一般包括基于实验结果的外插法的碳砷硒锗的一类组成物,此类组成物包括位于10at%至30at%的范围的碳、位于20at%至35at%的范围的砷、位于35at%至55at%的范围的硒、以及位于8at%至25at%的范围的锗。此类组成物的成员之中,使用小于50nm的层厚度的C、As、Se及Ge可被结合为一切换层,C、As、Se及Ge的量有效地使此切换层在超过400℃的令人惊讶且不可预期的高温是稳定的。一些实施例中,C、As、Se及Ge的量有效地使此切换层具有超过450℃的结晶转换温度。一些实施例中,C、As、Se及Ge的量有效地使此切换层具有超过500℃的结晶转换温度。此类组成物的一特定成员的多个元素的相对浓度可被选择,以有效达成通过本文所述的测试所显示的一或多个特性,此一或多个特性包括高热稳定性、高结晶转换温度、高阈值电压、低关闭状态电流、快速切换(fast switching)及高耐久度(endurance)。

为了测试材料A的热稳定性,材料A的薄膜是被沉积在一基板上且受到渐增的温度。目视检查(visual inspection)显示,此薄膜在超过450℃的温度似乎未受到破坏,此薄膜受到暗示热降解(thermal degradation)的变色(discoloration)或粗糙度(roughness)是发生在大约550℃。即使从x光绕射量测(x-ray diffraction measurement)所推断(deduce)的结晶转换(crystallization transition)直到约500℃似乎并未发生,上方表格之中的三元素AsSeGe组成物的比较测试(comparable testing)显示低于380℃的变色或粗糙度破坏。由于材料之中的局部相分离(localized phase separation)、剥离(delamination)或其他物理变化所造成的表面粗糙度,变色是被相信会发生,显示由于缺乏热稳定性的热降解。

图3是材料A的电阻对温度(resistance versus temperature)的图表,在沿着顶列样品的低温显示非常高的电阻,大约530℃转换至低电阻且当材料被冷却时保持在低电阻。此图表显示超过500℃的材料A的结晶转换温度Tx。

虽然并未绘示于图3之中,材料C亦使用一基板上的一薄膜来进行测试。当温度斜向上升(ramp up)超过530°,并未观察到结晶。此外,目视检查中没有看见变色或热破坏。

图4是材料C的温度对表面粗糙度(temperature versus surface roughness)的图表,关于如上所述的后段工艺,绘示材料的热稳定性使材料C曝露于400℃以上、450℃以上、以及500℃以上或更高的温度而不会改变表面粗糙度,以提供热稳定性的实质制造容限(substantial manufacturing margin)。

装置性能亦进行一单元(cell)的测试,例如绘示于图1B的使用材料C的30nm厚的层、一钨底电极(tungsten bottom electrode)、在OTS材料上的一碳势垒层(carbonbarrier layer)以及一钨顶电极(tungsten top electrode)。

开关(switch)的循环的外加电压(force voltage)/感应电流(sense current)的IV图表是绘示于图5之中。通过扫描(sweep)电压从0V至4V,然后从4V至0V,并测量电流I,此图表是被产生。图表之中,符合(for compliance)100μA的最大值是被设定,因此甚至当此区域的电压增加,电流是恒定的(constant)。第一循环501是一形成循环(forming cycle),其中阈值电压是相对高的。后续循环之中,开关一致在约2.6V的临界值(threshold)以及在约1.4V的保持电压(holding voltage)Vh进行切换。图5之中,第一循环500为OTS材料在形成时的IV特性。很常见的是,形成工艺(forming process)的电流-电压曲线(I-V curve)是相异于形成工艺之后(第二循环~第五循环501)的电流-电压曲线。

图6是5纳秒(nsec)切换脉冲(switching pulse)的盒形图,显示材料C在5纳秒内约3.2伏特的成功切换。

图7是绘示耐久度的图表,绘示材料C的开启电流(on-current)及关闭电流(off-current)的位准(level),在测试样品中高达10

来自材料C的测试的数据暗示,如以上讨论的材料A、材料B、CAsSeGe的其他组合、以及区域5之中的其他材料可具有浓度的组合,此浓度的组合有效地具有如本文所讨论的快速切换、良好耐久度以及高结晶温度的类似行为(similar behavior)。

图8绘示一实施例存储器单元125,包括设置在一第一存取线(access line)110及一第二存取线120的交叉点上的一多层柱体(pillar)。

此实施例的柱体包括在第一存取线110上的一底电极层101,例如一金属、金属氮化物、一掺杂半导体(doped semiconductor)或类似物。

一势垒层102设置在底电极层101上。一些实施例中,势垒层102包括一组成物,例如本文所述的碳、或硅及碳。势垒层102可以例如是15至30nm厚。

一OTS切换层103设置在势垒层102之上。OTS切换层103可包括一OTS材料,例如本文所述的高达超过400℃的温度的热稳定性,包括参照图2以上所述的此类材料的材料。OTS切换层可以例如是15至45nm厚的CAsSeGe材料层,更佳地小于50nm厚度。

一势垒层104设置在OTS切换层103之上,且可被称作为OTS材料的覆盖层(cappinglayer)。势垒层104是包括如本文所讨论的碳、或硅及碳的组成物的势垒层。势垒层104可以例如是15至30nm厚。

一存储器材料层(memory material layer)105设置在势垒层104之上。存储器材料可包括一可程序电阻材料(programmable resistance material)。方法(technology)的实施例中,存储器材料包括一相变化存储器材料(phase change memory material),例如GST(例如Ge

存储器材料层105可包括一硫是合金(chalcogenide alloy)层,使用添加物以修饰(modify)导电度(conductivity)、转换温度(transition temperature)、熔化温度以及其他性质。代表性的添加物可包括氮(N)、硅(Si)、氧(O)、氧化硅(SiO

一些实施例中,其他可编程电阻存储器元件(programmable resistance memoryelement)可被实施,例如金属氧化物电阻式存储器(metal-oxide resistive memory)、磁阻式存储器(magnetic resistive memory)、导电桥电阻式存储器(conducting-bridgeresistive memory)或其他类型的存储器装置。

第一存取线(位线)以及第二存取线(字线)可包括各种金属、类金属材料(metal-like material)、掺杂半导体或其组合。第一存取线及第二存取线的实施例可使用一或多个材料层(layer of material)被实施,例如钨(W)、铝(Al)、铜(Cu)、氮化钛(TiN)、氮化钽(TaN)、氮化钨(WN)、掺杂多晶硅、硅化钴(CoSi)、硅化钨(WSi)、氮化钛/钨/氮化钛(TiN/W/TiN)及其他材料。举例而言,第一存取线及第二存取线的厚度的范围可以是10至100nm。其他实施例中,第一存取线及第二存取线可以非常薄或非常厚。第二存取线所选择的材料是优选地选择与存储器材料层105以及顶部势垒层(top barrier layer)106兼容(compatibility)。同样地,第一存取线所选择的材料是优选地选择与底电极层101以及势垒层102兼容。

另一实施例中,如图3所示的底电极相较于存储器元件的表面具有较小的接触表面(contact surface),此底电极夹置在存储器材料层105及OTS切换层103之间、或存储器材料层105及顶部势垒层106之间。因此,在存储器元件中的接触点(contact)的增加的电流密度可被达成。

一顶部势垒层106设置在存储器材料层105之上。一些实施例中,顶部势垒层106包括一组成物,包括本文所述的硅及碳。顶部势垒层106可以例如是15至30nm厚。

除了本文所述的硅及碳的组合,第一势垒层102、第二势垒层104及顶部势垒层106的实施例材料可以是金属氮化物,例如氮化钛(titanium nitride,TiN)、氮化钽(tantalumnitride,TaN)、氮化钨(tungsten nitride,WN)、氮化钼(molybdenum nitride,MoN)、氮化铌(niobium nitride,NbN)、氮化硅钛(titanium silicon nitride,TiSiN)、氮化铝钛(titanium aluminum nitride,TiAlN)、氮化硼钛(titanium boron nitride,TiBN)、氮化硅锆(zirconium silicon nitride,ZrSiN)、氮化硅钨(tungsten silicon nitride,WSiN)、氮化硼钨(tungsten boron nitride,WBN)、氮化铝锆(zirconium aluminumnitride,ZrAlN)、氮化硅钼(molybdenum silicon nitride,MoSiN)、氮化铝钼(molybdenumaluminum nitride,MoAlN)、氮化硅钽(tantalum silicon nitride,TaSiN)及氮化铝钽(tantalum aluminum nitride,TaAlN)。除了金属氮化物,第一势垒层102及顶部势垒层106可包括多个材料,例如碳、掺杂多晶硅、钨(W)、铜(Cu)、钛(Ti)、钼(Mo)、钽(Ta)、硅化钛(titanium silicide,TiSi)、硅化钽(tantalum silicide,TaSi)、钨化钛(titaniumtungsten,TiW)、氮氧化钛(titanium oxynitride,TiON)、氮氧化铝钛(titanium aluminumoxynitride,TiAlON)、氮氧化钨(tungsten oxynitride,WON)或氮氧化钽(tantalumoxynitride,TaON)。

第一存取线(位线)及第二存取线(字线)可包括各种金属、类金属、掺杂半导体或其组合。第一存取线及第二存取线的实施例可使用一或多个材料层(layer of material)被实施,例如钨(W)、铝(Al)、铜(Cu)、氮化钛(TiN)、氮化钽(TaN)、氮化钨(WN)、掺杂多晶硅、硅化钴(CoSi)、硅化钨(WSi)、氮化钛/钨/氮化钛(TiN/W/TiN)及其他材料。举例而言,第一存取线及第二存取线的厚度的范围可以是10至100nm。其他实施例中,第一存取线及第二存取线可以非常薄或非常厚。

第一电极及介电层是被形成,可使用例如美国专利号No.8,138,028,标题「Methodfor Manufacturing a Phase Change Memory Device with Pillar Bottom Electrode」所公开的方法、材料以及过程,其通过引用并入于本文中。

或者地,切换装置可在一交叉点架构中被组织(organized),叙述于例如2003年6月17日公告的美国专利号No.6,579,760的「Self-Aligned,Programmable Phase changememory」,其通过引用并入于本文中。第一电极可以是存取线,例如字线和/或位线。此架构之中,存取装置(access device)被排列在切换装置以及存取线之间。

图9绘示包括本文所述的CAsSeGe OTS层的材料及一存储器层(memory layer)的交替叠层(alternative stack)。图9的材料叠层(stack of material)可被使用于如图8所示的交叉点结构之中。图8及图9所示的实施例的各种材料叠层可被使用。

图9之中,叠层包括位于第一存取线(未绘示)之上的一底电极层161,例如一金属、金属氮化物、一掺杂半导体或类似物。

一势垒层162设置在底电极层161之上。一些实施例中,势垒层162包括例如本文所述的硅及碳的一组成物。势垒层162可以例如是15至30nm厚。

一OTS切换层163设置在势垒层162之上。OTS切换层163可包括一OTS材料,例如本文所述的具有高达超过400℃的温度的热稳定性的OTS材料,包括参照图2的上述类别材料的材料。OTS切换层可以例如是15至45nm厚的CAsSeGe材料层,更佳地小于50nm厚。

一势垒层164设置在OTS切换层163之上且可被称作OTS材料的覆盖层。势垒层164可包括本文所讨论的硅及碳的组成物。势垒层164可以例如是15至30nm厚。

一存储器材料层165设置在势垒层164上方。存储器材料可包括参照图8所讨论的可程序电阻材料。覆盖层172,包括例如是钨或另一导体,可设置在存储器材料层165以及势垒层164之间。此外,一覆盖层171,包括例如是钨或其他导体,可位于存储器材料层165上方。

图9的叠层中,一势垒层166,包括例如是碳及硅,覆盖(overlie)覆盖层171。一顶电极层160设置在势垒层166上方。另一实施例中,如图3所示的具有相较于存储器元件的表面更小的接触表面的底电极,是夹置在存储器材料层165以及OTS切换层163之间、或在存储器材料层165以及势垒层166之间。因此,在存储器元件中的接触点(contact)的增加的电流密度可被达成。

图10是包括本文所述的CAsSeGe OTS材料的一存储器装置的工艺的示意性流程图。

于步骤210,使用例如是上述并入于本文中的参考文献所讨论的图案化方法(patterning technique)来形成一第一电极,此第一电极包括上述的材料,此第一电极具有一可选择的势垒层。

于步骤212,包括上述材料的包括一CAsSeGe OTS材料的切换层,例如是形成在一溅射系统(sputtering system)的一溅射腔室(sputtering chamber)之中,其具有由选择的材料所组成的目标(target)。一些实施例中,CAsSeGe材料是使用由选择的材料所组成的目标来进行沉积,同时形成多个元素的组合,此多个元素的组合的量有效地使此切换层在本文所讨论的高温是稳定的。

于步骤214,包括例如是上述的硅及碳的组成物的势垒层的沉积是被形成,以使此势垒层充当(act as)对抗(against)切换层的氧化的势垒层。一优选实施例中,此组成物通过在相同于OTS材料的溅射腔室之中进行原位溅射(in situ sputtering)被形成,或不使OTS材料曝露于氧化环境(oxidizing atmosphere)来形成此组成物。

于步骤216,一存储器材料是形成在势垒层之上。存储器材料可以是一可程序电阻材料,例如上述的相变化材料或其他材料。

于步骤218,一第二电极是被形成。第二电极可通过沉积以及图案化刻蚀(patterned etch)来形成,例如是一导电材料的图案化刻蚀。

一装置可使用后段工艺(back-end-of-line(BEOL)processing)被完成。后段工艺是用以完成芯片的半导体工艺步骤(semiconductor process step),包括一些制造方法(manufacturing technology),使材料曝露至400℃或更高的等级的温度(temperature onthe order of 400℃ or more)。后段工艺可以是本领域所已知的标准工艺(standardprocess),工艺的执行取决于芯片的构造(configuration),其中切换装置是被实施。一般地,通过后段工艺所形成的结构可包括接触点(contact)、层间介电质(inter-layerdielectric)以及芯片上的互连结构(interconnection)的各种金属层,包括耦接切换装置至周围电路(peripheral circuitry)的电路。由于这些工艺,图11所示的控制电路以及偏压电路是形成在装置之上。

图11是包括交叉点存储器单元(crosspoint memory cell)的3D阵列302的集成电路300的示意性方块图,集成电路300具有本文所述的CAsSeGe切换层(SSL开关)以及可编程电阻存储器层(programmable resistance memory layer)。具有读取模式、设定模式以及重设模式的列/层译码器(row/level decoder)304是耦接且电性连接于多个字线306,多个字线306在阵列302之中的多个层而沿着多个列被排列。一行/层译码器(column/leveldecoder)308是电性连接于多个位线310,多个位线310在阵列302之中的多个层而沿着多个行被排列,以在阵列302中的存储器单元进行读取、设定以及重设。地址(address)在总线(bus)312之上,被供应至列/层译码器304以及行/层译码器308。包括读取模式、设定模式以及重设模式的电压和/或电流源的方块314之中的感测电路(sense circuitry)(感测放大器)以及数据输入结构(data-in structure),是通过总线316耦接至行/层译码器(位线译码器(bit line decoder))308。数据是从集成电路300之上的输入/输出端口(input/output port)或从集成电路300的内部或外部的其他数据源(data source),通过一数据输入线(data-in line)318被供应至方块314之中的数据输入结构。其他电路320可被包括在集成电路300之上,例如一般目的处理器(general purpose processor)、特殊应用电路(special purpose application circuitry)或提供被阵列302所支持的系统单芯片功能(system-on-a-chip functionality)的多个模块的组合。数据是通过一数据输出线(data-out line)322,从方块314之中的感测放大器被供应至集成电路300之上的输入/输出端口或集成电路300的内部或外部的其他数据目标端(data destination)。

此实施例所实施的使用一偏压配置状态机(bias arrangement state machine)的控制器324,控制用于偏压配置(bias arrangement)的应用的偏压电路(biascircuitry)电压源以及电流源326的应用,包括读取、设定、重设以及验证(verify)字线以及位线的电压和/或电流。在读取操作或存取选择的存储器单元的其他操作的期间,通过施加一电压至选择的存储器单元以使选择的存储器单元中的开关上的电压高于临界值,且通过施加一电压至未选择的存储器单元以使未选择的存储器单元中的开关上的电压低于临界值,控制器根据切换层的结构以及组成物而包括用于本文所述的切换层的控制电路。此外,在选择的存储器单元的读取期间的施加至未选择的单元的电压是被设定,以使在存取选择的存储器单元的读取操作期间,关闭状态电流根据切换层的结构以及组成物是优选地小于2nA或小于1nA。

控制器324可使用本领域已知的特殊目的逻辑电路(special-purpose logiccircuitry)被实施。另一些实施例中,控制器324包括一般目的处理器,可在相同的集成电路上被实施以执行一计算机程序,以控制装置的操作。其他实施例中,特殊目的逻辑电路以及一般目的处理器的组合可使用于控制器324的实施。

以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 切换装置及存储器装置

- 通道切换装置、存储器存储装置及通道切换方法