可变电阻式存储器装置及其制造方法

文献发布时间:2023-06-19 11:44:10

技术领域

本发明涉及一种使用可变电阻式的存储器单元的可变电阻式存储器装置及其制造方法,尤其涉及一种包含可变电阻式的存储器单元的阵列的三维结构。

背景技术

可变电阻式随机存取存储器(以下,略记为可变电阻式存储器)可按照列地址及行地址而随机地选择存储器单元,从经选择的存储器单元中读出数据、或将数据写入经选择的存储器单元。为了谋求高积集化而利用三维结构制造可变电阻式存储器的技术例如由专利文献(美国专利申请公开第2017/0330916号公报)公开。如图1所示,专利文献的可变电阻式存储器包含作为位线的在垂直方向延伸的导电性柱10,在水平方向延长的字线30A、字线30B,以及形成在柱10与字线30A、字线30B的交叉部的互补型的电阻存储器元件20A、电阻存储器元件20B来构成。互补型的电阻存储器元件20A、电阻存储器元件20B分别包含第一半导体氧化膜21、作为中间电极的导电膜22、第二半导体氧化膜23。将互补型的电阻存储器元件20A、电阻存储器元件20B物理式地分离,由此抑制在存储器元件间产生不期望的潜行电流(sneak current)。但为了保持作为可变电阻元件的可靠性,必须以固定的膜厚均质地且再现性良好地形成这些半导体氧化膜。但是,为了所述目的的制造步骤并不容易,作为结果,存在导致制造成本的增加或良率的下降的担忧。

发明内容

本发明是解决此种现有的问题者,其目的在于提供一种具有经改善的三维结构的可变电阻式存储器装置。

本发明的可变电阻式存储器装置包括:多个垂直构件,在基板的主面的垂直方向延伸,包含第一导电型的半导体材料;多个水平构件,在所述基板的主面的水平方向延伸,包含半导电材料;以及存储器单元,形成在所述多个垂直构件与所述多个水平构件的各个交叉部;所述存储器单元包含形成在所述垂直构件的外周的栅极绝缘膜、形成在所述栅极绝缘膜的外周的包含第二导电型的半导体材料的半导体膜、及形成在所述半导体膜的外周的一部分的可变电阻膜,所述可变电阻膜的外周的电极区域与邻接的一对水平构件的一个连接,所述半导体膜与邻接的一对水平构件的另一个连接。

根据本发明,在多个垂直构件与多个水平构件的各交叉部形成存储器单元,并以可变电阻膜的外周的电极区域与一个水平构件电连接,半导体膜与另一个水平构件电连接的方式构成存储器单元,由此可提供使存储器单元阵列的三维结构与现有相比变得简易、且使制造步骤变得容易的可变电阻式存储器装置。

附图说明

图1是表示现有的三维结构的可变电阻式存储器的概略构成的图;

图2是表示本发明的实施例的可变电阻式存储器的整体构成的图。

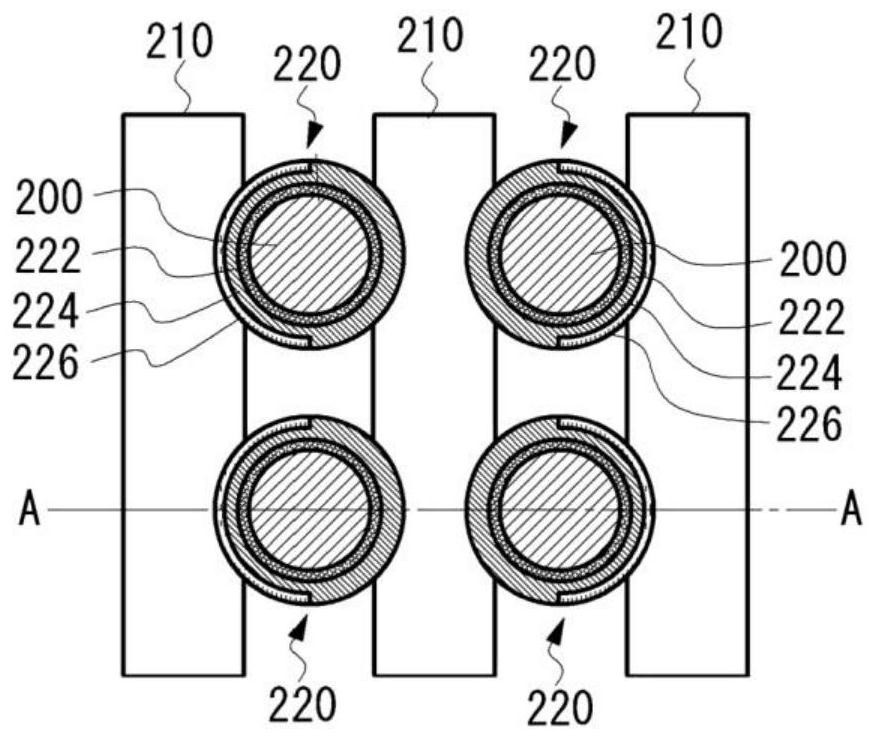

图3(A)以及图3(B)是表示本发明的实施例的可变电阻式存储器的存储器单元阵列的一部分的概略构成的图,图3(A)表示立体图,图3(B)表示平面图;

图4是图3(B)的A-A线的概略剖面图;

图5(A)~图5(J)是说明本实施例的存储器单元阵列的制造步骤的图;

图6(A)以及图6(B)是表示在本实施例中选择了存储器单元时的存取用晶体管与可变电阻元件的连接关系的图;

图7(A)以及图7(B)是表示根据本发明第二实施例的存储器单元阵列的构成的图;

图8是示意性地表示根据本发明第二实施例的存储器单元阵列的三维结构的图;

图9是表示根据本发明第二实施例的柱与字线的连接例的图;

图10是表示将本发明的实施例的存储器单元阵列的三维结构层叠在基板上的例子的概略剖面图。

[符号的说明]

10:导电性柱

20A、20B:电阻存储器元件

21:第一半导体氧化膜

22:导电膜

23:第二半导体氧化膜

30A、30B、WL、WL0、WL1、WL2、WL3、WL4、WL5:字线

100:可变电阻式存储器

110:存储器单元阵列

120:列选择/驱动电路

130:行选择/驱动电路

140:传感电路

150:写入/读出偏压电路

160:控制电路

170:内部数据总线

200:柱

210、210A、210B、BL、BL0、BL1、BL2、BL3、BL4、BL0_0、BL0_1、BL1_0、BL1_1、BL2_0、BL2_1:位线

220:存储器单元

222:栅极绝缘膜

224:半导体膜

226:可变电阻元件

230、232、234:层间绝缘膜

240:开口

250:材料层

260、280:多晶硅材料

270:绝缘材料

300:硅基板

310:存储器单元阵列

320:周边电路

330:绝缘层

340:导电层

GND:接地

K0、K1:电流路径

MC0:存储器单元(选择存储器单元)

MC1:存储器单元(非选择存储器单元)

MC2、MC3、MC1_0、MC1_1、MC2_0、MC2_1:存储器单元

R0:电阻成分

Vr:重置写入电压

Vread、Vbl:读出电压

Vs:设置写入电压

Vset、Vrset:写入电压

具体实施方式

本发明提供一种包含经堆叠的存储器单元阵列,即具有三维结构的存储器单元阵列的可变电阻式存储器。本发明的可变电阻式存储器除随机存取存储器单元的功能以外,还具备同时存取多个存储器单元的功能。以三维结构形成的存储器单元在一对位线间包含一个存取用晶体管、及形成在存取用晶体管的一侧的可变电阻元件。列方向的存储器单元在邻接的存储器单元间共有位线,以当选择一个存储器单元时,另一个存储器单元变成非选择的方式进行存储器单元的选择,防止在与选择存储器单元连接的选择位线形成不期望的潜通路(sneak path)。

另外,本发明的三维结构的存储器单元阵列可应用于交叉阵列或交叉存储器。交叉阵列用作用于构成作为人工智能(Artificial Intelligence,AI)硬件的神经网络的器件。

图2是表示本实施例的可变电阻式存储器的整体构成的图。本实施例的可变电阻式存储器100包含具有三维结构的存储器单元阵列110、列选择/驱动电路120、行选择/驱动电路130、传感电路140、写入/读出偏压电路150、控制电路160、将各部连接的内部数据总线170来构成。

图3(A)是示意性地表示本实施例的存储器单元阵列110的一部分的立体图,图3(B)是其概略平面图。图式例示有四个存储器单元。存储器单元阵列110包含相对于在未图示的基板(例如,硅基板)的主面的垂直方向延伸的多个柱200(在图式中,四根柱)、水平方向延伸且与多个柱200交叉的多个位线210(在图式中,六根位线)、以及形成在多个柱200与多个位线210的交叉部的可变电阻式的存储器单元220来构成。

柱200例如包含N型的多晶硅材料,柱200与对应的字线电连接。如图3(B)所示,在柱200的外周的整体,以固定的膜厚形成栅极绝缘膜222(例如,氧化硅膜等),在栅极绝缘膜222的外周的整体形成包含P型的多晶硅材料的半导体膜224。半导体膜224作为存取用晶体管的通道区域,当从柱200施加了电场时形成反转层。在半导体膜224的外周的一部分形成可变电阻元件226。可变电阻元件226以覆盖半导体膜224的一部分的方式形成为扇状,在图的例子中,以覆盖半导体膜224的约半周的方式形成可变电阻元件226。可变电阻元件226包含内侧的电极层、外侧的电极层、以及形成在这些电极层之间的转换层。转换层的材料为金属氧化物,例如HFO

位线210例如包含N型的多晶硅材料,在与柱200的交叉部,一个位线210与可变电阻元件226的外侧的电极层电连接,另一个位线210与未由可变电阻元件226覆盖的半导体膜224连接。图4表示图3(B)的存储器单元阵列的A-A线剖面图。

参照图5(A)~图5(J)对图3(A)以及图3(B)中所示的存储器单元的制造方法的一例进行说明。首先,如图5(A)所示,在基板(省略图示)上依次形成层间绝缘膜230、下层侧的位线210A、层间绝缘膜232、上层侧的位线210B、层间绝缘膜234。位线210A、位线210B为N+的多晶硅层,层间绝缘膜230、层间绝缘膜232、层间绝缘膜234例如为氧化硅膜或氮化硅膜等。

接着,利用微影步骤在层间绝缘膜234上形成掩膜层(省略图示)。掩膜层的形状及尺寸规定柱200的外形,例如若柱200为圆柱状,则掩膜层的预定形成柱200的部位形成有圆形的开口图案。使用掩膜层,通过各向异性蚀刻来对经层叠的层间绝缘膜230、层间绝缘膜232、层间绝缘膜234及位线210A、位线210B进行蚀刻,而形成如图5(B)所示的圆筒状的开口240。

接着,将掩膜层去除,如图5(C)所示,全面地形成可变电阻元件的材料层250。所述材料层250包含外侧的电极层、转换层(例如氧化铪(HfOx))及内侧的电极层的层叠。接着,形成掩膜层(省略图示),使用所述掩膜层对材料层250进行各向异性蚀刻和/或各向同性蚀刻,如图5(D)所示,在开口240的侧壁的一部分(例如,开口240的半周)形成可变电阻元件226。

接着,将掩膜层去除,如图5(E)所示,全面地形成P+的多晶硅材料260,接着,形成掩膜层(省略图示),使用所述掩膜层对多晶硅材料260进行各向异性蚀刻和/或各向同性蚀刻,如图5(F)所示,在开口240的侧壁、且可变电阻元件226的内侧形成半导体膜224。由此,可变电阻元件226由半导体膜224覆盖。

接着,将掩膜层去除,如图5(G)所示,全面地形成SiO

接着,将掩膜层去除,如图5(I)所示,全面地形成N+的多晶硅材料280,对多晶硅材料280进行回蚀或平坦化,形成如图5(J)所示的柱200。另外,所述制造步骤是先形成位线210A、位线210B,其后形成柱200,但并不限定于此,也可以在形成柱200与其周围的栅极绝缘膜222、半导体膜224及可变电阻元件226后,形成位线210。另外,本实施例的存储器单元阵列并不限定于所述制造方法,也可以是使用其它制造步骤来制造者。

再次参照图2。列选择/驱动电路120根据来自控制电路160的列地址来选择字线,并对经选择的字线施加电压。在列方向延伸的多个字线与对应的柱200电连接。行选择/驱动电路130根据来自控制电路160的行地址来选择位线。传感电路140在读出操作时,对在由列选择/驱动电路120及行选择/驱动电路130所选择的存储器单元的位线对中流动的电流或电压进行传感,并经由内部数据总线170而朝控制电路160输出表示其传感结果的数据。写入/读出偏压电路150在读出操作时,对选择存储器单元的位线对施加用于读出操作的偏压,另外,在写入操作时,根据已从控制电路160接收的写入数据,对选择存储器单元的位线对施加设置或重置的偏压。

控制电路160包含硬件和/或软件,控制各部的运行。在某一实施方式中,控制电路160包括包含唯读存储器(Read Only Memory,ROM)/随机存取存储器(Random AccessMemory,RAM)的微控制器、微处理器、或状态机(state machine)等,例如通过执行已被存放在ROM/RAM的软件来控制读出操作、写入操作(设置、重置)等。另外,控制电路160通过内部数据总线170来与各部连接,朝各部供给已从外部接收的数据(包含地址),另外,朝外部输出已从传感电路140接收的读出数据。

对本实施例的可变电阻式存储器的详细的运行进行说明。图6(A)以及图6(B)表示选择了某一存储器单元时的存取用晶体管与可变电阻元件的连接关系。此处,设为通过列选择/驱动电路120来选择与存储器单元MC0的柱200连接的字线WL0,通过行选择/驱动电路130来选择位线对BL0/BL1者。若对字线WL0施加正的某一电压,则经由栅极绝缘膜222而对半导体膜224施加电场,半导体膜224的整体反转成N型,形成通道区域。其结果,半导体膜224经由可变电阻元件226的外侧的电极区域而与位线BL0电连接,另外,在与可变电阻元件226的电极区域相向的区域中,已反转成N型的通道区域与作为N型的多晶硅层的位线BL1电连接。

在位线BL0与半导体膜224之间的电流路径K0,形成由可变电阻元件226所形成的电阻成分R0,位线BL1与半导体膜224之间的电流路径K1是由N型的多晶硅所形成的低电阻区域。图6(B)是图6(A)的等效电路图,选择存储器单元MC0在一对位线BL0/BL1间包含一个存取用晶体管、且在其一者包含电阻成分R0,构成1R1T的存储器单元。

在列方向与选择存储器单元MC0邻接的存储器单元MC1和选择存储器单元MC0共有位线BL1,但字线WL1为非选择(对字线WL1施加GND电位或比阈值低的电压),在半导体膜224未形成反转层,存储器单元MC1的存取用晶体管保持关闭。因此,位线BL1事实上与非选择存储器单元MC1隔离,而避免潜行电流通路的形成。

另外,在行方向与选择存储器单元MC0邻接的存储器单元MC2和选择存储器单元MC0共有位线对BL0/BL1,但字线WL2为非选择,在位线对BL0/BL1与半导体膜224之间形成PN障壁,存取用晶体管保持关闭。因此,位线对BL0/BL1事实上与非选择存储器单元MC2(在行方向共有位线对BL0/BL1的其它非选择存储器单元也一样)隔离,而避免潜行电流通路的形成。

对选择存储器单元MC0的写入操作进行说明。写入/读出偏压电路150根据来自控制电路160的写入数据,对选择存储器单元MC0进行设置或重置的写入。在设置写入中,列选择/驱动电路120对选择字线WL0施加写入电压Vset,对非选择字线施加GND。写入/读出偏压电路150对一个选择位线BL0施加设置写入电压Vs(Vset>Vs),对另一个选择位线BL1施加GND。由此,从位线BL0朝位线BL1施加电压,可变电阻元件226即电流路径K0上的电阻成分R0被编程为低电阻状态。

在重置写入中,对位线对BL0/BL1施加与设置写入时不同的极性的电压。即,列选择/驱动电路120对选择字线WL0施加写入电压Vrset,对非选择字线施加GND。写入/读出偏压电路150对一个选择位线BL0施加GND,对另一个选择位线BL1施加重置写入电压Vr(Vrset>Vr)。由此,从位线BL1朝位线BL0施加电压,可变电阻元件226即电流路径K0上的电阻成分R0被编程为高电阻状态。

在选择存储器单元MC0的读出操作中,列选择/驱动电路120对选择字线WL0施加读出电压Vread,对非选择字线施加GND。写入/读出偏压电路150对一个选择位线BL0施加读出电压Vbl,对另一个选择位线BL1施加GND。若可变电阻元件226为低电阻状态(设置),则从选择位线BL0朝选择位线BL1流入大的电流,若可变电阻元件为高电阻状态(重置),则从选择位线BL0朝选择位线BL1流入小的电流。传感电路140对选择位线对BL0/BL1间的电流或电压进行传感,并将对应于传感结果的数据“0”、数据“1”作为读出数据经由内部数据总线170而朝控制电路160输出。

在所述实施例中,将可变电阻元件226形成为大致半圆状,但其为一例,可变电阻元件226只要是至少包括与位线BL0电接触的区域的形状即可。另外,在所述实施例中,将可变电阻元件226与位线BL0连接,将半导体膜224与位线BL1连接,但其为一例,也可以将半导体膜224与位线BL0连接,将可变电阻元件226与位线BL1连接。

对本发明的第二实施例进行说明。所述实施例表示了随机存取一个存储器单元的例子,但第二实施例涉及一种可同时存取多个存储器单元的阵列构成。此种阵列构成适合于所谓的交叉阵列。

图7(A)以及图7(B)中表示第二实施例的存储器单元阵列的一部分的电路构成。配置在列方向的存储器单元MC0~存储器单元MC3交替地连接在字线WL0、字线WL1,当选择了字线WL0时,如图7(A)所示,存储器单元MC0、存储器单元MC2的存取用晶体管开启(即,在半导体膜224形成反转层)。另一方面,当选择了字线WL1时,如图7(B)所示,存储器单元MC1、存储器单元MC3的存取用晶体管开启。写入/读出偏压电路150对经选择的位线对的一个位线施加读出电压Vbl、设置写入电压Vs、重置写入电压Vr,使另一个位线虚拟接地。

当通过列选择/驱动电路120而选择了一个字线时,与选择字线连接的多个存储器单元的存取用晶体管被同时开启,可一次性读出已被储存在多个存储器单元的多个数据、或将多个数据一次性写入多个存储器单元。例如,此种多个数据的输入/输出可用于交叉阵列的矩阵运算。

即便在列方向邻接的存储器单元间共有位线,由于在选择存储器单元之间存在非选择存储器单元,且非选择存储器单元的存取用晶体管关闭,因此选择存储器单元的位线对不被非选择存储器单元干涉,可施加所期望的偏压。另外,虽然在此处省略图示,但在行方向共有位线的非选择存储器的存取用晶体管也关闭,因此选择存储器单元的选择位线对不被非选择存储器单元干涉,而抑制形成不期望的潜行电流通路。

图8是立体地表示图7(A)以及图7(B)中所示的阵列构成者,此处,表示经堆叠的垂直方向的两段的位线。阵列的基本的操作与图7(A)以及图7(B)时相同。当通过选择字线WL0而选择了存储器单元MC2_0、存储器单元MC2_1时,存储器单元MC2_0、存储器单元MC2_1的存取用晶体管被开启,位线对BL1_0/BL2_0与位线对BL1_1/BL2_1被选择。当通过选择字线WL1而选择了存储器单元MC1_0、存储器单元MC1_1时,存储器单元MC1_0、存储器单元MC1_1的存取用晶体管被开启,位线对BL0_0/BL1_0与位线对BL0_1/BL1_1被选择。

图9是表示存储器单元阵列的柱与字线的优选的连接例的概略立体图。字线WL0与配置在列方向的多个柱200的上端部每隔一个来连接,字线WL1与未由字线WL0连接的柱200的下端部每隔一个来连接。字线WL0、字线WL1可为导电性的多晶硅或金属层。将柱200从柱200的上下方向交替地连接在字线WL0、字线WL1,由此与将字线WL0、字线WL1配线在同一平面的情况相比,可谋求存储器单元阵列的高集积化,并削减存储器单元阵列的水平方向的占有面积。

图10是表示将本实施例的存储器单元阵列层叠在基板上的例子的概略剖面图。作为基板,例如使用硅基板300,在所述硅基板300上形成三维结构的存储器单元阵列310。在硅基板300的表面或其内部形成列选择/驱动电路120、行选择/驱动电路130、传感电路140、写入/读出偏压电路150及控制电路160等的周边电路320。存储器单元阵列310的经选择的柱200、经选择的位线210及经选择的字线等经由多层配线结构而与周边电路320的列选择/驱动电路120、行选择/驱动电路130、传感电路140、写入/读出偏压电路150及控制电路160电连接。多层配线结构包含多个导电层(多晶硅层及金属层)、多个层间绝缘膜、形成在层间绝缘膜的通孔(或接触孔)、形成在通孔内的插塞等,可将在垂直方向层叠的位线或字线与周边电路320电连接。

在某一实施方式中,在硅基板300上形成绝缘层330,在绝缘层330上形成导电层340,在导电层340上形成存储器单元阵列310。导电层340例如提供存储器单元阵列310的共同的源极(GND电位)或电源线。导电层340例如包含N型的多晶硅层、或金属层与N型的多晶硅层的层叠。如此,在硅基板300形成周边电路320,在其上方层叠存储器单元阵列310,由此可减小存储器晶片的二维的面积。

对本发明的优选的实施方式进行了详述,但本发明并不限定于特定的实施方式,可在权利要求中记载的本发明的主旨的范围内进行各种变形及变更。

- 可变电阻式存储器装置及其制造方法

- 可变电阻式存储器及其制造方法