时钟恢复电路及方法、数据处理芯片、电子设备

文献发布时间:2023-06-19 11:49:09

技术领域

本发明涉及电路技术领域,尤其涉及一种时钟恢复电路及方法、数据处理芯片、电子设备。

背景技术

时钟恢复的目的是跟踪发送端的时钟漂移和一部分抖动,以确定正确的数据采样。时钟恢复电路(Clock Data Recovery,CDR)通常通过锁相环(phase lock loop,PLL)电路的方式实现。

但是,现有的时钟恢复电路恢复出的时钟信号的精确度较低。

发明内容

本发明实施例解决的是时钟恢复电路恢复出的时钟信号的精确度较低的技术问题。

为解决上述技术问题,本发明实施例提供一种时钟恢复电路,应用于C-PHY,包括:锁存模块、单稳模块以及反相逻辑单元,其中:所述锁存模块,其第一置位端S输入多组脉冲信号,在其中任一组脉冲信号由低电平跳变至高电平时,锁存上升沿并经由其第一输出端输出;所述反相逻辑单元,其输入端与所述锁存模块的第一输出端耦接,其第一输出端与所述锁存模块的第一复位端RN耦接,其第二输出端与所述锁存模块的第二置位端SN耦接;所述单稳模块,其第一输入端与所述反相逻辑单元的第一输出端耦接,其第二输入端输入电压电源,其输出端与所述锁存模块的第二复位端R耦接;所述第一复位端RN的输入信号与所述第二复位端R的输入信号反相。

可选的,所述锁存模块包括:第一PMOS管、第二PMOS管、第一NMOS管、第二NMOS管、第三NMOS管、第四NMOS管、第五NMOS管以及第六NMOS管,其中:所述第一PMOS管,其栅极与所述锁存模块的第二输出端耦接,其漏极与所述第一NMOS管的漏极耦接,其源极输入所述电源电压;所述第二PMOS管,其栅极与所述锁存模块的第一输出端耦接,其漏极与所述第二NMOS管的漏极耦接,其源极输入所述电源电压;所述第一NMOS管,其栅极与所述锁存模块的第二输出端耦接,其源极接地;所述第二NMOS管,其栅极与所述锁存模块的第一输出端耦接,其源极与地耦接;所述第三NMOS管,其栅极与所述锁存模块的输入端耦接,其漏极与所述锁存模块的第二输出端耦接,其源极与所述第四NMOS管的漏极耦接;所述第四NMOS管,其栅极与所述锁存模块的第一复位端RN耦接,其源极接地;所述第五NMOS管,其栅极与所述锁存模块的第二复位端R耦接,其漏极与所述锁存模块的第一输出端耦接,其源极与所述第六NMOS管的漏极耦接;所述第六NMOS管,其栅极与所述锁存模块的第二置位端SN耦接,其源极接地。

可选的,所述单稳模块包括与非门电路、第三反相器、延时电路以及或非门电路,其中:所述与非门电路,其第一输入端与所述单稳模块的第一输入端耦接,其第二输入端与所述单稳模块的第二输入端耦接,其输出端与所述第三反相器的输入端耦接;所述第三反相器,其输出端与所述或非门电路的第一输入端耦接;所述延时电路,其输入端与所述反相逻辑单元的第一输出端耦接,其输出端与所述或非门电路的第二输入端耦接;所述或非门电路,其输出端与所述单稳模块的输出端耦接。

可选的,所述时钟恢复电路还包括:时间数值转换电路,与所述延时电路的控制端耦接,适于对所述延时电路的延时时长进行控制。

可选的,所述时钟恢复电路还包括:缓冲模块,输入端与所述时钟恢复电路的输出端耦接,适于对所述时钟恢复电路的输出时钟信号进行驱动并输出。

可选的,所述缓冲模块包括第四反相器以及第五反相器,其中:所述第四反相器,其输入端与所述反相逻辑单元的第一输出端耦接,其输出端与所述第五反相器的输入端耦接;所述第五反相器,其输出端输出进行过驱动后的所述时钟信号;所述第五反相器的驱动系数大于所述第四反相器的驱动系数。

可选的,当所述锁存模块的第一复位端RN输入高电平时,所述锁存模块通过所述第一置位端S置位;当所述锁存模块的第二置位端SN输入高电平时,所述锁存模块通过所述第二复位端R复位。

可选的,所述锁存模块的第一复位端RN将第二复位端R置为高电平的时间位于所述第一置位端S置位结束的时间。

可选的,所述反相逻辑单元包括第一反相器以及第二反相器,其中:所述第一反相器,其输入端为所述反相逻辑单元的输入端,其输出端为所述反相逻辑单元的第一输出端;所述第二反相器,其输入端与所述第一反相器的输出端耦接,其输出端为所述反相逻辑单元的第二输出端。

本发明实施例还提供了一种数据处理芯片,包括上述任一种所述的时钟恢复电路。

本发明实施例还提供了一种电子设备,包括上述的数据处理芯片。

本发明实施例还提供了一种时钟恢复方法,包括:在检测到输入的多组脉冲信号时,检测所述多组脉冲信号的宽度;将所述多组脉冲信号的宽度进行编码,并将编码结果发送至时钟恢复电路,以控制所述时钟恢复电路中单稳模块的暂态时间。

与现有技术相比,本发明实施例的技术方案具有以下有益效果:

时钟恢复电路包括锁存模块、单稳模块以及反相逻辑单元,通过锁存模块锁存其第一置位端输入的多组脉冲信号,当任一组脉冲信号从低电平跳变至高电平时,将其上升沿锁存。反相逻辑单元的第一输出端对锁存模块的第一输出端的输出信号进行反相,反相逻辑单元的第二输出端对其第一输出端的输出信号反相。单稳模块的第一输入端输入经过反相的锁存模块的第一输出端的输出信号,并经过单稳模块的延时路径得到稳定的延时,从而实现精准的时钟恢复。

附图说明

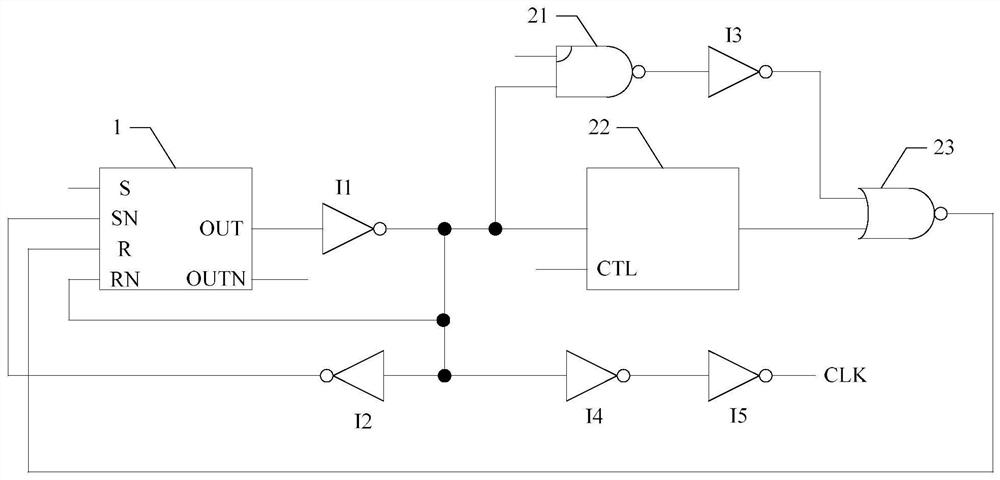

图1是本发明实施例中的一种时钟恢复电路的结构示意图;

图2是本发明实施例中的一种锁存模块的结构示意图。

具体实施方式

如上述背景技术中所述,现有的时钟恢复电路恢复出的时钟信号的精确度较低。

在本发明实施例中,时钟恢复电路包括锁存模块、单稳模块以及反相逻辑单元,通过锁存模块锁存其第一置位端输入的多组脉冲信号,当任一组脉冲信号从低电平跳变至高电平时,将其上升沿锁存。反相逻辑单元的第一输出端对锁存模块的第一输出端的输出信号进行反相,反相逻辑单元的第二输出端对其第一输出端的输出信号反相。单稳模块的第一输入端输入经过反相的锁存模块的第一输出端的输出信号,并经过单稳模块的延时路径得到稳定的延时,从而实现精准的时钟恢复。

为使本发明的上述目的、特征和有益效果能够更为明显易懂,下面结合附图对本发明的具体实施例做详细的说明。

本发明实施例提供了一种时钟恢复电路,应用于C-PHY。在具体实施中,时钟恢复电路可以包括:锁存模块1、单稳模块以及反相逻辑单元。

在本发明实施例中,锁存模块1的第一置位端为S端,其可以输入多组脉冲信号。当其中的任一组脉冲信号由低电平跳变至高电平时,锁存模块1可以锁存上升沿,并经由锁存模块1的第一输出端OUT输出。

反相逻辑单元的输入端可以与锁存模块1的第一输出端耦接,反相逻辑单元的第一输出端与锁存模块1的第一复位端RN耦接,反相逻辑单元的第二输出端与锁存模块1的第二置位端SN耦接。

单稳模块的第一输入端与反相逻辑单元的第一输出端耦接,单稳模块的第二输入端输入电源电压,单稳模块的输出端与锁存模块1的第二复位端R耦接。

在具体实施中,第一复位端RN的输入信号与第二复位端R的输入信号反相。

参照图2,给出了本发明实施例中的一种锁存模块1的结构示意图。

在本发明实施例中,锁存模块1可以包括第一PMOS管MP1、第二PMOS管MP2、第一NMOS管MN1、第二NMOS管MN2、第三NMOS管MN3、第四NMOS管MN4、第五NMOS管MN5以及第六NMOS管MN6,其中:

第一PMOS管MP1的栅极可以与锁存模块1的第二输出端OUTN耦接,第一PMOS管MP1的漏极可以与第一NMOS管MN1的漏极耦接,第一PMOS管MP1的源极可以输入电源电压;

第二PMOS管MP2的栅极可以与锁存模块1的第一输出端耦接,第二PMOS管MP2的漏极可以与第二NMOS管MN2的漏极耦接,第二PMOS管MP2源极可以输入电源电压;

第一NMOS管MN1的栅极可以与锁存模块1的第二输出端OUTN耦接,第一NMOS管MN1的漏极可以与第一PMOS管MP1的漏极耦接,第一NMOS管MN1的源极接地;

第二NMOS管MN2的栅极可以与锁存模块1的第一输出端耦接,第二NMOS管MN2的漏极可以与第二PMOS管MP2的漏极耦接,第二NMOS管MN2的源极接地;

第三NMOS管MN3的栅极可以与锁存模块1的输入端耦接,第三NMOS管MN3的漏极可以与锁存模块1的第二输出端耦接,第三NMOS管MN3的源极可以与第四NMOS管MN4的漏极耦接;

第四NMOS管MN4的栅极可以与锁存模块1的第一复位端RN耦接,第四NMOS管MN4的漏极可以与第三NMOS管MN3的源极耦接,第四NMOS管MN4的源极接地;

第五NMOS管MN5的栅极可以与锁存模块1的第二复位端R耦接,第五NMOS管MN5的漏极可以与锁存模块1的第一输出端耦接,第五NMOS管MN5的源极可以与第六NMOS管MN6的漏极耦接;

第六NMOS管MN6的栅极可以与锁存模块1的第二置位端SN耦接,第六NMOS管MN6的漏极可以与第五NMOS管MN5的源极耦接,第六NMOS管MN6的源极接地。

在具体实施中,当锁存模块1的第一复位端RN输入高电平时,锁存模块1通过第一置位端S置位;当锁存模块1的第二置位端SN输入高电平时,锁存模块1通过第二复位端R复位。

在具体实施中,锁存模块1的第一复位端RN与第二复位端R置为高电平的时间可以位于第一置位端S置位结束的时间。也就是说,当第一置位端S置位结束时,可以将锁存模块1的第一复位端RN与第二复位端R置为高电平。

在本发明实施例中,当锁存模块1的第一置位端S输入一组脉冲信号时,第一复位端RN默认为高电平,第二置位端SN默认为低电平,第二复位端R默认为低电平。当一组脉冲信号中的第一个上升沿到来时,锁存模块1的输出端被置为高电平,锁存模块1置位。当锁存模块1的输出端被置为高电平后,第一复位端RN被置为低电平,第二置位端SN被置为高电平,锁存模块1不受第一置位端S的控制,将一组脉冲信号中的第一个上升沿锁存。第一复位端RN的信号的下降沿经过延时后形成复位信号,第二复位端R置为高电平。由于此时第二置位端处于高电平状态,则锁存模块1的输出端被置为低电平,锁存模块1复位。当锁存模块1的输出端被置为低电平之后,第一复位端RN被置为高电平,第二置位端SN被置为低电平,第一复位端RN的信号的上升沿不经过延时形成复位信号,将第二复位端R置为低电平,回到默认状态,等待下一组脉冲信号。

在本发明实施例中,单稳模块可以包括与非门电路21、第三反相器I3、延时电路22以及或非门电路23,其中:

与非门电路21的第一输入端可以与单稳模块的第一输入端耦接,与非门电路21的第二输入端可以与单稳模块的第二输入端耦接,与非门电路21的输出端可以与第三反相器I3的输入端耦接;

第三反相器I3的输入端可以与与非门电路21的输出端耦接,第三反相器I3的输出端可以与或非门电路23的第一输入端耦接;

延时电路22的输入端可以与反相逻辑单元的第一输出端耦接,延时电路22的输出端可以与或非门电路23的第二输入端耦接;

或非门电路23的输出端可以与单稳模块的输出端耦接。

在具体实施中,单稳模块可以包括延时路径以及非延时路径。延时路径对应延时电路22的延时时长不为0,非延时路径对应延时电路22的延时时长为0。通过延时路径以及非延时路径,可以控制复位操作的时间。

在本发明实施例中,反相逻辑单元的第一输出端输出的信号输入至锁存模块1的第一复位端RN,因此,单稳模块的第一输入端输入的信号实质上与锁存模块1的第一复位端RN输入的信号相同。锁存模块1的第一输出端的输出信号的上升沿经过延时路径,得到延时后的高位复位信号;锁存模块1的第一输出端的输出信号的下降沿经过非延时路径,得到低位复位信号。

在本发明实施例中,反相逻辑单元可以包括第一反相器I1以及第二反相器I2,其中:

第一反相器I1的输入端可以为反相逻辑单元的输入端,第一反相器I1的输出单可以为反相逻辑单元的第一输出端;

第二反相器I2的输入端可以与第一反相器I1的输出端耦接,第二反相器I2的输出端可以为反响逻辑单元的第二输出端。

在具体实施中,时钟恢复电路还可以包括时间数值转换电路。时间数值转换电路可以与延时电路22的控制端CTL耦接,通过时间数值转换电路,对延时电路22的延时时长进行控制。

也就是说,通过时间数值转换电路,将所需要设置的延时时长输入至延时电路22,实现对延时电路22的控制。

在具体实施中,时钟恢复电路还可以包括缓冲模块,缓冲模块的输入端可以与时钟恢复电路的输出端耦接。通过缓冲模块,可以对时钟恢复电路的输出时钟信号进行驱动,增加时钟恢复电路的输出时钟信号的驱动能力。

在本发明实施例中,缓冲模块可以包括第四反相器I4以及第五反相器I5,其中:

第四反相器I4的输入端可以与反向逻辑单元的第一输出端耦接,第四反相器I4的输出端可以与第五反相器I5的输入端耦接;

第五反相器I5的输入端可以与第四反相器I4的输出端耦接,第五反相器I5的输出端可以输出经过驱动后的时钟信号CLK。

在具体实施中,第四反相器I4与第五反相器I5可以具备不同的驱动系数。在本发明实施例中,第五反相器I5的驱动系数可以大于第四反相器I4的驱动系数。

本发明实施例还提供了一种数据处理芯片,所述数据处理芯片包括上述实施例中提供的时钟恢复电路。

本发明实施例还提供了一种电子设备,包括上述所述的数据处理芯片。

本发明实施例还提供了一种时钟恢复方法,包括:在检测到输入的多组脉冲信号时,检测所述多组脉冲信号的宽度;将所述多组脉冲信号的宽度进行编码,并将编码结果发送至时钟恢复电路,以控制时钟恢复电路中单稳模块的暂态时间。

在具体实施中,上述时钟恢复方法中所涉及到的时钟恢复电路可以为本申请上述实施例中提供的时钟恢复电路。

虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

- 时钟恢复电路及方法、数据处理芯片、电子设备

- 时钟数据恢复电路、处理芯片及电子设备