一种防穿通驱动电路

文献发布时间:2023-06-19 13:46:35

技术领域

本发明属于模拟集成电路技术领域,具体涉及一种防穿通驱动电路。

背景技术

在模拟集成电路中,功率级栅极驱动电路功率开关管是功率转换、LED驱动等芯片的核心电路之一;其他功能模块中也会需要放大控制信号驱动后级晶体管,驱动电路的特征直接影响开关电源工作的安全可靠性和性能指标。

采用同步整流技术的开关电源电路中,为了保证上下管不同时开启,避免造成穿通损坏电路,需要在开关转换过程中设置死区时间以保护电路安全工作;非功率级驱动中,为了保证后续电路的正常开关,仍需要保证充放电驱动级上下管不同时开启,也需要死区时间。传统的固定死区时间虽然在设计上较为简单,但是为了保证所有条件下都不发生上下功率管穿通的情况,需要将死区时间设计的相当长,这样不可避免地会产生较长时间的体二极管导通,增大了功率损耗。死区时间设置的不合理是产生功率损失的主要原因之一,为了尽量减小这种体二极管导通对电路性能的影响,需要引入自适应死区时间技术优化死区时间,提高转换效率。由于上下拉电流峰值均为安培级别,当下功率管完成开关转换时,同样需要对上下拉MOSFET设置死区时间,以防止发生电流穿通。

发明内容

本发明的目的就是为了解决传统的驱动电路存在的上述问题,提出一种防穿通的驱动电路结构。

为实现上述目的,本发明的技术方案为:

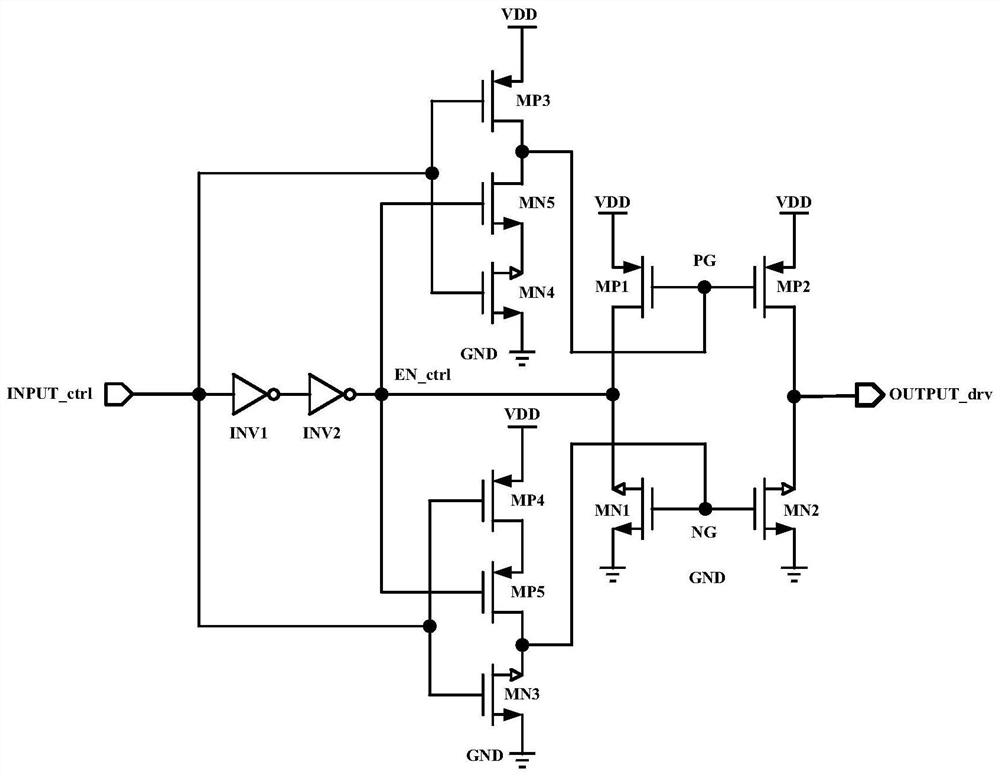

一种防穿通驱动电路,如图1所示,包括第一PMOS管、第二PMOS管、第三PMOS管、第四PMOS管、第五PMOS管、第一NMOS管、第二NMOS管、第三NMOS管、第四NMOS管、第五NMOS管、第一反相器和第二反相器;第一反相器的输入端接输入控制信号,第一反相器的输出端接第二反相器的输出端,第二反相器的输出端接第一PMOS管漏极、第一NMOS管漏极、第五NMOS管栅极和第五PMOS管栅极;第一PMOS管源极接电源,其栅极接第三PMOS管漏极;第二PMOS管源极接电源,其栅极接第三PMOS管漏极,第二PMOS管漏极接第二NMOS管漏极;第二NMOS管栅极接第五PMOS管漏极,第二NMOS管源极接地;第三PMOS管源极接电源,其栅极输入控制信号,其漏极接第五NMOS管漏极;第五NMOS管源极接第四NMOS管漏极,第四NMOS管栅极接输入控制信号,其源极接地;第四PMOS管源极接电源,其栅极接输入控制信号,其漏极接第五PMOS管源极;第五PMOS管漏极接第三NMOS管漏极,第三NMOS管栅极接输入控制信号,其源极接地;第一NMOS管的栅极接第五PMOS管漏极,第一NMOS管的源极接地;第二NMOS管的栅极接第五PMOS管的漏极,其源极接地;第二PMOS管漏极和第二NMOS管漏极的连接点为驱动电路输出端输出驱动信号。

上述方案中,通过带使能管的反相器和电流竞争将单个输入控制信号分为两个有自适应死区时间的控制信号,防止了P/N型驱动管MN2/MP2的上下穿通问题。MN1和MP1的电流大小反应驱动管MN2和MP2的开关状态,通过MN1和MP1和INV2的电流竞争,决定使能管控制信号EN_ctrl,决定何时开启上控制支路的下拉和下控制支路的上拉。使能管控制信号EN_ctrl延迟于输入控制信号INPUT_ctrl一定时间后跳变,控制驱动管栅极信号PG和NG的开关,使MP2和MN2的开启时间没有重叠部分,具有自适应死区时间,防止了上下管的穿通。

本发明的有益效果为,本发明采用自适应死区时间的防穿通驱动策略,避免了死区时间过长或过短造成的功率损耗等问题,使功率管或驱动管可以实现可靠的开关动作,确保了自适应死区驱动电路的可靠性。

附图说明

图1为本发明的防穿通驱动电路的原理图;

图2为本发明中的基本时序逻辑图。

具体实施方式

下面结合附图,对本发明技术方案进行详细描述:

如图1所示,电路中的VDD为电源电压,INPUT_ctrl为输入控制信号,EN_ctrl为反相器中使能管的使能控制信号,PG为MP1和MP2的栅极信号,NG为MN1和MN2的栅极信号,OUTPUT_drv为输出驱动信号。MN1和MP1栅极与MN2和MP2连接,MN2和MP2的栅极NG和PG通过控制MN1和MP1的电流大小反应驱动管MN2和MP2的开关状态。MN5和MP5做反相器中的使能管,只有当EN_ctrl和INPUT_ctrl同相时才会控制反相器正常开关。INPUT_ctrl经过INV1和INV2得到EN_ctrl,但因为MN1和MP1的电流大小反应驱动管MN2和MP2的开关状态,且MN1的下拉能力强于INV2中P管的上拉能力,MP1的上拉能力强于INV2中N管的下拉能力,所以EN_ctrl的实际电位受NG和PG控制。具体的时序逻辑图如图2所示。

当INPUT_ctrl跳为高电平信号时,MN3开启,开始对MN1与MN2的栅极NG放电,此时MN1的电流能力强于INV1的电流能力,EN_ctrl仍为低电平,因此MN5关断,故MP2保持为关断状态。当MN2与MN1的栅极电压NG下降到(为阈值电压附近)使得MN1与MN2关断时,MN1关断,此时INV1的电流能力强于MN1的电流能力,进而使得EN_ctrl跳为高电平,MN5开启,由于INPUT_ctrl为高电平,故MN4开启,从而使得MP1和MP2的栅极电压PG开始下降,最终使得MP2开启。MN2关断到MP2开启之间的时间为死区时间。

当INPUT_ctrl跳为低电平信号时,MP3开启,开始对MP1与MP2的栅极PG充电,此时MP1的电流能力强于INV1的电流能力,EN_ctrl仍为高电平,因此MP5关断,故MN2保持为关断状态。当MP2与MP1的栅极电压PG上升到(为VDD减去阈值电压附近)使得MP1与MP2关断时,MP1关断,此时INV1的电流能力强于MP1的电流能力,进而使得EN_ctrl跳为低电平,MP5开启,由于INPUT_ctrl为低电平,故MP4开启,从而使得MN1和MN2的栅极电压NG开始上升,最终使得MN2开启,输出信号跳低。MP2关断到MN2开启之间的时间为死区时间。

通过对防穿通驱动开关过程的分析可以看出防穿通驱动的自适应死区时间有效防止了上下驱动管的同时开启导通,避免了死区时间过长或过短造成的功率损耗等问题,使功率管或驱动管可以实现可靠的开关动作。