编程电抗部件

文献发布时间:2023-06-19 10:14:56

背景技术

可以在制造期间调节模拟和数字电路,以设定电路性能参数和/或改变电路配置。熔断器、电可擦除可编程只读存储器(EEPROM)和一次性可编程(OTP)存储器可以用于微电子器件制造期间的修整和/或编程不同的产品选项。然而,那些存储器元件和/或熔断器通常需要额外的掩模步骤以及更多的管芯面积、成本和复杂性,这限制了产品的灵活性和可靠性,和/或需要精确的特殊多次通过测试和编程程序以确保可靠性。

发明内容

电子器件制造和配置方法包括执行增材沉积工艺,该增材沉积在经处理的晶片金属化结构的表面上方沉积材料,以设定或调节经处理的晶片的电容器、电感器、电阻器、天线和/或热部件的电路。

附图说明

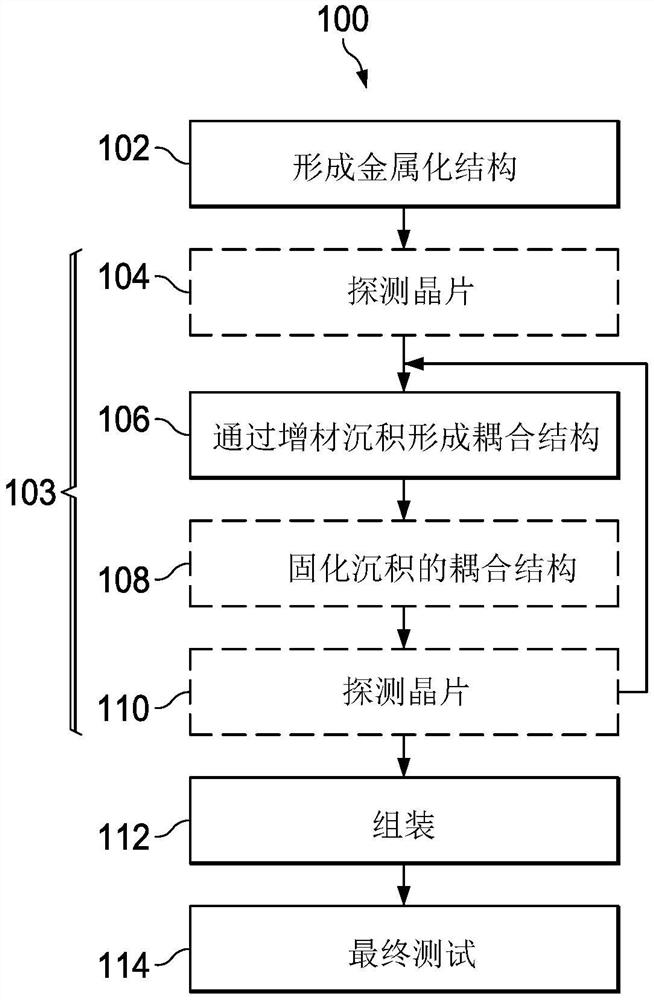

图1是制造微电子器件的方法的流程图。

图2是经处理的晶片的局部侧视图,该晶片具有增材沉积在金属化结构上方的介电材料以设定或调节包括在金属化结构中形成的横向电容器的电路。

图3是经处理的晶片的局部侧视图,该晶片具有增材沉积在金属化结构上方的导电材料以设定或调节包括在金属化结构中形成的横向电容器的电路。

图4是经处理的晶片的局部俯视平面图,该晶片具有沉积在金属化结构上方的磁性材料以设定或调节包括在金属化结构中形成的平面电感器的电路。

图5是经处理的晶片的局部俯视平面图,该晶片具有沉积在金属化结构上方的磁性材料以设定或调节在金属化结构中形成的两个导电特征件之间的磁耦合。

图6是经处理的晶片的局部俯视平面图,该晶片具有沉积在金属化结构上方的磁性材料以设定或调节在金属化结构中形成的第一平面电感器和第二平面电感器之间的磁耦合。

图7是经处理的晶片的局部俯视平面图,该晶片具有沉积在金属化结构上方的磁性、导电、介电和/或电阻材料以设定或调节具有在金属化结构中形成的部件的并联RLC储能电路。

图8是经处理的晶片的局部侧视图,该晶片具有沉积在金属化结构上方的导电材料以设定或调节在金属化结构中形成的天线电路。

图9是经处理的晶片的局部侧视图,该晶片具有沉积在金属化结构上方的半导体材料以设定或调节在金属化结构中形成的天线电路。

图10是经处理的晶片的局部侧视图,该晶片具有沉积在金属化结构上方的导热材料以设定或调节在金属化结构中形成的热回路。

图11是沿图6的线11-11截取的示例经处理的晶片的局部截面侧视图,该晶片具有沉积在金属化结构上方的磁性材料,以设定或调节在金属化结构中不同层级处形成的第一平面电感器和第二平面电感器之间的磁耦合。

图12是沿图5的线12-12截取的另一示例经处理的晶片的局部截面侧视图,该晶片具有沉积在金属化结构上方的顶表面的低洼区域中的磁性材料,以设定或调节在金属化结构中形成的第一导电特征件和第二导电特征件之间的磁耦合。

图13是另一示例经处理的晶片的局部截面侧视图,该晶片具有通过在金属化结构上方进行增材三维沉积而形成的磁性材料,以设定或调节在金属化结构中形成的第一导电特征件和第二导电特征件之间的磁耦合。

具体实施方式

在附图中,相似的附图标记始终指代相似的元件,并且各种特征不必按比例绘制。同样,在本说明书中,术语“耦合”或“耦接”包括间接或直接的电连接或机械连接或其组合。例如,如果第一器件、部件或结构耦合到第二器件、结构或部件或与第二器件、结构或部件耦合,则该连接可以是通过直接电连接,或者是通过经由一个或多个中间结构、器件和/或连接的间接电连接。

图1示出制造和配置微电子器件(诸如具有集成电路(IC)的微电子器件)的方法100。与熔断器、EEPROM或OTP存储器不同,方法100使用印刷或其它增材沉积处理来在经处理的晶片(诸如硅晶片或绝缘体上硅(“SOI”)晶片)的金属化结构的表面(例如,顶表面)上方形成材料结构,以设定或调节晶片的电子部件的电路。所描述的方法的示例有益于在制造期间设定或调节与在金属化结构中形成的一个或多个部件相关联的值或参数。所描述的示例有益于调节各种模拟电路修整应用(包括RF电路、变压器电路、热回路等)中的电抗或其它电子部件。

方法100包括在最终组装和封装之前,在102处制作具有金属化结构的晶片,并在103处配置经处理的晶片的电子部件的电路。在102处的晶片制作包括在半导体衬底上或半导体衬底中形成电子部件,以及金属化处理以在衬底上方形成具有其它电子部件或其部分的金属化结构。金属化处理包括形成导电布线结构连接到的一个或多个介电层,和/或形成一个或多个电子部件以提供经处理的晶片。金属化结构提供了晶片的顶表面,该顶表面暴露出一些导电布线结构,用于随后的键合线连接以及与随后沉积的材料结构的欧姆连接。金属化结构的顶表面不需要是平面的。在一些示例中,顶表面暴露最上层金属化层的导电布线结构。在102处的晶片制作包括在晶片表面的选定部分上方形成钝化层(例如,氧化物、氧氮化物、聚酰胺、氮化物材料等)。随后的增材沉积处理创建了可以电连接到暴露的导电布线结构和/或可以覆在具有中间钝化层材料的此类结构上的材料结构。钝化层覆盖顶表面的选定部分,并使导电布线结构的部分暴露。

示例方法100包括电路配置方法103作为制造工艺的一部分。在103处的配置处理包括使用增材沉积来配置(例如,设定或调节)经处理的晶片的电子部件的电路。该配置包括设定或调节电子部件的值和/或设定或调节电路配置和/或连接。示例包括创建或修改部件或部件的导电特征件之间的电容耦合或磁耦合,创建或修改部件或其特征件的串联和/或并联连接,创建或修改天线结构,创建或修改热回路中导热路径等。

在103处的配置处理包括在104处执行第一晶片探针测试,该第一晶片探针测试测量至少一个电子部件的电路的参数。经处理的晶片包括多个管芯区域或区,该区域或区最终将被分割成分开的集成电路管芯,以用于随后封装以形成微电子器件。在该示例中,每个管芯区域包括:(a)在半导体衬底的管芯区域的相应部分上或之中和/或在经处理的晶片的金属化结构中形成的一个或多个电子部件;以及(b)金属化结构的导电布线结构,其用于为与探针机进行电互连以进行晶片探测操作提供外部通道。

在104处的第一晶片探针测试可以包括:(a)将探针信号施加到一个或多个探针电连接件;以及(b)测量与经处理的晶片的电子部件的电路相关联的一个或多个参数。在104处的示例探针测试识别相应管芯区域及其相关联的电路的可操作性和性能参数。探针测试可以识别出任何故障电路。如果管芯区域的相应电路包括用于自我修复的特征件(例如,备用存储器单元),则可以识别管芯区域以用于随后通过增材沉积来自我修复,如下文进一步所述。对于经处理的晶片的每个管芯区域,第一晶片探针测试104收集相应的修整或配置数据,以识别用于随后的增材沉积以设定或修改晶片的电路配置的位置。

在106处,方法100进一步包括在晶片的顶表面上(例如,直接在导电布线结构的一个或多个暴露部分上和/或在上层或最终金属化结构层的顶表面上的任何钝化层的部分上)沉积材料,以设定或调节经处理的晶片的至少一个电子部件的电路。在106处的沉积中使用的位置、尺寸和/或材料至少部分地根据(例如,响应于或基于)在104的任何晶片探针处理部分期间测量的一个或多个参数来确定。以该方式,根据晶片探针的结果,选择性地调节或设定所测量的经处理的晶片的电路状况或参数。

在106处,增材沉积工艺沉积材料以设定或调节各种不同电子部件的电路。可以通过在106处的沉积来修改的电子部件的示例包括电容器、电感器、电阻器、天线和热部件或其组合。在106处的沉积处理包括设定或调节沉积的材料的至少一个尺寸,以设定或调节晶片的至少一个电子部件的电路。

在106处的增材沉积提供了与晶片金属化结构的导电布线结构接近或接触的一个或多个结构的受控形成。在106处的沉积形成材料结构,该材料结构修改或设定电路配置或部件值,或者管芯中的部件的互连或耦合。

在各种实施方式中,可以在106处沉积一种或多种材料,诸如电导体、半导体、电阻材料、介电材料、磁性材料和/或导热材料或其组合。沉积的结构可以作为跳线或电阻器操作,诸如在经处理的晶片的金属化结构的第一导电布线结构和第二导电布线结构的暴露部分之间延伸。在其它示例中,沉积的结构从导电布线结构的暴露部分延伸至接近(例如但不接触)电气部件或电气部件的特征件的位置,以在经处理的晶片的电子部件之间提供电屏蔽、热屏蔽、散热、电容耦合或磁耦合(例如,电感耦合或变压器耦合)。例如,沉积的材料结构可以形成在经处理的晶片的金属化结构的导电布线结构之上的钝化层上方,以接近但不接触特定的导电布线结构。

在一些示例中,在106处的沉积用于沉积导体或介电材料,以选择性地设定或调节使用在晶片金属化结构中形成的横向电容器的电路中的电容。在一些示例中,执行106处的沉积以沉积磁性材料以选择性地设定或调节使用在晶片金属化结构中形成的平面电感器线圈结构的电路中的电感或磁耦合。在一些示例中,在106处的沉积用于沉积电阻材料以在导电布线结构的暴露部分之间形成电阻器或熔断。在106处的沉积包括沉积半导体材料以在第一导电布线结构的暴露部分与第二导电布线结构的暴露部分之间形成半导体结构。在其它示例中,在106处的沉积包括沉积导热材料以设定或修改晶片的热回路的热性能。增材沉积的材料与一个或多个金属化层的导电布线结构的暴露部分形成欧姆接触。调整增材沉积的材料,以创建与导电布线结构的材料(例如,铝、铜等)的具有受控金属-金属界面的欧姆接触,而无需产生肖特基二极管。

可以在不同的实施方式中执行不同的增材沉积工艺。在106处的沉积包括执行印刷工艺或其它增材沉积工艺以形成沉积的材料。在一些实施方式中,沉积的材料是由溶解颗粒制成的适于喷涂沉积的溶液。在106处的印刷工艺是喷墨工艺。在另一个示例中,在106处的印刷工艺是静电喷射工艺。在另一个示例中,在106处的印刷工艺是喷射分配工艺。在另一个示例中,在106处的印刷工艺是激光辅助沉积工艺。在另一个示例中,在106处的印刷工艺是喷涂工艺。在另一个示例中,在106处的印刷工艺是丝网印刷工艺。在106处执行多个印刷工艺,诸如以在晶片表面129上的不同位置中沉积多种不同的材料。在106处的工艺沉积包括金属的溶液(例如,纳米粒子、溶胶-凝胶、金属盐分解)。在106处的沉积工艺沉积电阻材料(例如,含碳材料(和所有同素异形体)、填充有碳/导电颗粒的聚合物、沉积的金属溶液)。在106处的沉积工艺沉积介电材料(例如,高介电常数(高K)材料,诸如包括PI、PBO、BCB、SU8、环氧树脂的聚合物,包括HBN、氧化物、钛酸钡的溶胶-凝胶陶瓷材料)。在106处的沉积工艺沉积磁性材料(例如,氧化铁、Ni、Co、磁铁矿)。在106处的沉积工艺沉积热传输改性材料(例如,高热常数(高热K)材料,诸如石墨烯、CNT、HBN、沉积的金属溶液、陶瓷)。

在图1的示例性方法100中,在108处执行固化工艺以固化在106处沉积的材料。在108处的处理包括预烘烤晶片并将沉积的材料暴露于紫外(UV)光以促进干燥并建立沉积的材料的期望材料特性。在其它实施方式中,可以省略在108处的可选固化处理。

图1的示例方法100包括在106处的增材沉积处理之后在110处执行第二晶片探针测试。在110处的第二晶片探针测试测量晶片的至少一个电子部件的电路的在104处的第一晶片探针中测试了的一个或多个电路参数。可以根据(例如,响应于或基于)在110处的第二晶片探针测试的结果,来执行进一步的增材沉积,连同106和108的任何固化处理部分。在其它示例中,可以省略110处的第二晶片探针处理。在另一个示例中,在106处印刷的材料:(a)在两个导电布线结构之间创建结构;以及(b)因此,在分别连接到这两个导电布线结构的电气部件之间创建结构。可以诸如在112处通过激光修整来去除全部或部分增材沉积的材料,以调节电子部件的电路。例如,可以在106处以初始宽度增材沉积电阻材料,并且然后在112处可以使用激光修整来使沉积的电阻材料变窄,从而增加电阻。在104处的初始晶片探针操作和/或在110处的随后晶片探针处理包括光学探针,以识别经处理的晶片的顶表面的形貌特征,并且调节106处的增材沉积处理以优先在识别的顶表面的凹谷或低洼区域中沉积材料结构(例如,导电材料、电阻材料、半导体材料等)。因此,在102处的一些制作工艺包括使顶表面平坦化,并且在102处的其它晶片制作工艺省略了顶侧平坦化处理,从而在顶表面上留下了高低形貌特征。在一些实施方式中,在106处的增材沉积优先在顶表面上的台阶之间的低洼区域中沉积材料。在一个实施方式中,通过在104和/或110处的光学晶片探测来识别低洼区域。

在103处的配置处理(例如,图1中的步骤104-110)之后,示例制造方法100在112处包括组装处理。组装处理包括以下步骤中的一个或多个:对经处理的晶片进行背磨;锯切或激光切割晶片以将晶片分割成分开的管芯,这些管芯包括由电子部件形成的相应电路;进行管芯附接处理以将每个管芯附接到相应的引线框架;进行引线键合以将键合线附接到管芯和引线框架特征件;清洁工艺,诸如等离子体清洁步骤(例如,Ar/O

图2示出在根据示例方法100的制造期间的示例微电子器件。在图2中示出经处理的晶片200的说明性部分,包括一个示例说明性管芯部分或管芯区域201。示例晶片200作为一体结构进行处理,包括示例增材沉积处理(例如,上文中的图1中的106),并且随后被分割成分开的管芯201。图2中的器件包括半导体衬底202(例如,硅晶片、SOI晶片等),并且在衬底202上或衬底202中形成多个电子部件。在所示的示例中,在衬底202的上表面上方形成多晶硅结构204。形成隔离结构206(例如,场氧化物结构、浅沟槽隔离(STI)结构等)以隔离衬底202的选定区域或选定区。使用合适的半导体处理技术和装置,用p或n型杂质或掺杂剂(未示出)选择性地注入衬底202和/或多晶硅结构204的一个或多个部分,以形成一个或多个电子部件。多晶硅结构204提供多晶硅电阻器208(例如,标记为R1)。其它类型和形式的电子部件可以形成在衬底202上或衬底202中,以及随后形成的金属化结构212、216中,诸如电阻器、电感器、电容器等。

金属化层212形成在衬底202、多晶硅结构204和隔离结构206的上表面上方。金属化层或层级212被称为预金属化介电(PMD)层,并且可以是任何合适的介电材料,诸如二氧化硅(SiO

ILD层216包括导电布线结构,以通过相关联的PMD层接触件214形成互连,以将晶片200的各个电子部件彼此互连,并为各个电子部件特征件提供外部连接性。导电布线结构220(例如,铜)具有通过最终ILD层218的顶表面或上表面219而暴露的上表面。所示示例包括在顶部ILD层218的选定部分上方形成的钝化层222(例如,氮化物材料)。钝化层222暴露出所示的导电布线结构220的顶部的一部分。在其它示例中,钝化层222覆盖上部导电布线结构220的全部或一部分。

在图2的示例中,金属化结构212、216包括电连接到电阻器208的相对端的第一导电布线结构和第二导电布线结构220。所示的第一上部导电布线结构和第二上部导电布线结构220形成横向电容器210(例如,图中标记为C1)的电容器板。上部ILD层218在导电布线结构220之间提供介电材料,以形成与多晶硅电阻器结构208并联的电容器210。在图1中的106处执行增材沉积工艺在顶部介电层218的表面219上方沉积介电材料224,以设定或调节电阻器208和电容器210的并联RC电路。在图2的示例中,电容器板220彼此横向间隔开间隙距离230。

在间隙230附近存在或不存在选择性沉积的介电材料224影响(例如,设定或调节)电容器210的电容C1。此外,所选材料224影响最终电容C1。此外,尺寸(沿着所示的X和/或Y方向,以及沿着进入图1中的页面的方向的维度)影响电容C1。在各种实施方式中,在106处选择性地调节增材沉积以控制尺寸、材料和/或添加的结构224的存在/不存在,以便设定或调节电容器210的电容C1。该沉积进而设定或调节由电容器部件210和电阻器部件208形成的并联RC电路。在该示例中,沉积系统沿图2中的方向228从左向右平移印刷头或喷嘴226,以便沉积材料224。

图2还示意性地示出所得的RC并联电路,该RC并联电路包括与电容器210(C1)并联的电阻器208(R1)。在该示例中,通过金属化导电布线结构220的互连,电阻器208和电容器210在电路节点232和234之间彼此并联连接。提供介电材料224的增材沉积的能力提供了如图2中示意性示出的电容器210的可调节性。

图3示出在根据示例方法100的制造期间的示例微电子器件200的另一种实施方式。在该示例中,图1中106处的增材沉积工艺在金属化结构上方沉积导电材料结构300,以设定或调节包括金属化结构212、216的横向电容器210的电路。如图3中所示,导电结构300相对于电路组件208和210是浮置的。在该示例中,导电结构300(例如,铜)的存在提供了关于电容器210的电容C1的互电容调节能力。在另一示例中,在106处的增材沉积工艺在电容器210的电容器板之间的间隙230附近创建导电结构300,并且所添加的导电结构300还连接到金属化结构的另一导电布线结构(未示出),以控制导电材料结构300的电压。例如,导电结构300可以接地,或者可以连接到电路内的电源电压节点,以便以可控制的方式影响电容C1。

图2和图3的示例有助于在形成电容器210的板的导电布线结构220附近(例如,在其上方)进行介电或导电材料的晶片级沉积,以改变电容C1的值,而钝化层222的中间部分防止通过材料结构300的增材沉积而使电容器板短路。可以以模拟方式使用该调节能力来调谐电容器和/或以数字方式来使用该调节能力以修整随后分割和封装的微电子器件上的功能。

图1中的制造和配置方法100、103有益于以各种方式修整或调节电路,诸如在不使用欧姆接触的情况下创建射频(RF)跳线。另一个有利的用途是在不使用欧姆接触的情况下路由RF信号。该技术还可以用于通过改变或设定滤波器电路的电容器部件的电容来逐个部分地调谐RF滤波器,而不管电容器是至少部分地被创建在下面的衬底202上或中,还是至少部分地被创建在金属化结构212、216中。所描述的方法也可以用于基于单个晶片设计来创建不同的产品,诸如通过逐个管芯地在106处调节增材沉积工艺。以该方式,在106处的沉积处理可以在单个晶片200内的不同管芯区域201上提供不同的滤波器频率、RF功率输出、单端与差分信号路径等。

图4示出经处理的晶片200的另一示例的局部俯视图,其中在图1的方法100中的106处在金属化结构上方(例如,在钝化层222的一部分上方)沉积了磁性材料400。在该示例中,沉积的磁性材料400包括长度402、宽度404和厚度(未示出,在图4的页面向外),其可以通过在106处的增材沉积处理来控制。在该示例中,磁性材料400的增材沉积设定或调节包括在金属化结构中形成的平面电感器401的电路。在该示例中的增材沉积将磁性材料400沉积在介电层218的表面219上方。在该示例中的电感器401是具有第一端和第二端的平面线圈,其可以使用不同金属化结构层级或层的导电布线结构(未示出)连接到晶片200中的其它电路。

图5示出经处理的晶片200的另一示例的局部俯视图。在该示例中,顶部金属化结构层218的两个大致平行的导电布线结构220(例如,上文中描述的图2)通过磁性材料400的增材沉积(例如,图1中的106)彼此磁耦合。该能力允许通过将磁性材料400选择性地放置在晶片200内的两个不同电路的导电特征件220附近来选择性地将第一电路和第二电路进行磁(例如,电感)耦合。在该示例中,在106处的增材沉积通过不存在/存在增材沉积的磁性材料400和/或通过调节材料400的成分、沉积的材料400的长度402、宽度404和/或厚度来促进设定或调节给定管芯区域的两个电路之间的耦合。

图6示出使用磁性材料400的选择性增材沉积的经处理的晶片200的不同实施方式的另一局部俯视平面图。在该示例中,经处理的晶片200包括由顶部金属化层218中的导电布线结构220形成的两个分开的平面线圈电感器结构401。在该示例中,在图1中的106处的增材沉积将磁性材料400沉积在金属化结构上方(例如,在钝化层222上方),以设定或调节在金属化结构中形成的第一平面电感器和第二平面电感器401之间的磁耦合。在一个实施方式中,磁性材料400的添加在第一线圈和第二线圈401之间提供了变压器耦合。可以扩展图6中的构思,以通过将磁性材料选择性地增材沉积在那些不同电感器的导电特征件之间或附近,而选择性地耦合或改变一组电感器中的不同电感器之间的耦合量。这有助于在任何期望电路应用中精细修整电感。

图4-图6的示例允许在106处的增材沉积在用于线圈401的导电布线结构220上方在选定管芯电路中实现磁跳线,以改变电感器的磁耦合或自感,选择性地创建变压器耦合,调谐包括电感器或变压器的电路的一个或多个参数,创建带有力/感测电路和/或其它应用的数字开关。

图7示出经处理的晶片200的不同实施方式的局部俯视平面图,其包括由电阻器208(标记为R)、电容器210(标记为C)和电感器401(标记为L)形成的RLC谐振储能(tank)电路。电路部件的各个部分由导电布线结构220形成,以形成第一电路节点702和第二电路节点704。在该示例中,经处理的晶片200包括电感器线圈401,该电感器线圈具有连接到第一节点702的第一端以及通过在下部金属化层或层级中布线的金属化结构(图7中的虚线所示)连接到第二节点704的第二端。

导电布线结构220还形成横向电容器210的大致平行的电容器板(例如,类似于上文描述的图2和图3)。导电布线结构220的所示下部(例如,节点702和704)通过金属化结构的导电特征件(未示出)连接至多晶硅电阻器208的第一端和第二端(例如,上文描述的图2和图3)。在该示例中,在图1中的106处的增材沉积处理用于在金属化结构上方选择性地沉积磁性、导电、介电和/或电阻材料,以设定或调节由在金属化结构和衬底202中形成的电子部件创建的并联RLC储能电路的谐振频率。如结合图4-图6在上面所述,沉积的磁性材料结构400用于设定或调节电感器组件401的电感L。此外,沉积的介电材料结构224(或沉积的导电结构)用于设定或调节电容器部件210的电容C(例如,上文描述的图2和图3)。

此外,增材沉积工艺在介电层218的表面219上方沉积电阻材料700,以设定或调节电阻器部件208的电阻。在该示例中,沉积的电阻结构700添加与多晶硅结构204的电阻R并联的电阻R2,以修改或设定谐振储能电路的电阻。此外,可以在106处的增材沉积处理中调节沉积的结构400、224和/或700的存在或不存在以及尺寸和材料,以实现电路的任何期望谐振频率或其它操作参数。

参考图8和图9,图8示出经处理的晶片200的另一实施方式,其中增材沉积处理用于实现用于天线电路的可编程电长度的可配置RF调谐短截线(stub)。在该示例中,顶部金属化层导电布线结构220形成与上述多晶硅电阻器208(标记为R1)串联连接的基础天线800。电阻器208的一端经由金属化结构互连连接到接地参考节点(例如,标记为GND)。在图8的示例中,导电材料结构300沉积在金属化结构上方(例如,靠近天线800,并通过中间钝化层222与天线800电分离)。增材沉积的导电结构300的尺寸有助于设定或调节在金属化结构中形成的天线电路。图9示出经处理的晶片200的另一示例RF调谐短截线实施方式,其中半导体材料900被增材沉积在金属化结构212、216上方以设定或调节在金属化结构中形成的天线电路。

图10示出经处理的晶片200的另一实施方式,以示出用于设定或调节热电路的增材沉积。在该示例中,经处理的晶片200包括沉积在金属化结构的热回路部件(例如,示出为导电布线结构220)上方的导热材料1000。沉积的材料1000的存在或不存在、尺寸、接近度和热导率参数(例如,热K)修改了进出热回路的热传递,以设定或调节在金属化结构中形成的热回路。所描述的增材沉积方法和技术有益于修改热电电路的热导率,调谐热时间常数,调谐声子转移和晶片200的电路的效率,或用于其它目的。

图11示出沿图6的线11-11截取的经处理的晶片200的另一实施方式,以说明增材沉积用于将在金属化结构212、216中的不同层级处形成的两个平面电感器磁耦合。在该示例中,经处理的晶片200包括在金属化结构212和216中的不同层级处形成的第一平面电感器和第二平面电感器,并且磁性材料400在金属化结构上方(例如,在钝化层222上方)的增材沉积将电感器磁耦合。

图12示出沿图5的线12-12截取的另一示例经处理的晶片200的另一实施方式,以说明增材沉积用于将在金属化结构212、216中形成的两个导电特征件磁耦合。在该示例中,处理晶片200的顶表面包括具有纹理化表面的形貌特征,其包括高区域和低洼区域。此外,在该示例中,钝化层222是大体保形的薄层,其中上部金属化导电结构220在钝化层222的部分上竖直延伸。光学晶片探针(例如,在图1的方法100中为104和/或110)识别顶部金属化层218的导电结构220之间的低洼区域(例如,凹谷)。在该情况下,在106处的增材沉积处理形成磁性材料400和在导电结构220之间横向的低洼区域。该示例在以下方面提供优势:磁性材料400的选择性增材沉积用以选择性地将经处理的晶片200的电路磁耦合和/或修改电路的电感或其它性能属性。此外,在106处的沉积处理之后,在增材沉积的磁性材料400的至少一部分上方形成另一钝化层材料1202。在该构思的另一示例中,介电材料可以沉积在导电布线结构之间横向的凹谷或低洼区域中,以与中间钝化层材料一起形成电容器或提供电容耦合。该方法可以与光学扫描结合(例如,在104和/或110处)以识别手指结构之间的低洼区域的位置,并且可以进一步与电晶片探针测量结合以调节增材沉积的材料的厚度和/或位置,以精确地调节或设定电气部件值、磁耦合或电容耦合的量或经处理的晶片200的电路的其它特征或性能属性。

图13示出另一示例经处理的晶片,该晶片具有通过在金属化结构212、216上进行增材沉积而形成的三维磁性材料400,以设定或调节在金属化结构中形成的第一导电结构和第二导电结构220之间的磁耦合。在所示示例中,磁性材料结构400包括间隙或腔1300。在一个可能的实施方式中,在三维磁性材料400上方形成金属化结构(未示出)以提供导电屏蔽。

在权利要求的范围内,在所描述的实施例中可以进行修改,并且其它实施例也是可以的。

- 编程电抗部件

- 电抗器、电抗器制造方法、以及电抗器部件