阵列基板以及显示面板

文献发布时间:2023-06-19 11:49:09

技术领域

本申请涉及显示技术领域,具体涉及一种阵列基板以及显示面板。

背景技术

光学指纹识别技术是利用光的折射和反射原理,当光照射到手指上,被手指反射到感光器件上,由于指纹谷和脊对光的反射不同,感光器件所接受到谷和脊的反射光强不同,然后再将光信号转换为电学信号。

但是在对现有技术的研究和实践过程中,本申请的发明人发现,感光器件一般由下电极、感光层以及上电极组成。其中下电极除作为电子传输层以外,还对穿透感光层到达下电极的光线反射回感光层以增加感光层对指纹反射光线的吸收效率,提高感光器件的灵敏度。但由于下电极表面相对粗糙,易发生漫反射,造成光线的损失,进而不利于感光器件的感测效率。

发明内容

本申请实施例提供一种阵列基板以及显示面板,可以提高感光器件的感测效率。

本申请实施例提供一种阵列基板,其包括:

基板;

薄膜晶体管结构层,所述薄膜晶体管结构层设置在所述基板上,所述薄膜晶体管结构层包括第一薄膜晶体管;

平坦层,所述平坦层设置在所述薄膜晶体管结构层上;以及

感光器件,所述感光器件设置在所述平坦层上,所述感光器件电连接于所述第一薄膜晶体管;所述感光器件包括第一电极、感光层和第二电极;

所述第一电极设置在所述平坦层上,所述第一电极包括相连的平展部和凹陷部,所述凹陷部自所述平展部向所述平坦层的厚度方向凹设形成;所述感光层填充并覆盖所述凹陷部,所述第二电极设置在所述感光层上。

可选的,在本申请的一些实施例中,所述平坦层上设置有凹槽,所述凹陷部形成在所述凹槽上;

所述凹槽的槽壁面与所述凹槽底面所在的平面具有坡度角,所述坡度角为锐角。

可选的,在本申请的一些实施例中,所述坡度角介于60度至80度之间。

可选的,所述凹槽的深度小于所述平坦层的厚度,所述凹陷部与所述薄膜晶体管结构层的源/漏极分隔设置。

可选的,在所述第一电极中,自所述第一电极的中间区域向所述第一电极的四周区域,所述凹陷部的凹陷深度递减。

可选的,在本申请的一些实施例中,所述感光器件与所述第一薄膜晶体管至少部分重叠。

可选的,在本申请的一些实施例中,所述阵列基板还包括第一绝缘层、第二绝缘层、公共电极、第三绝缘层和像素电极;

所述第一绝缘层设置在所述第一电极上,所述第一绝缘层上设置有裸露所述平展部和凹陷部的开口,所述感光层设置在所述开口内并连接于所述第一电极;所述第二绝缘层设置在所述感光层上;所述公共电极设置在所述第二绝缘层上;所述第三绝缘层设置在所述公共电极上;所述像素电极和所述第二电极均设置在所述第三绝缘层上,所述像素电极和所述第二电极同层设置。

可选的,在本申请的一些实施例中,所述阵列基板还包括电极绝缘层和像素电极;所述感光层包括N型半导体层、本征半导体层和P型半导体层;

所述N型半导体层形成在所述第一电极上,所述本征半导体层包裹所述N型半导体层和所述第一电极,所述P型半导体层设置在所述本征半导体层上,所述第二电极设置在所述P型半导体层上;所述电极绝缘层设置在所述第二电极上;所述像素电极设置在所述电极绝缘层上。

可选的,在本申请的一些实施例中,所述薄膜晶体管结构层包括依次设置在所述基板上的缓冲层、有源层、栅极绝缘层、第一金属层、层间介质层和第二金属层;

所述第一金属层包括第一栅极,所述有源层包括第一有源部分,所述第二金属层包括第一源极和第一漏极;

所述第一栅极、所述第一有源部分、所述第一源极和所述第一漏极形成所述第一薄膜晶体管;所述第一源极或所述第一漏极电连接于所述第一电极。

可选的,在本申请的一些实施例中,所述薄膜晶体管结构层还包括设置在所述基板和所述缓冲层之间的遮光层,所述遮光层与所述第一有源部分重叠设置,且与所述感光器件也重叠设置。

可选的,在本申请的一些实施例中,所述第一金属层还包括第二栅极,所述有源层包括第二有源部分,所述第二金属层包括第二源极、第二漏极;所述第二栅极、所述第二有源部分、所述第二源极和所述第二漏极形成第二薄膜晶体管;

所述第二源极或所述第二漏极电连接于所述像素电极。

相应的,本申请实施例还提供一种显示面板,其包括彩膜基板、液晶和如上述实施例所述的阵列基板。

本申请实施例在平坦层上形成具有凹陷部的第一电极,使得光线穿过感光层到达凹陷部上时,会在凹陷部上形成多次反射,而在反射的过程中,光线均会穿过感光层,因此增加了感光层吸收光线的效率。

附图说明

为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

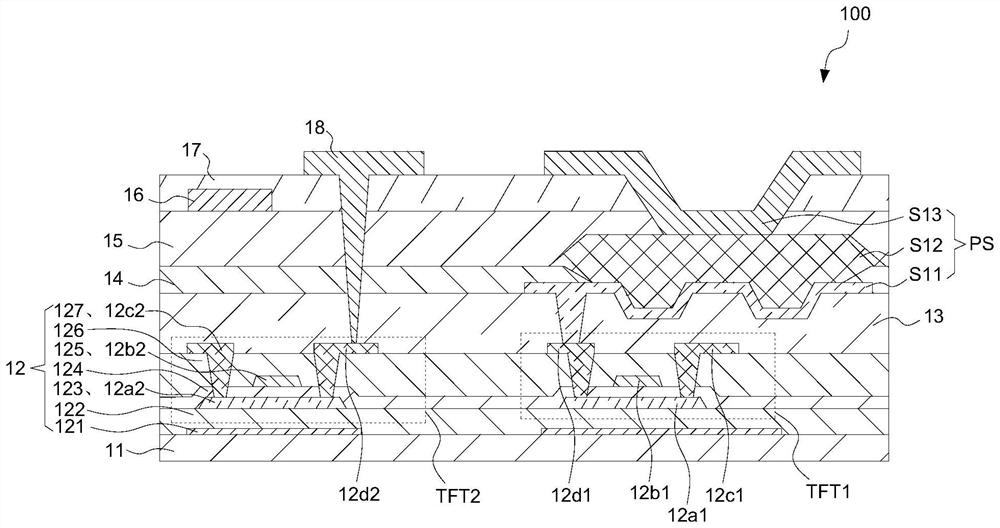

图1是本申请第一实施例提供的阵列基板的结构示意图;

图2为本申请第一实施例提供的阵列基板中平坦层、第一电极、第一绝缘层和感光层的结构示意图。

图3是本申请第一实施例提供的阵列基板的制备方法的步骤B1的示意图;

图4是本申请第一实施例提供的阵列基板的制备方法的步骤B2的示意图;

图5是本申请第一实施例提供的阵列基板的制备方法的步骤B3的示意图;

图6是本申请第二实施例提供的阵列基板的结构示意图;

图7是本申请实施例提供的显示面板的结构示意图。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。此外,应当理解的是,此处所描述的具体实施方式仅用于说明和解释本申请,并不用于限制本申请。在本申请中,在未作相反说明的情况下,使用的方位词如“上”和“下”通常是指装置实际使用或工作状态下的上和下,具体为附图中的图面方向;而“内”和“外”则是针对装置的轮廓而言的。

本申请实施例提供一种阵列基板以及显示面板,下文进行详细说明。需说明的是,以下实施例的描述顺序不作为对实施例优选顺序的限定。

图1是本申请第一实施例提供的阵列基板的结构示意图。本申请第一实施例提供一种阵列基板100,其包括基板11、薄膜晶体管结构层12、平坦层13和感光器件PS。

薄膜晶体管结构层12设置在基板11上。薄膜晶体管结构层12包括第一薄膜晶体管TFT1和第二薄膜晶体管TFT2。平坦层13设置在薄膜晶体管结构层12上。感光器件PS设置在平坦层13上。感光器件PS电连接于第一薄膜晶体管TFT1。感光器件PS包括第一电极S11、感光层S12和第二电极S13。

请参照图2,第一电极S11设置在平坦层13上。第一电极S11包括相连的平展部S111和凹陷部S112。凹陷部S112自平展部S111向平坦层13的厚度方向凹设形成。感光层S12填充并覆盖凹陷部S112。第二电极S13设置在感光层S12上。

本申请第一实施例的阵列基板100在平坦层13上形成具有凹陷部S112的第一电极S11,使得光线穿过感光层S12到达凹陷部S112上时,会在凹陷部S112上形成多次反射,而在反射的过程中,光线均会穿过感光层S12,因此增加了感光层S12吸收光线的效率,进而提高了感光器件PS的感测效率。

在本第一实施例的阵列基板100中,基板11可为玻璃基板或者柔性衬底。基板11的材质包括玻璃、二氧化硅、聚乙烯、聚丙烯、聚苯乙烯、聚乳酸、聚对苯二甲酸乙二醇酯、聚酰亚胺或聚氨酯中的一种。

第一薄膜晶体管TFT1可以是顶栅型薄膜晶体管或底栅型薄膜晶体管;第二薄膜晶体管TFT2可以是顶栅型薄膜晶体管或底栅型薄膜晶体管。第一薄膜晶体管TFT1可以是P型薄膜晶体管或N型薄膜晶体管;第二薄膜晶体管TFT2可以是P型薄膜晶体管或N型薄膜晶体管。在本第一实施例中,以第一薄膜晶体管TFT1和第二薄膜晶体管TFT2均为N型的顶栅薄膜晶体管为例进行阐述,但不限于此。

在本第一实施例的阵列基板100中,平坦层13上设置有凹槽131。凹陷部S112形成在凹槽131上。

请参照图2,凹槽131的槽壁面与凹槽131底面所在的平面具有坡度角α,坡度角α为锐角,以提高凹槽131槽壁面的面积,由于第一电极S11的凹陷部S112形成在凹槽131上,因此增加凹陷部S112接收光线的范围,提高光线的反射效率,进而提高了感光层S12吸收光线的效率。

可选的,坡度角α可以是5度、10度、15度、30度、45度、60度、75度、80度和85度。

可以理解的是,坡度角α越小,光线在凹陷部S112上的反射次数将会越少,而在第一电极S11上成膜出现断裂的风险越低;坡度角α越大,光线在凹陷部S112上的反射次数将会越多,而在第一电极S11上成膜出现断裂的风险越高。

在本第一实施例的阵列基板100中,坡度角α介于60度至80度之间,比如可以是60度、65度、70度、75度和80度。

将坡度角α介于60度至80度之间,是为了避免感光层S12在第一电极S11上形成出现断裂,以及确保光线在凹陷部S112上具有足够多的反射次数。

请参照图2,凹槽131的深度D小于平坦层13的厚度L。凹陷部S112与薄膜晶体管结构层12的源/漏极分隔设置。这样的设置,以避免凹槽131的深度过深,降低感光层S12出现断层的风险。

可选的,在第一电极S11中,自第一电极S11的中间区域ZJ向所述第一电极S11的四周区域SZ,凹陷部S112的凹陷深度递减。在每个感光器件中,位于第一电极S11的中间区域ZJ接受的光线多,因此上述的设置提高了光线利用率。

在本第一实施例的阵列基板100中,凹槽131和凹陷部S112一一对应设置,即一个凹陷部S112覆盖一个凹槽131。可选的,凹槽131的数量是多个,凹陷部S112的数量也是多个,多个凹陷部S112的设置便于提高光线的利用率。

可选的,平坦层13的材料可包括氮化硅、氧化硅以及有机光阻中的至少一种。

另外,感光器件PS与第一薄膜晶体管TFT1至少部分重叠,以提高开口率。

在本第一实施例的阵列基板100中,阵列基板100还包括第一绝缘层14、第二绝缘层15、公共电极16、第三绝缘层17和像素电极18。

第一绝缘层14设置在第一电极S11上。第一绝缘层14上设置有裸露部分的平展部S111和凹陷部S112的开口141。其中,开口141孔壁的倾斜角β小于坡度角α,且第一绝缘层14覆盖第一电极S11周侧的平展部S111的部分,以使开口141孔壁、平展部S111面向感光层S12的一面和凹陷部S112的侧壁形成三段式斜面,提高感光层S12在制程中的连续性,避免感光层S12出现断裂的风险。

感光层S12设置在开口141内并连接于第一电极S11。第二绝缘层15设置在感光层S12上。公共电极16设置在第二绝缘层15上。第三绝缘层17设置在公共电极16上。像素电极18和第二电极S13均设置在第三绝缘层17上。像素电极18和第二电极S13同层设置。

可选的,第一电极S11可是单层结构或多层结构,比如可为Ti(钛)层/Al(铝)层/Ti(钛)层、Mo(钼)层、Mo(钼)层/Cu(铜)层、Mo(钼)层/Al(铝)层/Mo(钼)层中一种。

可选的,第二电极S13、公共电极16和像素电极18的材料包括但不限于氧化铟锡。

第一绝缘层14、第二绝缘层15和第三绝缘层17的材料可包括氮化硅、氧化硅以及有机光阻中的至少一种。

在本第一实施例的阵列基板100中,薄膜晶体管结构层12包括依次设置在基板11上的遮光层121、缓冲层122、有源层123、栅极绝缘层124、第一金属层125、层间介质层126、第二金属层127和平坦层128。

有源层123包括第一有源部分12a1和第二有源部分12a2。有源层123的材料可以是多晶硅或金属氧化物。第一金属层125包括第一栅极12b1和第二栅极12b2。第二金属层127包括第一源极12c1、第一漏极12d1、第二源极12c2和第二漏极12d2。

第一有源部分12a1、第一栅极12b1、第一源极12c1和第一漏极12d1形成第一薄膜晶体管TFT1。第二有源部分12a2、第二栅极12b2、第二源极12c2和第二漏极12d2形成第二薄膜晶体管TFT2。

第一源极12c1或第一漏极12d1电连接于第一电极S11的平展部S111。第二源极12c2或第二漏极12d2电连接于像素电极18。

在本第一实施例的阵列基板100中,第一漏极12d1电连接于第一电极S11。第二漏极12d2电连接于像素电极18。

遮光层121的部分与第一有源部分12a1重叠设置,且与感光器件PS也重叠设置;遮光层121的另一部分与第二有源部分12a2重叠设置;以避免光线照射到第一有源部分12a1、第二有源部分12a2和感光器件PS。

可选的,遮光层121的材料可为金属材料。缓冲层122的材料包括但不限于氮化硅或氧化硅。栅极绝缘层124的材料可包括氮化硅、氧化硅以及有机光阻中的至少一种。第一金属层125的材料可包括铜、铝以及钛中的至少一种。层间介质层126的材料可包括氮化硅、氧化硅以及有机光阻中的至少一种。平坦层128的材料可包括氮化硅、氧化硅以及有机光阻中的至少一种。

相应的,本第一实施例的阵列基板100的制备方法包括以下步骤:

步骤B1:在基板11上形成薄膜晶体管结构层12;

步骤B2:在薄膜晶体管结构层12上形成平坦层13;

步骤B3:在平坦层13上形成感光器件PS。

下文对本第一实施例的阵列基板100的制备方法进行阐述。

请参照图3,步骤B1,在基板11上形成薄膜晶体管结构层12。具体的,步骤B1包括以下步骤:

步骤B11:在基板11上形成一遮光材料层,并采用曝光蚀刻等方式图案化该遮光材料层形成遮光层121。随后转入步骤12。

步骤B12:在遮光层121上依次形成缓冲层122和多晶硅层SI,并采用曝光蚀刻等方式图案化多晶硅层SI,随后对多晶硅层SI进行磷离子掺杂,形成N+掺杂区。随后转入步骤B13。

步骤B13:在多晶硅层SI和缓冲层122上形成栅极绝缘层124和第一金属材料层,并采用光刻工艺图案化第一金属材料层形成第一金属层125;随后以第一栅极12b1和第二栅极12b2遮挡多晶硅层SI的部分,对多晶硅层SI进行N-离子植入形成N-掺杂区,继而形成有源层123。随后转入步骤B14。

步骤B14:在第一金属层125上形成层间介质层126。随后转入步骤B15。

步骤B15:在所述层间介质层126上形成第二金属材料层,并采用光刻工艺图案化第二金属材料层形成第二金属层127。随后转入步骤B2。

请参照图4,步骤B2,在薄膜晶体管结构层12上形成平坦层13。具体的,先在第二金属层127上形成一有机光阻层,随后采用半色调掩模板在该有机光阻层上形成平坦层13以及凹槽131。随后转入步骤B3。

请参照图5,步骤B3,在平坦层13上形成感光器件PS。具体的,步骤B3包括以下步骤:

步骤B31:在平坦层13上形成一层第三金属材料层,随后图案化第三金属材料层,形成对应于凹槽131区域的第一电极S11;随后在第一电极S11上形成第一绝缘层14。随后转入步骤B32。

步骤B32:在第一绝缘层14上依次形成N型半导体材料层、本征半导体材料层和P型半导体层,并采用同一光罩图案化N型半导体材料层、本征半导体材料层和P型半导体层形成感光层S12,感光层S12设置第一电极S11和第一绝缘层14上。

可选的,N型半导体层的材料为N型非晶硅;本征半导体层的材料为非晶硅;P型半导体层的材料为P型非晶硅。随后转入步骤B33。

步骤B33:在感光层S12上依次形成第二绝缘层15、公共电极16和第三绝缘层17。第三绝缘层17上设置有第一过孔171和第二过孔172,第一过孔171裸露第二漏极12d2,第二过孔172裸露感光层S12。随后转入步骤B34。

步骤B34:在第三绝缘层17上形成一导电层,并采用光刻工艺图案化该导电层形成像素电极18和第二电极S13。像素电极18连接于第二漏极12d2。第二电极S13连接于感光层S12。

这样便完成了本第一实施例的阵列基板100的制备过程。

请参照图6,图6是本申请第二实施例提供的阵列基板的结构示意图。本第二实施例的阵列基板200与第一实施例的阵列基板100的不同之处在于:本第二实施例的阵列基板200采用同一光罩同时形成第一电极S21和N型半导体层S221,并且采用本征半导体层S222包裹N型半导体层S221,进而节省了第一实施例的阵列基板100中的第一绝缘层14和第二绝缘层15。

具体的,本第二实施例的阵列基板200的基板21、薄膜晶体管结构层22、平坦层23和第一电极S21对应的与第一实施例的阵列基板100的基板11、薄膜晶体管结构层12、平坦层13和第一电极S11的结构相同。

本第二实施例的阵列基板200还包括电极绝缘层24和像素电极25。感光层S22包括N型半导体层S221、本征半导体层S222和P型半导体层S223。

N型半导体层S221形成在第一电极S21上。本征半导体层S222包裹N型半导体层S221和第一电极S21。P型半导体层S223设置在本征半导体层S222上。第二电极S23设置在P型半导体层S223上。电极绝缘层24设置在第二电极上S23。像素电极25设置在电极绝缘层24上。

可选的,P型半导体层S223和本征半导体层S222采用同一光罩形成。第二电极S23连接P型半导体层S223和本征半导体层S222,以节省两层绝缘层,简化了阵列基板200的制备工艺。另外,第二实施例的阵列基板200采用本征半导体层S222包裹N型半导体层S221,以提高了感光器件PS的灵敏度。

在一些实施例中,本征半导体层S222采用一光罩形成,P型半导体层S223采用另一光罩形成。本征半导体层S222包裹N型半导体层S221,P型半导体层S223包裹本征半导体层S222。第二电极S23连接P型半导体层S223。

可选的,第二电极S23至少覆盖P型半导体层S223面积的63%以上,以保证感光器件PS的光电性能,比如可以是63%、64%、75%、85%或100%。

在本第二实施例的阵列基板200中,阵列基板200还包括公共电极(图中未示出),公共电极与第二电极S23同层设置。

相应的,请参照图7,图7是本申请实施例提供的显示面板的结构示意图。本申请实施例还提供一种显示面板1000,其包括彩膜基板CF、液晶LC和阵列基板AY。其中阵列基板AY为上述第一实施例的阵列基板100、第二实施例的阵列基板200或上述其它实施例的阵列基板。

本申请实施例在平坦层上形成具有凹陷部的第一电极,使得光线穿过感光层到达凹陷部上时,会在凹陷部上形成多次反射,而在反射的过程中,光线均会穿过感光层,因此增加了感光层吸收光线的效率。

以上对本申请实施例所提供的一种阵列基板以及显示面板进行了详细介绍,本文中应用了具体个例对本申请的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本申请的方法及其核心思想;同时,对于本领域的技术人员,依据本申请的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本申请的限制。

- 阵列基板、显示面板以及阵列基板和显示面板的制造方法

- 阵列基板、具有该阵列基板的显示面板和阵列基板的制造方法