一种频率数据恢复电路与其频率维持方法

文献发布时间:2023-06-19 11:03:41

技术领域

本发明涉及一种频率数据恢复电路与其频率维持方法。

背景技术

数字数据在高速传输时可能容易出现噪声。因此,收发器通常需要频率数据恢复电路(Clock and Data Recovery Circuit,CDR),来重新产生低抖动频率以及恢复出低噪声数据。所以,频率数据恢复电路对于数据和频率的传输与接收扮演重要角色。

一般而言,频率最好能满足:1.频率频率必须和数据速率相同。2.频率和数据间必须要有正确的相位关系。3.频率本身必须要有小的抖动。

频率数据恢复电路在进行频率产生与数据恢复时,需要让所产生的频率能锁定于数字输入数据。但如果突然有一段时间,频率数据恢复电路接收不到数字输入数据,则所产生的频率的频率容易乱漂。等到频率数据恢复电路重新接收到数字输入数据,需要花较长的时间才能让频率数据恢复电路所产生的频率重新锁定至数字输入数据。

发明内容

根据本案一实例,提出一种频率数据恢复电路,包括:一相位侦测器;一第一电荷泵,耦接至该相位侦测器;一循环滤波器,耦接至该第一电荷泵;一压控振荡器,耦接至该循环滤波器;一计数器与脉冲产生器,耦接至该压控振荡器;一电压产生器,耦接至该计数器与脉冲产生器;一临界侦测器,耦接至该电压产生器;一逻辑门单元,耦接至该计数器与脉冲产生器以及该临界侦测器;以及一第二电荷泵,耦接至该逻辑门单元与该循环滤波器。当该频率数据恢复电路持续接收一数字输入数据时,该相位侦测器、该第一电荷泵、该循环滤波器与该压控振荡器使得该压控振荡器的一输出信号锁定于该数字输入数据。当该数字输入数据暂时消失时,于该计数器与脉冲产生器的一计数时间内,该电压产生器的一输出电压上升,该临界侦测器将该电压产生器的该输出电压分别比较于复数个临界值,以产生复数个比较结果,该逻辑门单元根据该些比较结果而产生一控制信号至该第二电荷泵,以由该第二电荷泵控制该压控振荡器加速或减速。

根据本案另一实例,提出一种频率数据恢复电路的频率维持方法,该频率数据恢复电路包括一压控振荡器。该频率维持方法包括:当一数字输入数据暂时消失时,于一计数时间内,让一输出电压上升;将该输出电压分别比较于复数个临界值,以产生多个比较结果;以及根据该些比较结果而产生一控制信号,以控制该压控振荡器加速或减速。

为了对本发明的上述及其他方面有更佳的了解,下文特举实施例,并配合所附图式详细说明如下。

附图说明

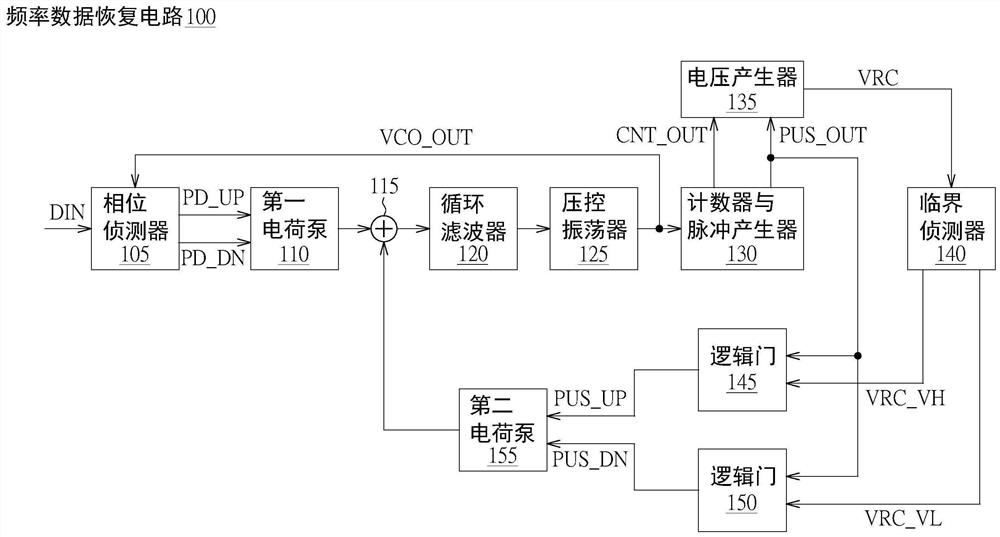

图1显示根据本案实施例的频率数据恢复电路的功能方块图。

图2显示根据本案一实施例的电压产生器的电路示意图。

图3显示根据本案一实施例的临界侦测器的电路示意图。

图4A与图4B显示根据本案实施例的信号波形图。

图5显示根据本案一实施例的频率数据恢复电路的频率维持方法的流程图。

附图标记

100:频率数据恢复电路

105:相位侦测器 110:第一电荷泵

115:加法器 120:循环滤波器

125:压控振荡器 130:计数器与脉冲产生器

135:电压产生器 140:临界侦测器

145、150:逻辑门 155:第二电荷泵

IREF:参考电源 SW1与SW2:开关

C:电容

310:数字模拟转换器 315:加法器

320:减法器 325与330:比较器

T1-T4:时期

510-530:步骤

具体实施方式

本说明书的技术用语是参照本技术领域的习惯用语,如本说明书对部分用语有加以说明或定义,该部分用语的解释是以本说明书的说明或定义为准。本揭露的各个实施例分别具有一或多个技术特征。在可能实施的前提下,本技术领域具有通常知识者可选择性地实施任一实施例中部分或全部的技术特征,或者选择性地将这些实施例中部分或全部的技术特征加以组合。

图1显示根据本案实施例的频率数据恢复电路的功能方块图。如图1所示,根据本案实施例的频率数据恢复电路100包括:相位侦测器(PhaseDetector)105、第一电荷泵(Charge Pump)110、加法器115、循环滤波器(loopfilter)120、压控振荡器(Voltage-controlled oscillator,VCO)125、计数器与脉冲产生器(Counter and Pulse Generator)130、电压产生器135、临界侦测器(ThresholdDetector)140、第一逻辑门145、第二逻辑门150与第二电荷泵155。第一逻辑门145与第二逻辑门150亦可合称为逻辑门单元。

相位侦测器105用以比较数字输入数据DIN与压控振荡器125的输出信号VCO_OUT的相位,并根据数字输入数据DIN与压控振荡器125的输出信号VCO_OUT的相位之间的相位差而输出信号PD_UP或PD_DN至第一电荷泵110。简言之,压控振荡器125的输出信号VCO_OUT的相位落后于数字输入数据DIN时,相位侦测器105输出信号PD_UP至第一电荷泵110。压控振荡器125的输出信号VCO_OUT的相位领先于数字输入数据DIN时,相位侦测器105输出信号PD_DN至第一电荷泵110。

第一电荷泵110耦接至相位侦测器105。第一电荷泵110内部有充电电源与放电电源。当第一电荷泵110接收到相位侦测器105所传来的信号PD_UP时,第一电荷泵110会致能其内部的充电电源(或者说提供充电路径),以输出充电电流给循环滤波器120(透过加法器115)。同样地,当第一电荷泵110接收到相位侦测器105所传来的信号PD_DN时,第一电荷泵110会致能其内部的放电电源(或者说提供放电路径),以使得循环滤波器120来放电。

加法器115将由第一电荷泵110与第二电荷泵155所传来的信号相加后,提供给循环滤波器120。在本案其他可能实施例中,加法器115是可省略组件,本案亦可设计成第一电荷泵110的讯号与第二电荷泵155的讯号分别且同时输入循环滤波器120。

循环滤波器120耦接至加法器115、第一电荷泵110与第二电荷泵155。在本案其他可能实施例中,加法器115是可省略组件,循环滤波器120亦可不透过加法器115而耦接第一电荷泵110与第二电荷泵155。一般而言,循环滤波器120可以是RC电路。如果循环滤波器120接收到由第一电荷泵110与/或第二电荷泵155所提供的充电电流/充电路径,则循环滤波器120的内部电容(未示出)被充电,使得循环滤波器120的内部电容的DC电压往上抬。如果第一电荷泵110与/或第二电荷泵155提供放电路径给循环滤波器120,则循环滤波器120的内部电容被放电,使得循环滤波器120的内部电容的DC电压往下降。

压控振荡器125耦接至循环滤波器120,以接收循环滤波器120的内部电容所提供的DC电压。当循环滤波器120的内部电容所提供给压控振荡器125的DC电压往上升时,压控振荡器125的输出信号VCO_OUT的频率增加。反之,当循环滤波器120的内部电容所提供给压控振荡器125的DC电压往下降时,压控振荡器125的输出信号VCO_OUT的频率下降。

计数器与脉冲产生器130耦接至压控振荡器125,以接收压控振荡器125的输出信号VCO_OUT。计数器与脉冲产生器130提供计数时间CNT_OUT。计数时间CNT_OUT的宽度例如但不受限于,为压控振荡器125的输出信号VCO_OUT的100个周期,当然,本案并不受限于此。当计数时间CNT_OUT转态为失能(例如,逻辑低)时,计数器与脉冲产生器130更产生输出脉冲PUS_OUT,其中,输出脉冲PUS_OUT的宽度是可控制的。

电压产生器135耦接至计数器与脉冲产生器130。电压产生器135可根据计数时间CNT_OUT而产生电压VRC(亦可称为输出电压VRC)。电压VRC相关于计数时间CNT_OUT,例如,电压VRC正比于计数时间CNT_OUT。亦即,计数时间CNT_OUT愈久,则电压VRC愈高。反之亦然。电压产生器135的电路细节将于底下说明。

临界侦测器140耦接至电压产生器135。临界侦测器140用以将电压产生器135所产生的电压VRC分别比较于第一临界值VH与第二临界值VL,以产生2个比较结果VRC_VH与VRC_VL。当电压VRC高于第一临界值VH时,比较结果VRC_VH为逻辑高。当电压VRC低于第二临界值VL时,比较结果VRC_VL为逻辑高。临界侦测器140的电路细节将于底下说明。

第一逻辑门145耦接至计数器与脉冲产生器130与临界侦测器140。第一逻辑门145例如但不受限于,为AND逻辑门。当输出脉冲PUS_OUT与比较结果VRC_VH皆为逻辑高时,第一逻辑门145输出逻辑高的信号PUS_UP。如果输出脉冲PUS_OUT与比较结果VRC_VH的任一者或两者为逻辑低时,第一逻辑门145输出逻辑低的信号PUS_UP。

第二逻辑门150耦接至计数器与脉冲产生器130与临界侦测器140。第二逻辑门150例如但不受限于,为AND逻辑门。当输出脉冲PUS_OUT与比较结果VRC_VL皆为逻辑高时,第二逻辑门150输出逻辑高的信号PUS_DN。如果输出脉冲PUS_OUT与比较结果VRC_VL的任一者或两者为逻辑低时,第二逻辑门150输出逻辑低的信号PUS_DN。

第二电荷泵155耦接至第一逻辑门145与第二逻辑门150,以及加法器115。当信号PUS_UP为逻辑高时,第二电荷泵155提供充电路径给循环滤波器120。当信号PUS_DN为逻辑低时,第二电荷泵155提供放电路径给循环滤波器120。

在本案实施例中,输出脉冲PUS_OUT的宽度是可控制的。所以,输出脉冲PUS_OUT的宽度如果宽一些,则信号PUS_UP跟PUS_DN的宽度也会宽一些,就会使得第二电荷泵155多送一些电流给循环滤波器120(或者提供更长的放电时间给循环滤波器120),以让压控振荡器125的输出信号VCO_OUT的频率在这一次的调整幅度比较大。

图2显示根据本案一实施例的电压产生器135的电路示意图。如图2所示,电压产生器135包括:参考电源IREF、开关SW1与SW2,以及电容C。开关SW1耦接于参考电源IREF以及电容C之间。开关SW2耦接于电容C。

开关SW1受控于计数时间CNT_OUT,而开关SW2受控于控制信号CSW2,其中,控制信号CSW2有关于输出脉冲PUS_OUT与计数时间CNT_OUT。例如但不受限于,

当计数时间CNT_OUT为逻辑高时,开关SW1为导通,使得参考电源IREF对电容C充电。也就是说,如果计数时间CNT_OUT的宽度愈宽,电容C的跨压VRC愈高(因为充电时间愈久)。反之亦然。

此外,如上述,当计数时间CNT_OUT由逻辑高转态为逻辑低时,输出脉冲PUS_OUT会被致能。当输出脉冲PUS_OUT结束时,开关SW2为导通,以重设电压VRC。

图3显示根据本案一实施例的临界侦测器140的电路示意图。如图3所示,临界侦测器140包括:数字模拟转换器(DAC)310、加法器315、减法器320、比较器325与330。数字模拟转换器310耦接于加法器315与减法器320。加法器315与减法器320耦接于比较器325与330。

数字模拟转换器310将数字控制信号CTRL转换为模拟电压ΔV。加法器315将电压VRC_LOCK(亦可称为锁定输出电压)与模拟电压ΔV相加,以产生第一临界值VH(VH=VRC_LOCK+ΔV)。减法器320将电压VRC_LOCK与模拟电压ΔV相减,以产生第二临界值VL(VL=VRC_LOCK-ΔV)。当压控振荡器125处于锁定状态时,电压产生器135所产生的电压VRC定义为电压VRC_LOCK。

比较器325将电压VRC比较于第一临界值VH,以产生比较结果VRC_VH。当电压VRC高于第一临界值VH时,比较器325的比较结果VRC_VH为逻辑高。当电压VRC低于第一临界值VH时,比较器325的比较结果VRC_VH为逻辑低。

比较器330将电压VRC比较于第二临界值VL,以产生比较结果VRC_VL。当电压VRC低于第二临界值VL时,比较器330的比较结果VRC_VL为逻辑高。当电压VRC高于第二临界值VL时,比较器330的比较结果VRC_VL为逻辑低。

当数字输入数据DIN持续输入至频率数据恢复电路100时,频率数据恢复电路100主要由相位侦测器105、第一电荷泵110、加法器115、循环滤波器120、压控振荡器125来运作,以让压控振荡器125的输出信号VCO_OUT能锁定于数字输入数据DIN(也就是说,当压控振荡器125处于锁定状态时,电压产生器135所产生的电压VRC可以稳定地锁定于电压VRC_LOCK,并据以产生第一临界值VH与第二临界值VL)。如何在数字输入数据DIN持续输入至频率数据恢复电路100时,让压控振荡器125的输出信号VCO_OUT能锁定于数字输入数据DIN的细节于此将不重述。当然,当数字输入数据DIN持续输入至频率数据恢复电路100时,计数器与脉冲产生器130、电压产生器135、临界侦测器140、第一逻辑门145、第二逻辑门150与第二电荷泵155也可以有动作。

然而,当数字输入数据DIN暂时消失,使得频率数据恢复电路100有一段时间无法接收到数字输入数据DIN时,相位侦测器105与第一电荷泵110是无法动作。故而,当数字输入数据DIN暂时消失时,光靠相位侦测器105、第一电荷泵110、加法器115、循环滤波器120与压控振荡器125的运作,压控振荡器125的输出信号VCO_OUT将会乱漂(因为没有数字输入数据DIN可以参考)。

故而,于本案实施例中,当数字输入数据DIN暂时消失时,透过计数器与脉冲产生器130、电压产生器135、临界侦测器140、第一逻辑门145、第二逻辑门150与第二电荷泵155的运作,将使得压控振荡器125的输出信号VCO_OUT的频率能被维持于既定范围内,降低压控振荡器125的输出信号VCO_OUT的频率的漂动范围。

现将说明,本案实施例中,当数字输入数据DIN暂时消失时,透过计数器与脉冲产生器130、电压产生器135、临界侦测器140、第一逻辑门145、第二逻辑门150与第二电荷泵155的运作原则。

请参考图4A与图4B,其显示根据本案实施例的信号波形图。于时期T1内,由于计数器与脉冲产生器130提供逻辑高的计数时间CNT_OUT,使得电压产生器135的电容C被充电,故而,电压产生器135的电压VRC上升。当时期T1结束而进入到时期T2时,由于计数器与脉冲产生器130提供逻辑低的计数时间CNT_OUT,使得电压产生器135的电容C不再被充电,故而,电压产生器135的电压VRC维持。于时期T2内,临界侦测器140将电压产生器135所产生的电压VRC分别比较于第一临界值VH与第二临界值VL,以产生2个比较结果VRC_VH与VRC_VL。在图4A中,由于电压VRC高于第一临界值VH且未低于第二临界值VL,故而,于时期T2内,临界侦测器140产生逻辑高的比较结果VRC_VH与逻辑低的VRC_VL。由于在时期T2内,比较结果VRC_VH与输出脉冲PUS_OUT皆为逻辑高,故而,第一逻辑门145产生逻辑高的信号PUS_UP;以及比较结果VRC_VL为逻辑低但输出脉冲PUS_OUT为逻辑高,故而,第二逻辑门150产生逻辑低的信号PUS_DN。逻辑高的信号PUS_UP会输入至第二电荷泵155,使得第二电荷泵155提供充电路径给循环滤波器120,以加速压控振荡器125。也就是说,如图4A所示,由于压控振荡器125较慢(压控振荡器125较慢是指,压控振荡器125的输出信号VCO_OUT的频率较低,反之亦然),使得计数时间CNT_OUT较长(对电压VRC的充电时间较长),故而,电压VRC高于第一临界值VH。本案实施例可以产生信号PUS_UP来加速压控振荡器125。

相似地,于时期T3内,由于计数器与脉冲产生器130提供逻辑高的计数时间CNT_OUT,使得电压产生器135的电容C被充电,故而,电压产生器135的电压VRC上升。当时期T3结束而进入到时期T4时,由于计数器与脉冲产生器130提供逻辑低的计数时间CNT_OUT,使得电压产生器135的电容C不再被充电,故而,电压产生器135的电压VRC维持。于时期T4内,临界侦测器140将电压产生器135所产生的电压VRC分别比较于第一临界值VH与第二临界值VL,以产生2个比较结果VRC_VH与VRC_VL。在图4B中,由于电压VRC未高于第一临界值VH且低于第二临界值VL,故而,于时期T4内,临界侦测器140产生逻辑低的比较结果VRC_VH与逻辑高的VRC_VL。由于在时期T4内,比较结果VRC_VH为逻辑低而输出脉冲PUS_OUT为逻辑高,故而,第一逻辑门145产生逻辑低的信号PUS_UP;以及比较结果VRC_VL为逻辑高且输出脉冲PUS_OUT也为逻辑高,故而,第二逻辑门150产生逻辑高的信号PUS_DN。逻辑高的信号PUS_DN会输入至第二电荷泵155,使得第二电荷泵155提供放电路径给循环滤波器120,以减慢压控振荡器125。也就是说,如图4B所示,由于压控振荡器125较快,使得计数时间CNT_OUT较短(对电压VRC的充电时间较短),故而,电压VRC低于第二临界值VL。本案实施例可以产生信号PUS_DN来减慢压控振荡器125。

由上述可知,于本案实施例中,如果计数时间CNT_OUT结束时,电压产生器135的电压VRC介于第一临界值VH与第二临界值VL之间,则第一逻辑门145产生逻辑低的信号PUS_UP且第二逻辑门150产生逻辑低的信号PUS_DN。故而,第二电荷泵155并无提供充电路径也无提供放电路径给循环滤波器120,所以,压控振荡器125得以维持其输出信号VCO_OUT的频率。

图5显示根据本案一实施例的频率数据恢复电路的频率维持方法的流程图。于步骤510中,当一数字输入数据暂时消失时,于一计数时间内,让一输出电压上升。于步骤520中,将该输出电压分别比较于复数个临界值,以产生复数个比较结果。于步骤530中,根据该些比较结果而产生一控制信号,以控制该压控振荡器加速或减速。

由上述可知,即便在暂时接收不到数字输入数据DIN的情况下,本案实施例仍可以有效维持压控振荡器125的输出信号VCO_OUT的频率,不致于乱漂。

综上所述,虽然本发明已以实施例揭露如上,然其并非用以限定本发明。本发明所属技术领域中具有通常知识者,在不脱离本发明的精神和范围内,当可作各种的更动与润饰。因此,本发明的保护范围当视权利要求书所界定者为准。

- 一种频率数据恢复电路与其频率维持方法

- 时钟数据恢复电路及其频率侦测方法