一种高分辨率的两级时间数字转换器及转换方法

文献发布时间:2023-06-19 13:49:36

技术领域

本发明涉及集成电路设计,尤其涉及一种高分辨率的两级时间数字转换器及转换方法。

背景技术

时间数字转换器(Time to Digital Converter,TDC)是一种将时间间隔转换为数字信号的器件,可以用来计量两个输入信号之间的相位差。

中国专利:CN111313902A,2020.06.19(参考文献1)公开了一种时间数字转换器及其转换方法,该时间数字转换器包括:y个快延迟单元和x个慢延迟单元,用于建立两条延时不一样的延时链路;y个快延时开关和x个慢延时开关,用于控制逐次比较时的接入的延迟单元;一个仲裁器,用于仲裁时间差;一个逐次逼近逻辑电路,用于查找权重映射逻辑表。此结构可以减小仲裁器的数量以减小面积,但是动态范围较小,从输入到输出需要多个周期,效率相对较低,分辨率高需要极长的延时链,面积会更大。

为了克服这些问题,需要设计出拥有高速率、高分辨率、宽动态范围和量化结果准确的时间数字转换器。

发明内容

发明目的:针对现有技术存在的问题,本发明提供一种高分辨率的两级时间数字转换器及转换方法,本发明结构和设计简单,高速率,可测动态范围大,高分辨率,实现时芯片面积更小。

技术方案:为了实现上述发明目的,本发明的一种高分辨率的两级时间数字转换器及转换方法,该两级时间数字转换器包括抽头延迟链模块、粗精接口电路模块、游标卡尺型延迟链模块、编码电路模块;反馈信号和参考时钟信号输入到抽头延迟链模块,抽头延迟链模块通过粗精接口电路模块与游标卡尺型延迟链模块相连,编码电路模块将抽头延迟链模块和游标卡尺型延迟链模块的输出转换成二进制码;

一种时间数字转换方法包括以下步骤:

步骤1、采用抽头延迟链模块对反馈信号和参考时钟信号的时间差进行粗略测量,输出位宽为N

步骤2、采用粗精接口电路模块对抽头延迟链模块测量产生的剩余时间差进行处理,得到第一粗精接口输出信号和第二粗精接口输出信号,传递给游标卡尺型延迟链模块;

步骤3、采用游标卡尺型延迟链模块对第一粗精接口输出信号和第二粗精接口输出信号进行量化,得到位宽为N

步骤4、将步骤1抽头延迟链模块的测量数据Q[1],Q[2],…,Q[N

进一步的,所述抽头延迟链模块即粗量延迟链模块,包括N

进一步的,所述粗精接口电路模块包括第一粗精接口和第二粗精接口,第一粗精接口包括第一延迟单元、第一32选1选择器、第一2选1选择器和第一D触发器;第一粗精接口的输入即第一延迟单元的输入是抽头延迟链模块中延迟单元的输出,第一延迟单元的输出连接到第一32选1选择器,第一32选1选择器的输出连接到第一2选1选择器,第一2选1选择器的另外一个输入端接地电平,第一2选1的选择器的输出连接到第一D触发器的采样端,第一D触发器的数据端连接高电平,第一D触发器输出第一粗精接口输出信号连接到游标卡尺型延迟链模块的慢延迟链输入端;

第二粗精接口包括第二延迟单元,第二32选1选择器,第二2选1选择器和第三延迟单元,第二粗精接口的输入即第二延迟单元的输入是抽头延迟链模块中N

进一步的,所述游标卡尺型延迟链模块即精量延时链模块包括慢延迟链和快延迟链,具体结构为:慢延迟链中N

进一步的,所述编码电路模块即温度码编码电路,其中包括M级依次连接的全加器电路模块。

进一步的,所述步骤2具体包括:

步骤2.1、第一粗精接口中的第一32选1选择器对经过第一延迟单元后的延迟信号进行选择,第一32选1选择器的选择使能信号来自编码电路模块的二进制输出;

步骤2.2、根据步骤2.1中第一32选1选择器输出结果,第一2选1选择器在Q[0]的使能下选择是否将第一32选1选择器的选择结果进行输出:在Q[0]为0时,输出结果为0;在Q[0]为1时,输出第一32选1选择器的输出结果;

步骤2.3、第一2选1选择器输出结果输出到第一D触发器的采样端,去采样高电平信号,第一D触发器输出即第一粗精接口输出信号作为游标卡尺型延迟链模块中慢延迟链的输入信号;

步骤2.4、第二粗精接口中的第二32选1选择器对经过第二延迟单元的信号进行选择,第二32选1选择器的选择使能信号来自编码电路模块的二进制输出;

步骤2.5、根据步骤2.4第二32选1选择器输出结果,第二2选1选择器在Q[0]的使能下选择是否将第二32选1选择器的选择结果进行输出:在Q[0]为0时,输出结果为0;在Q[0]为1时,输出第二32选1选择器的输出结果;

步骤2.6、第二2选1选择器的输出结果输出给第三延迟单元输入端,第三延迟单元的输出即第二粗精接口输出信号作为游标卡尺型延迟链模块中快延迟链的输入信号。

进一步的,所述步骤4具体包括:

步骤4.1、分别提取步骤1抽头延迟链模块的测量数据Q[1],Q[2],…,Q[N

步骤4.2、根据步骤4.1输出的求和结果和进位结果,第二级全加器电路模块再次对第一级结果进行压缩,输出第二级的求和结果和进位结果,第i级以此类推;

步骤4.3、将倒数第二级的求和结果和进位结果输入最后一级全加器模块,输出的结果作为的最终输出,即将反馈信号和参考时钟信号的差值转换为固定位宽、有权位的二进制码。

有益效果:与现有技术相比,本发明的显著优点是:使用路径匹配的粗精接口电路模块将两级延迟链连接起来,减小了由第一级时间数字转换器传递至第二级时间数字转换器的延迟误差,使本发明具有抽头延迟链较高的动态范围和游标卡尺型延迟链较宽的动态范围两种优点,结构简单,速率更快;本发明当中的编码电路由代码综合生成,所以针对不同的工艺有更优的移植性并更利于集成。

附图说明

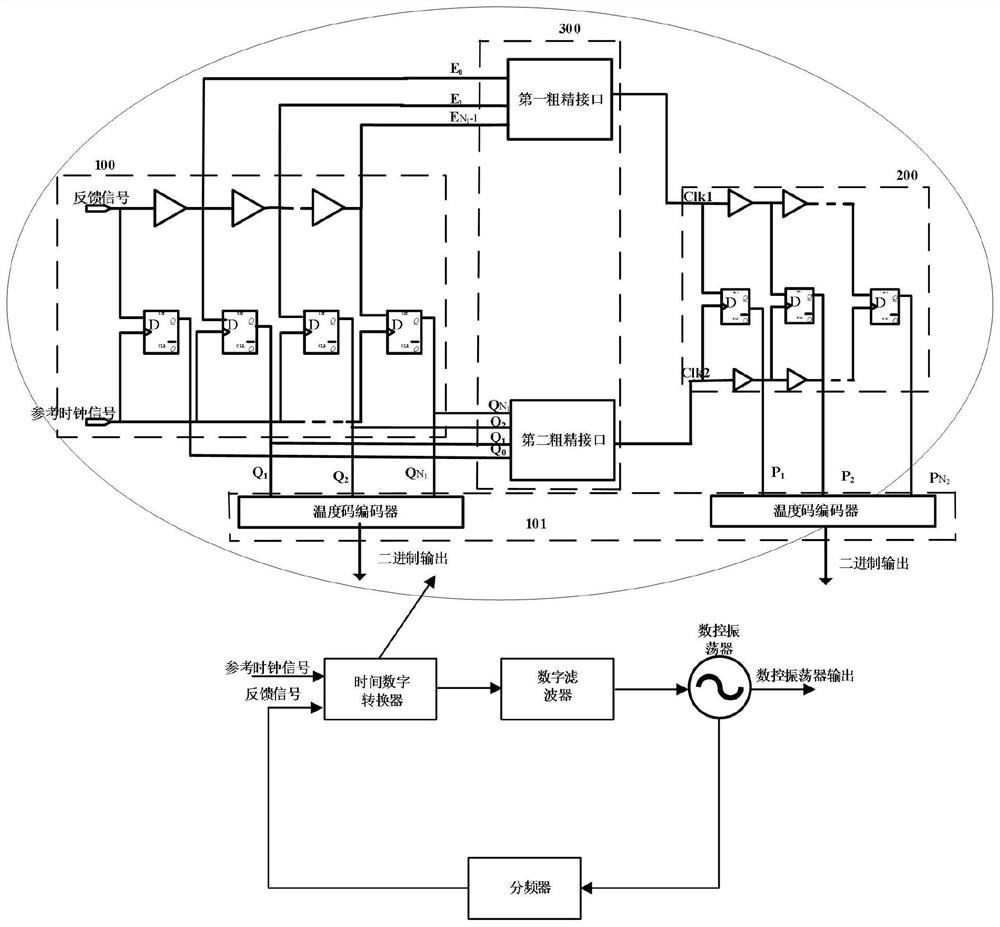

图1为本发明的时间数字转换器结构图;

图2为时间数字转换器中第一粗精接口的结构图;

图3为时间数字转换器中第二粗精接口的结构图。

图中有:抽头延迟链模块100,游标卡尺型延迟链模块200,粗精接口电路模块300,编码电路模块101;第一延迟单元102,第一32选1选择器103,第一2选1选择器104,第一D触发器105,地电平GND1,高电平VDD;第二延迟单元106,第二32选1选择器107,第二2选1选择器108,第三延迟单元109;第一粗精接口输出信号clk1,第二粗精接口输出信号clk2。

具体实施方式

下面结合实施例对本发明技术方案进行详细说明。

本发明提供了一种高分辨率的两级时间数字转换器及转换方法,该两级时间数字转换器结构如图1所示,包括抽头延迟链模块100,游标卡尺型延迟链模块200,编码电路模块101和粗精接口电路模块300。抽头延迟链模块100通过粗精接口电路模块300与游标卡尺型延迟链模块200相连,抽头延迟链模块100与游标卡尺型延迟链模块200的输出经过编码电路模块101输出二进制码,此二进制码是时间数字转换器的最终输出。

抽头延迟链模块100和游标卡尺型延迟链模块200用于对反馈信号和参考时钟信号的误差进行粗量化;编码电路模块101通过编码电路将两个延迟链输出进行编码,转换成有权位的二进制码;粗精接口电路模块300,对抽头延迟链模块100的量化结果作出正确的选择,再传输给游标卡尺型延迟链模块200,减小由第一级时间数字转换器传递至第二级时间数字转换器的延迟误差,使两级时间数字转换器的量化结果更精确。

其中,抽头延迟链模块100和游标卡尺型延迟链模块200都是传统的延迟链模块,计算本发明中时间数字转换器的动态范围为抽头延迟链模块的动态范围和游标卡尺型延迟链模块的动态范围相加。

抽头延迟链模块100即粗量延迟链模块,包括N

游标卡尺型延迟链模块200即精量延时链模块包括慢延迟链和快延迟链,具体结构为:慢延迟链中N

抽头延时链模块的动态范围T

T

式中,N

游标卡尺型延迟链的动态范围T

T

式中,N

数字时间转换器的动态范围T为T=T

编码电路模块101包括M级依次连接的全加器电路模块,其中,第一级和第二级包括1/4·(N

粗精接口电路模块300包括第一粗精接口和第二粗精接口,第一粗精接口结构如图2所示,包括第一延迟单元102、第一32选1选择器103、第一2选1选择器104和第一D触发器105;第一粗精接口的输入即第一延迟单元102的输入是抽头延迟链模块100中延迟单元的输出,第一延迟单元102的输出连接到第一32选1选择器103,第一32选1选择器103根据选择信号进行合适的选择,选择信号来自编码电路模块101的二进制输出结果,第一32选1选择器103连接到第一2选1选择器104,第一2选1选择器104的另外一个输入端接地电平GND1,第一2选1选择器104的选择信号来自Q[0];第一2选1的选择器104输出连接第一D触发器105的采样端,第一D触发器105的数据端接入高电平VDD,第一D触发器105的输出即第一粗精接口输出信号clk1连接到游标卡尺型延迟链模块200的慢延迟链输入端;

第二粗精接口结构如图3所示,包括第二延迟单元106,第二32选1选择器107,第二2选1选择器108和第三延迟单元109,第二粗精接口的输入即第二延迟单元106的输入是抽头延迟链模块100中N

本实例还提供了一种时间数字转换方法,包括:

步骤1、采用抽头延迟链模块100对反馈信号和参考时钟信号的时间差进行粗略测量,利用抽头延迟链模块100的宽动态范围的特点,保证可以测量宽范围的误差,并且输出位宽为N

步骤2、由于抽头延迟链模块100较低的分辨率,测量时会产生较大的剩余时间差,采用粗精接口电路模块300将剩余时间差传递到高分辨率的游标卡尺延迟链模块200,具体过程为:采用粗精接口电路模块300中的第二粗精接口将Q[0],Q[1],…,Q[N

步骤2.1、抽头延迟链模块100的延迟信号E[0],E[1],…,E[N

步骤2.2、抽头延迟链模块100输出的Q[0],Q[1],…,Q[N

步骤3、采用游标卡尺型延迟链模块200对第一粗精接口输出信号clk1和第二粗精接口输出信号clk2进行量化,得到测量数据P[1],P[2],…,P[N

步骤4、采用编码电路模块101对抽头延迟链模块100的测量数据Q[1],Q[2],…,Q[N

步骤4.1、提取抽头延迟链模块100的测量数据Q[1],Q[2],…,Q[N

步骤4.2、根据步骤4.1输出的求和结果和进位结果,第二级全加器电路模块再次对第一级结果进行压缩,输出第二级的求和结果和进位结果,第i级以此类推;

步骤4.3、将倒数第二级的求和结果和进位结果输入最后一级全加器模块,输出的结果作为抽头延迟链模块的最终输出,即将参考信号和反馈信号的差值转换为固定位宽、有权位的二进制码。

本实施例通过改变时间数字转换器的结构,将电路结构设计为两级时间数字转换器,使时间数字转换器在具有较高的精度同时还有较宽的动态范围。并且还加入了路径匹配的粗精调接口电路,减小了由第一级时间数字转换器传递至第二级时间数字转换器的延迟误差,使两级时间数字转换器的量化结果更精确。本实施例当中的编码电路由代码综合生成,所以针对不同的工艺有更优的移植性并更利于集成。

以上内容仅为说明本发明的技术思想,不能以此限定本发明的保护范围,凡是按照本发明提出的技术思想,在技术方案基础上所做的任何改动,均落入本发明权利要求书的保护范围之内。