一种基于脉冲展宽的时间数字转换器

文献发布时间:2023-06-19 18:30:43

技术领域

本发明属于数字电路领域,具体涉及一种基于脉冲展宽的时间数字转换器。

背景技术

时间数字转换器(Time-to-digital converter,TDC)能够将时间间隔转化成数字信号,是时间量化处理系统中的核心部分。TDC有广泛的应用场景,例如激光雷达测距、医学成像、超声流量计等。最简单的TDC由延迟线和采样电路组成,通过记录所测时间间隔内信号传播的延时单元个数来量化时间间隔。不过此TDC的分辨率不能小于延时单元的延时,此外量程受到延时单元个数的限制。目前已有多种TDC结构使分辨率小于延时单元的延时,例如游标型TDC、局部无源插值TDC、脉冲收缩TDC等。在游标型TDC中,开始信号在一个慢延迟链中传播,结束信号在一个快延迟链中传播,通过计数结束信号追上开始信号所经过的延时单元个数,可以将分辨率减小为快慢延时单元的延时差。局部无源插值TDC在延时单元的首尾之间插入多个电阻,在延时单元的延时之间插入了多个上升沿,从而使分辨率低于延时单元的延时。脉冲收缩TDC中,输入延时单元的信号的上升沿传播延时大于下降沿传播延时,因此一个脉冲信号在经过一定数量的延时单元之后,最终收缩成一个固定的电平,脉冲收缩TDC的分辨率为上升沿与下降沿的传播延时之差。为了实现大的测量范围,一般采取多步的测量,使用外部时钟或者大分辨率的TDC(通常是环形TDC的形式)进行初步的量化,再用精细的TDC对余量进行精细的量化。

脉冲展宽电路可以将一个窄脉冲按一定比例展宽成一个宽脉冲,可以通过对宽脉冲的量化实现对窄脉冲的量化,从而减小分辨率。文献[1]将输入信号上升沿与时钟上升沿之间的时间间隔输入脉冲展宽电路,将脉冲展宽约240倍,之后通过80MHz的时钟进行计数,从而实现50ps的分辨率。文献[1]的TDC的缺点是需要片外输入高频时钟,而且脉冲展宽的展宽倍数需要外部电路进行校准。文献[2]在文献[1]的基础上改进了脉冲展宽电路,使其有三斜率的展宽。不过并没有解决文献[1]的缺点。文献[3]中,脉冲展宽电路作为时间放大器,将时间间隔精确放大4倍。不过文献[3]中,决定分辨率的是其中的游标型TDC,与脉冲展宽电路的展宽倍数无关。此外,脉冲展宽电路需要精确放大,需要配合其他额外的电路,电路较为复杂。

参考文献:

[1]Chen P,Chen C C,Shen Y S.A Low-Cost Low-Power CMOS Time-to-DigitalConverter Based on Pulse Stretching[J].IEEE Transactions on Nuclear Science,2006,53(4):2215-2220.

[2]Kim M,Lee H,Woo J K,et al.A Low-Cost and Low-Power Time-to-DigitalConverter Using Triple-Slope Time Stretching[J].IEEE Transactions onCircuits&Systems II Express Briefs,2011,58(3):169-173.

[3]郭围围,尹勇生,龚号,孟煦,陈珍海,邓红辉.基于时间放大技术的时间数字转换器的设计[J].电子测量与仪器学报,2022,36(04):98-105.DOI:10.13382/j.jemi.B2104759.3

综上,现有技术的缺点概况如下:1.基于脉冲展宽电路的TDC需要高频的片外输入时钟;2.脉冲展宽电路的校准在片外进行;3.MDLL的静态相位误差对TDC的结果有直接影响。

发明内容

本发明的主要目的在于克服现有技术中的不足,并提出一种基于脉冲展宽的时间数字转换器,提供一种用于测量时间间隔的电路,以及用于克服MDLL静态相位误差的算法。

本发明所采用的具体技术方案如下:

一种基于脉冲展宽的时间数字转换器,其包括倍频延迟锁相环、脉冲产生电路、校准电路、延时电路、编码器、脉冲展宽电路、第一选择器、第一计数器、第二计数器、第三计数器;

倍频延迟锁相环的输入为片外参考时钟CLKREF,第一个输出为高频时钟CLK,第二个输出为多相时钟CLK

脉冲产生电路的第一个输入为倍频延迟锁相环的输出CLK,第二个输入为待量化信号INPUT,第一个输出信号为P1,第二个输出为CEN;

校准电路的第一个输入为倍频延迟锁相环的输出CLK,第二个输入为使能信号CALIBRATION,第三个输入为脉冲展宽电路的输出DONE,输出信号为P2;

延时电路的第一个输入为倍频延迟锁相环的输出CLK,第二个输入为脉冲展宽电路的输出DONE,输出信号为RESET;

编码器的第一个输入为为倍频延迟锁相环的输出CLK

脉冲展宽电路的第一个输入为第一选择器的输出TOUT,第二个输入为延时电路的输出RESET,输出信号为DONE;

第一选择器的第一个输入为脉冲产生电路的输出信号P1,第二个输入为校准电路的输出信号P2,第三个输入为使能信号CALIBRATION,输出信号为TOUT;

第一计数器的第一个输入为脉冲产生电路的输出CEN,第二个输入为倍频延迟锁相环的输出CLK;第一计数器的输出为COARSE<19:0>,作为粗量化结果;

第二计数器的第一个输入为第一选择器的输出TOUT,第二个输入为倍频延迟锁相环的输出CLK,第三个输入为脉冲展宽电路的输出DONE;第二计数器的输出为FINE<7:0>,作为精细量化结果的一部分;

第三计数器的第一个输入为脉冲产生电路的输出CEN,第二个输入为片外参考时钟CLKREF;第三计数器的输出为OUTM,用于消除倍频延迟锁相环静态相位误差的影响。

作为优选,所述校准电路中的校准信号产生电路包括第一D触发器、第二D触发器、第三D触发器、第二选择器、第一与门、反相器;

第一D触发器的D端连接第一D触发器的

第二选择器的第一输入连接CLK,第三输入连接选择信号SEL;

第二D触发器的D端连接第二D触发器的

第三D触发器的D端连接电源电压VDD,时钟输入端连接反相器的输出,复位端连接复位信号RN,Q端悬空,

第一与门的输出为P2。

作为优选,所述校准信号产生电路工作过程中,按照选择信号SEL将CLK二分频或者四分频,右侧的反相器、第三D触发器及第一与门能够将分频后的时钟转为一次性的脉冲,配合输入的复位信号RN,依次持续输出一个时钟周期和两个时钟周期宽度的脉冲。

作为优选,所述校准电路中,除校准信号产生电路外置还包含生成选择信号SEL与复位信号RN的逻辑电路,生成逻辑为:

1、当CALIBRATION为低电平时,RN为低电平;

2、当CALIBRATION由低电平切换为高电平后,RN由低电平切换为高电平;

3、当CALIBRATION处于高电平情况下,不断循环执行以下过程:

首先,P2输出脉冲;

然后,当P2输出一次脉冲之后RN转为为低电平,SEL进行平切换;

再后,等待脉冲展宽电路输出信号DONE由高电平转为低电平之后,RN转为高电平。

作为优选,所述脉冲产生电路包括第四D触发器、第五D触发器、第二与门;

第四D触发器的D端连接电源电压VDD,时钟输入端连接CLK,复位端连接INPUT,Q端连接第五D触发器的D端,

第五D触发器的时钟输入端连接CLK,复位端连接复位信号RST,Q端悬空,

第二与门的第二输入为INPUT,输出为P1。

作为优选,所述脉冲展宽电路包括第一电容、第二电容、第一电流源、第二电流源、第一MOS管、第二MOS管、第三MOS管、第四MOS管、逻辑电路以及比较器;第二电容的容值大于第一电容;

第一电容一端接地,另一端连接第一MOS管的漏极、第三MOS管的漏极以及比较器的正输入端;

第二电容一端接地,另一端连接第二MOS管的漏极、第四MOS管的漏极以及比较器的负输入端;

第一MOS管的栅极连接逻辑电路的第一输出T

第二MOS管的栅极连接逻辑电路的第二输出T

第一电流源以及第二电流源的电流输出端为地;

第三MOS管以及第四MOS管的源极均连接电源电源VDD,栅极均连接复位信号RESET;

逻辑电路的输入为第一选择器的输出TOUT;

比较器的输出为DONE。

作为优选,所述脉冲展宽电路工作过程中,在输入脉冲信号TOUT后,逻辑电路先输出与TOUT同宽度的脉冲信号T

作为优选,所述基于脉冲展宽的时间数字转换器中,倍频延迟锁相环倍频输入参考时钟CLKREF,一方面产生高频率的时钟CLK用于输入其他电路,另一方面输出多相时钟CLK

作为优选,所述输入信号INPUT上升沿的量化结果为:

式中:T

作为优选,所述输入信号INPUT上升沿的量化结果为:

式中:系数a和b需要满足以下三个条件:a mod 2=OUTM,M*a+b=D

本发明相对于现有技术而言,具有以下有益效果:

现有技术需要高频的输入时钟,并且对脉冲展宽电路的校准需要片外电路,难以实时校准。在有倍频电路的TDC中,为了避免MDLL静态相位误差的影响,一些已有方案采取PLL+DLL的方法,电路成本较高。本发明提出的TDC结构结合了MDLL、脉冲展宽电路以及校准电路,保证高分辨率的同时能有效增大了TDC的量程,并且能够减少PVT的影响。其中的校准电路结构简单,校准成本低,适用于脉冲展宽电路的校准。此外,针对MDLL静态相位误差的校准算法,只需增加一个1bit计数器,额外的电路成本极小,同时能够克服MDLL静态相位误差的影响。

附图说明

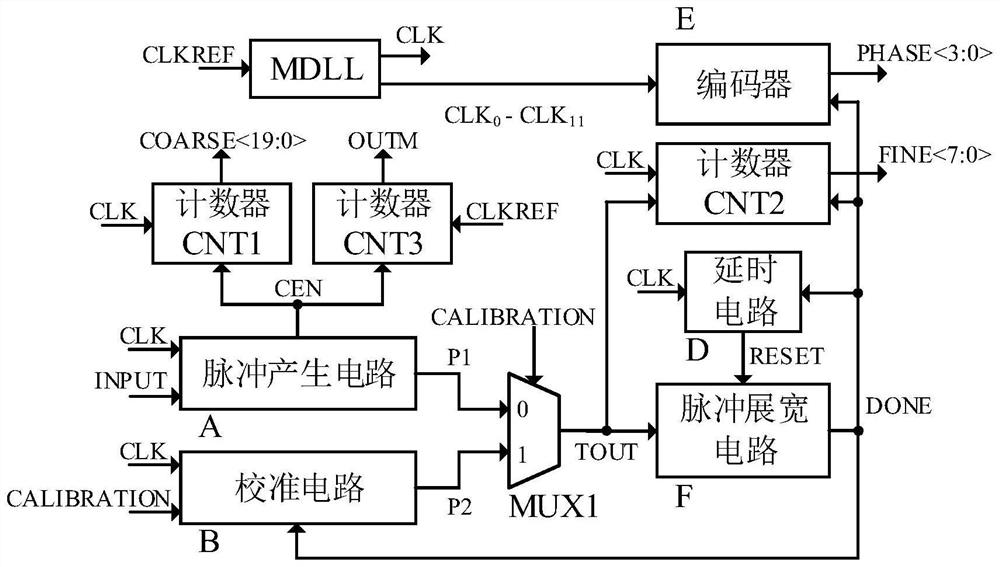

图1为基于脉冲展宽的时间数字转换器整体结构图。

图2为正常工作时TDC的时序图。

图3为校准电路中校准信号产生电路。

图4为脉冲产生电路。

图5为脉冲展宽电路。

图6为脉冲展宽电路中电容电压示意。

具体实施方式

为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图对本发明的具体实施方式做详细的说明。在下面的描述中阐述了很多具体细节以便于充分理解本发明。但是本发明能够以很多不同于在此描述的其它方式来实施,本领域技术人员可以在不违背本发明内涵的情况下做类似改进,因此本发明不受下面公开的具体实施例的限制。本发明各个实施例中的技术特征在没有相互冲突的前提下,均可进行相应组合。

在本发明的描述中,需要理解的是,术语“第一”、“第二”仅用于区分描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。

本发明提出了一种基于脉冲展宽的时间数字转换器(TDC)结构,并提出一种校准算法以应对MDLL中静态相位误差的影响。该TDC使用倍频延迟锁相环(Multiplying delay-locked loop,MDLL)倍频较低的输入参考时钟,倍频后的时钟可以对输入时刻进行粗量化;脉冲展宽电路将粗量化之后的余量以一定比例展宽,进而实现高分辨率的量化;通过对时刻的量化,此TDC能够应用于输入间隔小于飞行时间的场景,例如超声流量计。时间间隔的测量结果是所需的两个时刻的量化结果t

在本发明的一个较佳实施例中,提供了一种基于脉冲展宽的时间数字转换器,其基本工作原理如图1所示,具体的电路结构包括倍频延迟锁相环MDLL、脉冲产生电路A、校准电路B、延时电路D、编码器E、脉冲展宽电路F、第一选择器MUX1、第一计数器CNT1、第二计数器CNT2、第三计数器CNT3。下面对各电路模块的具体连接方式和信号传输过程进行详细描述。

倍频延迟锁相环MDLL的输入为片外参考时钟CLKREF,第一个输出为高频时钟CLK,第二个输出为多相时钟CLK

脉冲产生电路A的第一个输入为倍频延迟锁相环MDLL的输出CLK,第二个输入为待量化信号INPUT,第一个输出信号为P1,第二个输出为CEN;

校准电路B的第一个输入为倍频延迟锁相环MDLL的输出CLK,第二个输入为使能信号CALIBRATION,第三个输入为脉冲展宽电路F的输出DONE,输出信号为P2;

延时电路D的第一个输入为倍频延迟锁相环MDLL的输出CLK,第二个输入为脉冲展宽电路F的输出DONE,输出信号为RESET;

编码器E的第一个输入为为倍频延迟锁相环MDLL的输出CLK

脉冲展宽电路F的第一个输入为第一选择器MUX1的输出TOUT,第二个输入为延时电路的输出RESET,输出信号为DONE;

第一选择器MUX1的第一个输入为脉冲产生电路A的输出信号P1,第二个输入为校准电路B的输出信号P2,第三个输入为使能信号CALIBRATION,输出信号为TOUT;

第一计数器CNT1的第一个输入为脉冲产生电路A的输出CEN,第二个输入为倍频延迟锁相环MDLL的输出CLK;第一计数器CNT1的输出为COARSE<19:0>,作为粗量化结果;

第二计数器CNT2的第一个输入为第一选择器MUX1的输出TOUT,第二个输入为倍频延迟锁相环MDLL的输出CLK,第三个输入为脉冲展宽电路F的输出DONE;第二计数器CNT2的输出为FINE<7:0>,作为精细量化结果的一部分;

第三计数器CNT3的第一个输入为脉冲产生电路A的输出CEN,第二个输入为片外参考时钟CLKREF;第三计数器CNT3的输出为OUTM,用于消除倍频延迟锁相环MDLL静态相位误差的影响。

图2是TDC量化一个INPUT上升沿的时序图。在该TDC中,倍频延迟锁相环MDLL倍频输入参考时钟CLKREF,一方面产生较高频率的时钟CLK用于输入其他电路,另一方面输出多相时钟CLK

上述过程中,在余量中额外增加一个时钟周期的偏移,是为了保证脉冲展宽电路在输入余量很小时仍满足电路最小建立时间的要求,使得脉冲展宽电路实际输入范围保持在1~2个时钟周期内。

在本发明的实施例中,进一步给出了校准电路B的校准信号产生电路、脉冲产生电路A、脉冲展宽电路F的具体电路结构原理,下面对三者分别进行展开描述。

如图3所示,校准电路B的校准信号产生电路中,包括第一D触发器DFF1、第二D触发器DFF2、第三D触发器DFF3、第二选择器MUX2、第一与门AND1、反相器INV。其中:

第一D触发器DFF1的D端连接第一D触发器DFF1的

第二选择器MUX2的第一输入连接CLK,第三输入连接选择信号SEL;

第二D触发器DFF2的D端连接第二D触发器DFF2的

第三D触发器DFF3的D端连接电源电压VDD,时钟输入端连接反相器INV的输出,复位端连接复位信号RN,Q端悬空,

第一与门AND1的输出为P2。

如图4所示,脉冲产生电路A包括第四D触发器DFF4、第五D触发器DFF5、第二与门AND2;

第四D触发器DFF4的D端连接电源电压VDD,时钟输入端连接CLK,复位端连接INPUT,Q端连接第五D触发器DFF5的D端,

第五D触发器DFF5的时钟输入端连接CLK,复位端连接复位信号RST,Q端悬空,

第二与门AND2的第二输入为INPUT,输出为P1。

如图5所示,脉冲展宽电路F包括第一电容C

第一电容C

第二电容C

第一MOS管M

第二MOS管M

第一电流源I

第三MOS管M

逻辑电路LOGIC的输入为第一选择器MUX1的输出TOUT;

比较器COMP的输出为DONE。

上述实施例中设计的TDC通过分别量化开始与结束信号的输入时刻,再将量化结果的差作为时间间隔,可以使开始与结束信号通过的路径相同,避免电路自身传播延时对结果的影响。下面具体对其电路原理和结果量化过程进行详细描述。

本发明中通过采用粗量化和细量化结合的分步量化,可以在保证高分辨率的同时能有效增大TDC的量程。假设输入参考时钟周期为T

脉冲展宽电路按一定比例展宽输入脉冲,效果类似于将粗量化的余量放大,进而提高分辨率。假设展宽比例为K,MDLL有P个相位,则TDC的分辨率r为:

假设记录的第一计数器CNT1结果COARSE<19:0>为D

通过上述公式(3),即可计算输入信号INPUT上升沿的具体量化结果。

当然,本发明中还进一步提供了用于克服MDLL静态相位误差的改进算法,该算法可在测出时钟确定性抖动之后降低MDLL静态相位误差对于量化结果的影响。下面具体进行展开描述。

在信号CALIBRATION为高电平的情况下,电路进入校准模式。校准模式下TDC的各个模块的主要功能与正常工作时相同,因此该TDC校准方便,无需额外的片外信号。

校准电路B用于产生校准信号,校准电路B中除了校准信号产生电路之外还需要包含生成选择信号SEL与复位信号RN的逻辑电路。

图3是校准电路B中的校准信号产生电路的原理图,校准信号产生电路工作过程中,按照选择信号SEL将CLK二分频或者四分频,右侧的反相器INV、第三D触发器DFF3及第一与门AND1能够将分频后的时钟转为一次性的脉冲,配合输入的复位信号RN,依次持续输出一个时钟周期和两个时钟周期宽度的脉冲。因此,校准电路持续地产生两个脉冲,其脉冲宽度之差为一个时钟周期T

校准电路B中,校准信号产生电路外还需要依赖于其他逻辑电路来生成选择信号SEL与复位信号RN,其生成逻辑为:

1、当CALIBRATION为低电平时,RN为低电平;

2、当CALIBRATION由低电平切换为高电平后,RN由低电平切换为高电平;

3、当CALIBRATION处于高电平情况下,不断循环执行以下过程:

首先,P2输出脉冲;

然后,当P2输出一次脉冲之后RN转为为低电平,SEL进行平切换;

再后,等待脉冲展宽电路F输出信号DONE由高电平转为低电平之后,RN转为高电平。

只要CALIBRATION保持高电平,电路状态将不断循环上述步骤3。

图5是脉冲展宽电路F的原理图,图6是脉冲展宽电路F中电容电压示意图,展示了在脉冲展宽电路F工作时,电容C

ΔT=(AB+1)·ΔT

传播延时T

通过输出信号OUTM,采用本发明提出的改进算法可克服MDLL静态相位误差的影响,具体而言,改进算法如下:

MDLL静态相位误差会导致MDLL输出的CLK有两种周期。假设T

例如,本发明实施例中使用的MDLL的倍频比例M为32,因此在每个参考时钟周期内,MDLL会输出32个CLK周期。其中有31个CLK周期为T

在测得T

式中:系数a和b需要满足以下三个条件:a mod 2=OUTM,M*a+b=D

由此可见,本发明的上述改进算法将粗量化的计算由简单的D

以上所述的实施例只是本发明的一种较佳的方案,然其并非用以限制本发明。有关技术领域的普通技术人员,在不脱离本发明的精神和范围的情况下,还可以做出各种变化和变型。因此凡采取等同替换或等效变换的方式所获得的技术方案,均落在本发明的保护范围内。