时间数字转换器

文献发布时间:2023-06-19 19:33:46

技术领域

本发明涉及时间数字转换器,特别涉及适合用于半导体检查装置(半导体测试仪)的时间数字转换器。

背景技术

以往,公知在对被检查对象、例如IC、LSI等进行检查的半导体检查装置中,有进行信号的时间测定的装置(例如,参照专利文献1)。

另外,作为时间和/或频率的测定方法,迄今为止提出了各种方法,作为代表性的方法,可列举通用计数方式、时间扩展方式、时间电压转换方式、时间游标方式等。

其中,例如,在通用计数方式中,是通过对内置的基准时钟输入信号进行指定的时间测量从而进行时间测定的方法。另外,时间扩展方式是将时间转换为电压来进行测定的方式,是利用积分电路对零数时间的脉冲宽度进行充放电,并进行脉冲宽度扩展的方法。

现有技术文献

专利文献

专利文献1:日本特开2003-139817号公报

发明内容

技术问题

然而,在作为半导体检查装置中的一个功能而进行时间测定的情况下,在以往的方法中存在限度。

即,在半导体检查装置中,虽然能够通过具备时间数字转换器来进行时间测定,但在该情况下,作为不需要ASIC(application specific integrated circuit:专用集成电路)和/或模拟电路设计的通用技术,通常采用使用了FPGA(field-programmable gatearray:现场可编程门阵列)的时间数字转换器。在此,在通常的FPGA中,时钟频率为几百MHz,能够测定的最小量被限制为nsec量级。

另一方面,在半导体检查装置所采用的时间数字转换器中,测定(测量)的分辨率的高度、测定动态范围的广度、以及测定的高速性很重要,在现状下,例如期望100ps左右的分辨率下的测定。在该情况下,作为基准时钟则需要10GHz,为了实现高精度、高分辨率、高速,结果需要制作ASIC或另外设计模拟电路,存在时间数字转换器的成本变高的问题。这不限于通用计数方式,在采用以往已知的其他方式的时间数字转换器中也是同样低存在该问题。

另外,虽然能够使用示波器和PC(个人计算机)进行高精度、高分辨率的测定,但是在该情况下,高速处理存在限度。

本发明鉴于该实际情况,提供一种不需要ASIC和/或模拟电路设计就能够实现高精度、高分辨率、高速的时间数字转换器。

技术方案

本发明涉及一种时间数字转换器,其特征在于,测量输入波形中的第一时间点与第二时间点之间的时间间隔,所述时间数字转换器具备:基准计数单元,其对相对于所述时间间隔的主时间间隔进行计数而作为基准时钟的周期的整数倍;零数计数单元,其对零数时间间隔进行计数而作为所述主时间间隔相对于所述时间间隔的富余量、不足量;以及计数/转换单元,其基于所述主时间间隔和所述零数时间间隔计算出所述时间间隔,并将其转换为数字值,所述零数计数单元具有:倍频单元组,其分别由n个(n为2以上的整数)倍频单元构成,所述n个倍频单元生成以所述基准时钟的m倍频(m为2以上的整数)对与所述零数时间间隔对应的信号进行采样的信号;以及相位偏移单元,其使所述n个倍频单元所生成的所述信号各自的相位逐一偏移360°/n。

技术效果

根据本发明,起到能够提供一种不需要ASIC和/或模拟电路设计就能够实现高精度、高分辨率、高速的时间数字转换器这样的优异的效果。

附图说明

图1是说明本实施方式的时间数字转换器的图,图1的(A)是示出时间数字转换器的电路构成的一例的概要框图,图1的(B)是时间数字转换器中的时间测定的概要图。

图2是本实施方式的时间数字转换器中的时间测定的概要图,是图1的(B)的局部放大图。

图3是示出本实施方式的运算单元的一例的电路块概要图。

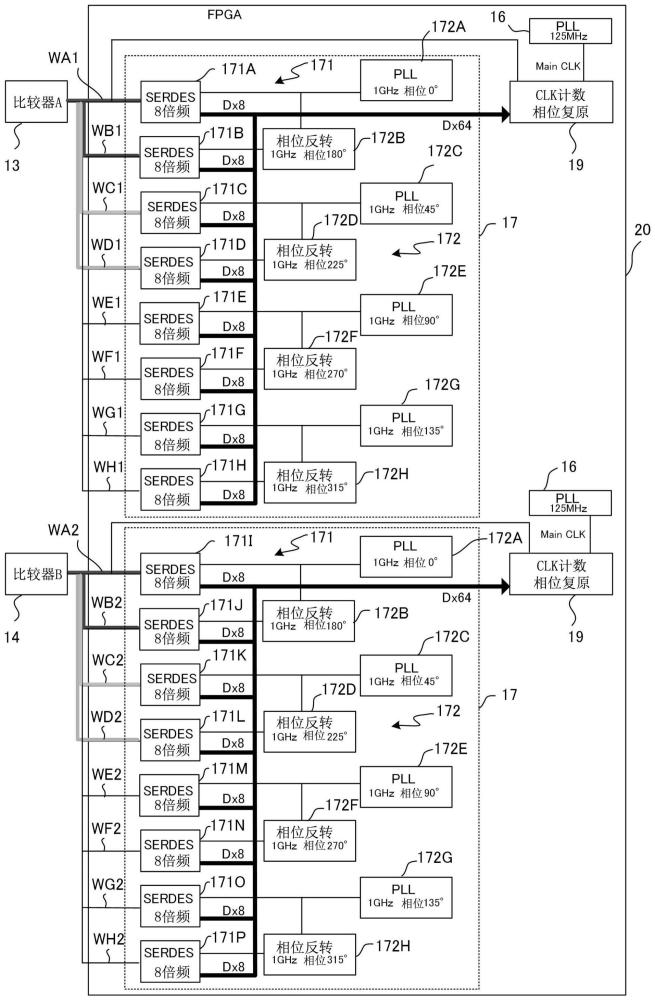

图4是示出本实施方式的零数计数单元的一例的电路块概要图。

图5是示出本实施方式的采样电路的一例的电路块概要图。

图6是本实施方式的零数计数单元中的采样时钟的一例。

图7是拍摄从本实施方式中的信号发生单元起到倍频单元为止的布线的状态而得的图像。

图8是拍摄从本实施方式中的信号发生单元起到倍频单元为止的布线的状态而得的图像。

符号说明

10:时间数字转换器

11:衰减器

12:滤波电路

13:第一信号发生单元

14:第二信号发生单元

15:计数单元

16:基准计数单元

17:零数计数单元

19:计数/转换单元

20:运算单元

171、171A~171H:倍频单元;

172、172A~172H:相位偏移单元

TF、TF1、TF2:零数时间间隔

TM:主时间间隔

具体实施方式

以下,参照附图对本发明的实施方式进行说明。在本实施方式的各附图中标注相同的符号的部分表示相同的部件。

图1是示出本实施方式的时间数字转换器10的概要的图,该图的(A)是示出时间数字转换器10的电路构成的一例的概要框图,该图的(B)是本实施方式的时间数字转换器10中的时间测定的概要图。另外,图2是图1的(B)的局部(比较器A、比较器B的波形)放大图。

参照图1的(A),本实施方式的时间数字转换器10例如具有衰减器11、滤波电路(例如低通滤波器)12、第一信号发生单元13、第二信号发生单元14、以及运算单元20。运算单元20具有计数单元15(基准计数单元16和零数计数单元17)、以及计数/转换单元19等。

参照图1的(B),时间数字转换器10测量经由衰减器11和滤波电路12输入的输入波形中的第一时间点t1与第二时间点t2之间的时间间隔T。本实施方式的时间数字转换器10在例如衰减器11的上游与未图示的DUT(被测定对象,例如半导体元件)(根据需要经由缓冲电路)连接。即,输入波形在该例中是作为被测定对象的半导体元件所输出的例如电压波形。作为该情况下的时间测定的一例,是达到DUT所输出的电压(波形)的va%(例如20%)的第一时间点t1与达到DUT所输出的电压(波形)的vb%(例如80%)的第二时间点t2之间的时间间隔T的测定等。时间数字转换器10与例如其他信息处理装置(例如PC等)一起构成半导体检查装置。

第一时间点t1和第二时间点t2分别是以预定的信号(定时信号、触发信号)的产生为契机的时间点。作为一例,时间数字转换器10具有第一信号发生单元13和第二信号发生单元14,并且预定的信号是通过两个信号发生单元13、14产生的信号。即,第一信号发生单元13是产生成为第一时间点t1的契机的第一信号(定时信号、触发信号)的单元,第二信号发生单元14是产生成为第二时间点t2的契机的第二信号(定时信号、触发信号)的单元。第一信号发生单元13和第二信号发生单元14分别是例如比较器(comparator)A、比较器(comparator)B。

作为一例,第一信号发生单元13对第一参考电压Vref1和输入波形的电压Vin进行比较,在输入波形的电压Vin比第一参考电压Vref1低的情况下输出“L”(截止),如果输入波形的电压Vin比第一参考电压Vref1高则输出作为第一信号的“H”(导通)。第二信号发生单元14对第二参考电压Vref2与输入波形的电压Vin进行比较,在输入波形的电压Vin比第二参考电压Vref2低的情况下输出“L”(截止),如果输入波形的电压Vin比第二参考电压Vref2高则输出作为第二信号的“H”(导通)。即,第一信号(“H”)的输出时刻为第一时间点t1,第二信号(“H”)的输出时刻为第二时间点t2。

在图1的(B)的例子中,第一信号发生单元成为“H”的时刻(第一时间点t1)是测定开始的时刻,第二信号发生单元成为“H”的时刻(第二时间点t2)是测定结束的时刻,从第一时间点t1起到第二时间点t2为止是测定对象的时间间隔T。

计数单元15是基于基准时钟对时间间隔T进行计数的单元,具有基准计数单元16和零数计数单元17。在此,基准时钟例如是基于从晶体振荡器等输入的外部时钟,通过例如相位同步电路(PLL:phase locked loop:PLL电路)等而生成的内部时钟。基准计数单元16是将所生成的基准时钟作为主要的采样时钟Main CLK,将时间间隔T作为该基准时钟的一个周期的整数倍进行计数的单元。具体地,参照图2,基准计数单元16例如将频率125MHz(一个周期8ns)的基准时钟(内部时钟)作为采样时钟Main CLK,对时间间隔T所包含的时钟数(整数)进行计数。在此,任意的时间间隔T并不一定成为采样时钟Main CLK(基准时钟)的一个周期的整数倍的时间。

基准计数单元16例如在时间间隔T的开始时间点与采样时钟Main CLK同步的情况下,将该采样时钟Main CLK设为开始时钟(第1个时钟),在时间间隔T的开始时间点与采样时钟Main CLK不同步的情况下,将在开始时间点以后最初到来的采样时钟Main CLK设为开始时钟(第1个时钟)。另外,在时间间隔T的结束时间点与采样时钟Main CLK同步的情况下,将该采样时钟Main CLK设为结束时钟(第N个时钟,N为整数),在时间间隔T的结束时间点与采样时钟Main CLK不同步的情况下,将在结束时间点以后最初到来的采样时钟Main CLK设为结束时钟(第N个时钟,N为整数)。然后,对时间间隔T所包含的时钟数(N-1个时钟)进行计数,测量与该时钟数对应的时间作为主时间间隔TM。

在图2所示的例子中,第一时间点t1和第二时间点t2均位于采样时钟Main CLK的1个周期的中途,即,时间间隔T的开始时间点(t1)与结束时间点(t2)均与采样时钟Main CLK不同步。在该情况下,基准计数单元16将从开始时钟(在开始时间点以后最初到来的采样时钟Main CLK(第“1”个时钟))起到结束时钟(在结束时间点以后最初到来的采样时钟MainCLK(第“12”个时钟))为止所包含的时钟数(11=12-1)作为时间间隔T所包含的(与主时间间隔TM对应的)采样时钟Main CLK进行计数。

另外,零数计数单元17是对零数时间间隔TF进行计数作为主时间间隔TM相对于时间间隔T的富余量、不足量的单元。即,针对不满采样时钟Main CLK的1个周期的时间(在图2中以阴影所示的零数时间间隔TF),以比采样时钟Main CLK的1个周期短的周期(高分辨率)进行计数。

在图2所示的例子中,如果对测定对象的时间间隔T与主时间间隔TM进行比较,则存在从第一时间点t1起到开始时钟(第1个采样时钟Main CLK)的上升沿为止的时间间隔(测定开始侧的零数时间间隔)TF1、以及从第二时间点t2起到结束时钟(第12个采样时钟Main CLK)的上升沿的时刻为止的时间间隔(测定结束侧的零数时间间隔)TF2。零数计数单元17对与零数时间间隔TF1和零数时间间隔TF2对应的时钟数进行计数,但该情况下的时钟的1个周期是比采样时钟Main CLK的1个周期短的周期,对此将在后面进行描述。

计数/转换单元19基于基准计数单元的计数结果和零数计数单元的计数结果计算出时间间隔,并将其转换为数字值。具体地,时间间隔T通过在主时间间隔TM加上或减去零数时间间隔TF1,并减去或加上(基本上是减去)零数时间间隔TF2而计算出。在该例中,时间间隔T=主时间间隔TM+零数时间间隔TF1-零数时间间隔TF2。另外,计数/转换单元19对计算出的时间间隔T进行数字转换并将其输出。

参照图3至图6,对零数计数单元17进行说明。图3是概略地示出运算单元20的一例的电路框图,图4是概略地示出零数计数单元17的一例的电路框图,图5是概略地示出采样电路170的一例的电路框图,图6是零数计数单元17中的采样时钟Main CLK的一例。

如图3所示,本实施方式的运算单元20包括基准计数单元16、零数计数单元17以及计数/转换单元19,作为一例,由FPGA(field-programmable gate array:现场可编程门阵列)应用构成。在零数计数单元17被输入来自第一信号发生单元13和第二信号发生单元14的数据。零数计数单元17例如是FPGA应用的一个要素,能够执行时钟的分频、倍频、相位偏移等处理。应予说明,这些处理也可以由数字时钟管理器(DCM)构成。

在本实施方式中,零数计数单元17具有由n个(n为2以上的整数)倍频单元171构成的倍频单元组、以及相位偏移单元172。另外,在本实施方式中,第一信号发生单元13和第二信号发生单元14分别与倍频单元组连接。倍频单元组的构成是相同的,因此,以下作为一例,对连接于第一信号发生单元13的倍频单元组(倍频单元171A~171H)进行说明,但对于连接于第二信号发生单元14的倍频单元组(倍频单元171I~171P)也是相同的。

倍频单元组由多个倍频单元171(例如,倍频单元171A~171H)构成,倍频单元171分别由例如SERDES电路(SERializer/DESerializer:串并相互转换电路)构成。倍频单元171生成以基准时钟(采样时钟Main CLK)的m倍频(m为2以上的整数)对从第一信号发生单元13(第二信号发生单元14)输入的信号(与零数时间间隔TF1、TF2对应的数据)进行采样的信号。

另外,n个相位偏移单元172使n个倍频单元171分别生成的倍频采样时钟MCLK的相位逐一偏移360°/n(倍频单元171的数量),例如是包括相位同步电路(PLL电路)的单元。

在此,作为一例,n为8,m也为8(应予说明,n和m也可以不是相同的数)。即,在图3所示的例子中,零数计数单元17具有由8个倍频单元(SERDES电路)171A~171H构成的倍频单元组、以及由8个倍频单元(SERDES电路)171I~171P构成的倍频单元组。各倍频单元171A~171P生成以基准时钟(采样时钟Main CLK)的8倍频对与零数时间间隔TF1、TF2对应的数据进行采样的信号(倍频采样时钟MCLK(参照图2))。

相位偏移单元172使一个倍频单元组(倍频单元171A~171H)分别生成的倍频采样时钟MCLK的相位逐一偏移45°(=360/8°)。相位偏移单元172与倍频单元171A~171H对应地设置,但在本实施方式中,作为一例,通过在4个相位偏移单元(PLL电路)172(172A、172C、172E、172G)分别设置反转电路(未图示)而构成为相位反转电路(相位偏移单元)172B、172D、172F、172H,从而作为使倍频单元171A~171H所生成的倍频采样时钟MCLK的相位偏移的单元。应予说明,也可以不使用相位反转电路,而设置与倍频单元171A~171H对应的8个相位偏移单元(PLL电路)172A~172H。

另外,在图3所示的电路图中,作为一例,在连接于第一信号发生单元13的倍频单元组(倍频单元171A~171H)、以及连接于第二信号发生单元14的倍频单元组(倍频单元171I~171P)中共用相位偏移单元172A~172H、基准计数单元16以及计数/转换单元19。但是,并不限于该构成,也可以与倍频单元组对应地分别设置相位偏移单元172、基准计数单元16以及计数/转换单元19。

参照图4进行具体说明。该图是抽出图3的零数计数单元17(连接于第一信号发生单元13的倍频单元组)进行示出的电路框图。

相位偏移单元172A将倍频单元171A生成的倍频采样时钟MCLK保持为与基准时钟(采样时钟Main CLK)的某一周期的上升沿的时刻(以下,称为基准时刻)相同的相位(相位0°),产生(生成、输出)倍频采样时钟MCLK1。

相位偏移单元172C使倍频单元171C生成的倍频采样时钟MCLK的相位从上述基准时刻偏移45°,产生倍频采样时钟MCLK3。

相位偏移单元172E使倍频单元171E生成的倍频采样时钟MCLK的相位从基准时刻偏移90°,产生倍频采样时钟MCLK5。

相位偏移单元172G使倍频单元171G生成的倍频采样时钟MCLK的相位从基准时刻偏移135°,产生倍频采样时钟MCLK7。

相位偏移单元172B使倍频单元171B生成的倍频采样时钟MCLK的相位偏移。在该例中,相位偏移单元172B利用反转电路(未图示)使相位偏移单元172A的输出反转180°,由此产生相位从基准时刻偏移180°而得的倍频采样时钟MCLK2。

相位偏移单元172D使倍频单元171D生成的倍频采样时钟MCLK的相位偏移。在该例中,相位偏移单元172D利用反转电路(未图示)使相位偏移单元172C的输出反转180°,由此产生相位从基准时刻偏移225°而得的倍频采样时钟MCLK4。

相位偏移单元172F使倍频单元171F生成的倍频采样时钟MCLK的相位偏移。在该例中,相位偏移单元172F利用反转电路(未图示)使相位偏移单元172E的输出反转180°,由此产生相位从基准时刻偏移270°而得的倍频采样时钟MCLK6。

相位偏移单元172H使倍频单元171H生成的倍频采样时钟MCLK的相位偏移。在该例中,相位偏移单元172H利用反转电路(未图示)使相位偏移单元172G的输出反转180°,由此产生相位从基准时刻偏移315°而得的倍频采样时钟MCLK8。

如此,一组倍频单元171和相位偏移单元172构成采样电路170,零数计数单元17具有多个(在此为8个)采样电路170A~170H。

图5是示出采样电路170(例如,由倍频单元171A和相位偏移单元172A构成的采样电路170A)的构成的一例的概略框图。

倍频单元171(例如,倍频单元171A)具有接收电路(例如,触发电路)201、1/m分频器202、以及1:m解复用器(Demux)203。m如上所述为倍频数(倍频率,在此,作为一例,m=8)。另外,相位偏移单元172(例如,相位偏移单元172A)具有对输入信号进行倍频处理的PLL电路204和相位调整器205。

在相位偏移单元172中,接收外部时钟CLK(在此为例如50MHz的晶体振荡器的时钟)的输入,在PLL路径204中将其倍频为例如20倍,从而产生1GHz的时钟RCLK。另外,相位调整器205生成使时钟RCLK的相位从基准时刻逐一偏移(延迟)360°/n(在此n=8)而得的倍频采样时钟MCLK,并将其输出到倍频单元171的接收电路201。

在此,将相位偏移单元172A从基准时刻起算的相位的偏移量设为0°,其他相位偏移单元172B~172H从基准时刻逐一偏移45°(=360°/8)。

倍频单元171的接收电路201接收来自比较器(比较器A或比较器B)的输入数据Din(与基于第一信号或第二信号的零数时间间隔TF对应的数据),并以使其与1GHz的倍频采样时钟MCLK同步的方式逐比特地将与倍频率(在此为8)相对应的比特数(在此为8比特)的串行数据信号发送至Demux203。即,在该情况下,以1GHz的周期对输入数据Din进行采样。

1/n(以下为1/8)分频器202以倍频率的倒数(1/8)对相位调整器205所生成的倍频采样时钟MCLK(1GHz)进行分频而生成分频时钟(125MHz)。另外,该频率(125MHz)成为内部时钟(采样时钟Main CLK)。

在Demux203中,基于接收电路201所输出的串行数据信号、以及分频时钟(125MHz),将串行数据信号转换为8比特的并行数据信号,并将其与分频时钟同步地作为8比特的并行数据信号Dout输出。即,来自Demux203的输出相对于Din的1个输入成为倍频(8倍)的数据数。

在各采样电路170中,通过相位调整器205将相位偏移后的倍频采样时钟MCLK、作为Demux203的输出的并行数据信号Dout、经1/8分频后的125MHz的分频时钟(采样时钟MainCLK)均是从1GHz的时钟RCLK生成的,且均为相同的相位。

另外,在各采样电路170(170A~170H)中,基于相位调整器205的相位偏移量(相位变化率)为360°/n,该情况下的n是向接收电路201的输入数量。对于相位调整器205而言,需要与该输入数量或该输入数量/2(使用反转电路的情况)相当的数量。

通过这样的构成,在本实施方式的零数计数单元17中,得到由以下的式1所示的采样数(分辨率)。

采样数(分辨率)=

基准时钟(采样时钟Main CLK)的倒数/(倍频单元171的数量(输入数量)×倍频数)(式1)

具体地,在本实施方式的例子中,分辨率=(1/125MHz)/(8×8)=125ps。

其结果是,如图6所示,在零数计数单元17中,能够测定通过将采样时钟Main CLK(125MHz、分辨率1个周期8ns)模拟地(表观上)进行64倍频而得的(1GHz、分辨率1个周期125ps)的倍频采样时钟MCLK1~MCLK8所输入的零数时间间隔TF(基于第一信号和第二信号的信号),能够进行高分辨率的采样。

即,基于图2所示的第一信号的产生的零数时间间隔TF1(相当于该零数时间间隔TF1的时钟数)通过该倍频采样时钟MCLK1~MCLK8进行计数,基于第二信号的产生的零数时间间隔TF2(相当于该零数时间间隔TF2的时钟数)同样地通过零数计数单元17的倍频采样时钟MCLK1~MCLK8进行计数。

在计数/转换单元19中,运算相当于主时间间隔TM的时钟数以及相当于零数时间间隔TF1、TF2的时钟数来计算时间间隔T。在该例中,时间间隔T=主时间间隔TM+零数时间间隔TF1-零数时间间隔TF2(参照图2)。另外,计数/转换单元19对所计算出的时间间隔T进行数字转换并将其输出。

应予说明,虽然省略详细的图示,但是例如使相位偏移而采样得到的数据(以相位45°~315°的倍频采样时钟MCLK1~MCLK8获取的数据)例如在计数/转换单元19中基于采样时钟Main CLK(125MHz)全部调整(复原)为相同相位(相位0°),并在经排列(进行顺序的重新排列)的基础上进行运算。

如此,在本实施方式中,通过设置n个(在该例中为8个)能够产生对基准时钟(采样时钟Main CLK)进行m倍频(例如8倍频)的倍频采样时钟的倍频单元171,从而能够在表观上对例如125MHz(1个周期8ns)的采样时钟Main CLK进行64倍频,成为125ps的倍频采样时钟。由此,能够以高分辨率(高精度)对零数时间间隔TF1、TF2进行计数,从而能够提供适合用于进行DUT的时间测量的半导体检查装置的时间数字转换器10。

另外,运算单元20(倍频单元171、相位偏移单元172、计数/转换单元19等)能够由FPGA构成,因此不需要ASIC模拟电路设计就能够抑制成本并实现高分辨率(高精度)化。另外,以往,虽然能够通过使用示波器和PC(个人计算机),从而进行高精度、高分辨率的测定,但是高速处理存在限度。根据本实施方式,能够由FPGA构成运算单元20,因此,除了高分辨率(高精度)化以外,还能够进行高速处理。

在此,与第一信号发生单元13连接的倍频单元组(倍频单元171A~171H)的构成和与第二信号发生单元14连接的倍频单元组(171I~171P)的构成相同,在各倍频单元组中,在与生成相同相位的倍频采样时钟MCLK的倍频单元171连接的情况下,各布线成为等长。

具体地,第一信号发生单元13通过第一布线WA1与倍频单元171A(相位偏移0°)连接,第二信号发生单元14通过第二布线WA2与倍频单元171I(相位偏移0°)连接。而且,第一布线WA1与第二布线WA2等长。在此,在本实施方式中,布线“等长”是指多个布线(例如,第一布线WA1和第二布线WA2)作为设计上的长度相等,且实质上(大致)相等的长度(虽然存在包含设计上的误差的情况,但并未有意地改变长度)。

同样地,第一信号发生单元13通过第一布线WB1与倍频单元171B(相位偏移180°)连接,第二信号发生单元14通过第二布线WB2与倍频单元171J(相位偏移180°)连接。而且,第一布线WB1与第二布线WB2等长。

另外,第一信号发生单元13通过第一布线WC1与倍频单元171C(相位偏移45°)连接,第二信号发生单元14通过第二布线WC2与倍频单元171K(相位偏移45°)连接。而且,第一布线WC1与第二布线WC2等长。

另外,第一信号发生单元13通过第一布线WD1与倍频单元171D(相位偏移225°)连接,第二信号发生单元14通过第二布线WD2与倍频单元171L(相位偏移225°)连接。而且,第一布线WD1与第二布线WD2等长。

另外,第一信号发生单元13通过第一布线WE1与倍频单元171E(相位偏移90°)连接,第二信号发生单元14通过第二布线WE2与倍频单元171M(相位偏移90°)连接。而且,第一布线WE1和第二布线WE2等长。

另外,第一信号发生单元13通过第一布线WF1与倍频单元171F(相位偏移270°)连接,第二信号发生单元14通过第二布线WF2与倍频单元171N(相位偏移270°)连接。而且,第一布线WF1与第二布线WF2等长。

另外,第一信号发生单元13通过第一布线WG1与倍频单元171G(相位偏移135°)连接,第二信号发生单元14通过第二布线WG2与倍频单元171O(相位偏移135°)连接。而且,第一布线WG1和第二布线WG2等长。

另外,第一信号发生单元13通过第一布线WH1与倍频单元171H(相位偏移315°)连接,第二信号发生单元14通过第二布线WH2与倍频单元171P(相位偏移315°)连接。而且,第一布线WH1和第二布线WH2等长。

图7和图8是拍摄从第一信号发生单元13和第二信号发生单元14起到倍频单元171为止的实际的布线的状态而得的图像,例如图7的(A)是示出倍频单元171A、171I附近的第一布线WA1和第二布线WA2的图像,该图7的(B)是示出倍频单元171B、171J附近的第一布线WB1和第二布线WB2的图像,图8的(A)是示出倍频单元171C、171K附近的第一布线WC1和第二布线WC2的图像,该图8的(B)是示出倍频单元171D、171L附近的第一布线WD1和第二布线WD2的图像。应予说明,如上所述,倍频单元171A~171D、171I~171L例如组装于FPGA。

由此,在测定开始侧的零数时间间隔TF1和测定结束侧的零数时间间隔TF2的计数时,直到成为相同相位的倍频采样时钟的生成单元(倍频单元171)为止的布线长度相等。即,在进行以第一信号发生单元13所输出的第一信号和第二信号发生单元14所输出的第二信号为契机的时间测定时,能够避免由布线长度的不同所引起的信号延迟。

在本实施方式中,通过在表观上将采样时钟Main CLK进行64倍频,从而能够进行1个周期125ps的采样。另一方面,测定对象的时间间隔T是以第一信号为契机的时刻与以第二信号为契机的时刻之间的时间(因为使用两个信号),第一信号和/或第二信号的输入的延迟在皮秒量级的测定中成为致命的问题。

具体地,例如,如果第一布线WA1和第二布线WA2的布线长度不同,则在向倍频单元171A输入的第一信号和/或第二信号中产生非有意的时刻的偏差(在极端的例子中,第一信号和第二信号的到达的时刻反转等),无法进行准确的时间测定。

在本实施方式中,由于第一信号和第二信号以相同的布线长度输入至产生相同相位的倍频采样时钟的倍频单元组(171A~171H、171I~171P),因此在硬件上也没有误差,能够保证时间的绝对精度。更详细地说,通过进行等长布线,从而能够进行基准时钟的1个周期以下的长度的时间测定,能够将时间延迟(时间测定)的误差抑制为最小分辨率以下。具体而言,虽然误差因基准时钟频率和/或倍频数而变化,但是在本实施方式中,通过进行等长布线,从而能够将测定误差抑制为最小分辨率即125ps以下(1个周期8ns的情况)。

另外,相位偏移单元172、计数/转换单元19在第一信号发生单元13和第二信号发生单元14中共用(使用同一单元(电路)),因此,能够有助于装置的小型化、低成本化,也能够避免电路的性能偏差,能够进行高精度的测定。

以上,对本实施方式的时间数字转换器10进行了说明,但信号发生单元也可以是单个。即,也可以以一个信号发生单元的信号(第一信号)的上升沿和下降沿的时刻为契机,测量两时刻之间的时间。另外,信号发生单元的数量也可以是3个以上(例如4个)。

另外,在上述实施方式中例示了输入波形为一个的情况,但输入波形也可以为多个。例如,也可以是第一信号是确定输入波形a的某一时刻(例如,成为输入电压a的50%的第一时间点t1等)的信号,第二信号是确定输入波形b的某一时刻(例如,成为输入电压b的50%的第二时间点t2等)的信号,并且测定第一时间点t1与第二时间点t2之间的时间间隔T的装置。

另外,第一信号和/或第二信号可以是以上升沿为契机的信号,也可以是以下降沿为契机的信号。如此,本实施方式能够不依赖于时间的测定方法而进行应用。

另外,在上述例子中,示出了第一信号发生单元13和第二信号发生单元14所连接的相位偏移单元172和计数/转换单元19等被共用的构成,但相位偏移单元172也可以分别设置于第一信号发生单元13和第二信号发生单元14。

另外,在上述实施方式中,示例了计数单元15具有基准计数单元16和零数计数单元17,通过零数计数单元17将零数时间间隔TF作为由基准计数单元16计数而得的主时间间隔TM的富余量、不足量而进行计数的构成。但是并不限于此,也可以是通过零数计数单元17进行应测量的时间间隔T的全部期间中的计数(在全部期间中进行高分辨率的计数)的构成。在该情况下,为了防止由基于零数计数单元17的高灵敏度(高分辨率)测定所引起的、第一信号发生单元13(第二信号发生单元14也同样)的第一参考电压Vref1附近的噪声所引起的误动作,优选调整第一信号发生单元13的灵敏度。另一方面,如上述实施方式那样,作为计数单元15,通过并用基准计数单元16和零数计数单元17,从而能够节约FPGA的容量。

另外,例如也可以对输入电压从0%上升的某一时刻(例如成为50%的定时)与从100%下降的某一时刻(例如成为50%的定时)之间的频率进行计数(作为频率计数器使用)。

另外,在上述实施方式中,示例了连接于第一信号发生单元13的倍频单元组(倍频单元171A~171H)和连接于第二信号发生单元14的倍频单元组(倍频单元171I~171P)是不同的倍频单元组的情况,但它们也可以共用一个倍频单元组。

另外,本发明的时间数字转换器10并不限于上述实施方式,并且显然能够在不脱离本发明的主旨的范围内施加各种变更。

工业上的可利用性

本发明的时间数字转换器例如能够在半导体检查装置的领域中利用。