半导体结构

文献发布时间:2023-06-19 09:44:49

技术领域

本公开主张2019/07/24申请的美国正式申请案第16/520,623号的优先权及益处,该美国正式申请案的内容以全文引用的方式并入本文中。

本公开涉及一种半导体结构。特别涉及一种具有设置在二穿基底通孔(through-substrate vias,TSVs)之间的遮蔽层的半导体结构。

背景技术

半导体产业通过持续缩减元件的最小尺寸,以持续改善各式电子组件(例如晶体管、二极管、电阻器、电容器等等)的集成密度(integration density),其是允许更多的组件整合到一给定区域。为了达到所述半导体组件的紧密整合与最小化,也提升了封装结构的需求。

在半导体晶粒中的多个元件可造成电噪声(electrical noise)与电磁干扰(electromagnetic interference)。包括射频(radio frequency)元件的噪声源(noisysources)产生搭载在多个导体结构中的信号内的电噪声。在所述多个导体结构中的电噪声影响在封装中的其他信号及所述多个元件。在半导体封装中,将这些噪声电子信号最小化是重要的课题,使高集成密度(high integration density)成为可能。

上文的“现有技术”说明仅是提供背景技术,并未承认上文的“现有技术”说明公开本公开的标的,不构成本公开的现有技术,且上文的“现有技术”的任何说明均不应作为本公开的任一部分。

发明内容

本公开的一实施例提供一种半导体结构。该半导体结构包括一基底、至少一半导体元件、一第一穿基底通孔(first through-substrate via,TSV)、一隔离层(insulatinglayer)、一遮蔽层(shielding layer)以及一第二穿基底通孔。该基底具有一前表面与一后表面。该半导体元件设置在该基底的一元件区中。该第一穿基底通孔设置在该基底中,其中该第一穿基底通孔通过该基底的该前表面与该后表面而暴露。该隔离层围绕该第一穿基底通孔设置,其中该隔离层包含一电性隔离材料(electrically insulating material)。该遮蔽层围绕该隔离层设置,其中该遮蔽层包含一电性导电材料(electrically conductivematerial),并经由一接地层而接地。该第二穿基底通孔邻近该第一穿基底通孔设置,其中该第二穿基底通孔通过该基底的该前表面与该后表面而暴露。

依据本公开的一些实施例,该第一穿基底通孔与该第二穿基底通孔包括一大致呈圆柱型形状,且该遮蔽层在该第一穿基底通孔周围设置。

依据本公开的一些实施例,该第一穿基底通孔与该第二穿基底通孔之间的一距离,在该第一穿基底通孔的一半径的1.5到2倍之间。

依据本公开的一些实施例,该第一穿基底通孔与该第二穿基底通孔之间的一距离,在7.5μm到10μm之间。

依据本公开的一些实施例,该基底接触该遮蔽层的一底表面。

依据本公开的一些实施例,该接地层设置在该基底的一重布层(redistributionlayer)中。

依据本公开的一些实施例,该接地层设置在该基底的该元件区中。

本公开的另一实施例提供一种半导体结构。该半导体结构包括一基底、至少一半导体元件、一第一穿基底通孔、一隔离层、一遮蔽层以及一第二穿基底通孔。该基底具有一前表面与一后表面。该半导体元件设置在该基底的一元件区中。该第一穿基底通孔设置在该基底中,其中该第一穿基底通孔通过该基底的该前表面与该后表面而暴露。该隔离层围绕该第一穿基底通孔设置,其中该隔离层包含一电性隔离材料。该遮蔽层围绕该隔离层设置,其中该遮蔽层包含一电性导电材料,并经由位在该基底的该前表面上的一第一接触垫(first contact pad)而接地。该第二穿基底通孔邻近该第一穿基底通孔设置,其中该第二穿基底通孔通过该基底的该前表面与该后表面而暴露。

依据本公开的一些实施例,该第一穿基底通孔与该第二穿基底通孔包括一大致呈圆柱型形状,且该遮蔽层在该第一穿基底通孔周围设置。

依据本公开的一些实施例,该第一穿基底通孔与该第二穿基底通孔之间的一距离,在该第一穿基底通孔的一半径的1.5到2倍之间。

依据本公开的一些实施例,该第一穿基底通孔与该第二穿基底通孔之间的一距离,在7.5μm到10μm之间。

依据本公开的一些实施例,该半导体结构还包括一第一电路层(first circuitlayer),设置在该基底的该前表面上的该第一接触垫与该遮蔽层之间。

依据本公开的一些实施例,该第一电路层电性连接该基底的该前表面上的该第一接触垫。

依据本公开的一些实施例,该基底接触该遮蔽层的一底表面。

本公开的另一实施例提供一种半导体结构。该半导体结构包括一基底、至少一半导体元件、一第一穿基底通孔、一隔离层、一遮蔽层以及一第二穿基底通孔。该基底具有一前表面与一后表面。该半导体元件设置在该基底的一元件区中。该第一穿基底通孔设置在该基底中,其中该第一穿基底通孔通过该基底的该前表面与该后表面而暴露。该隔离层围绕该第一穿基底通孔设置,其中该隔离层包含一电性隔离材料。该遮蔽层设置在该隔离层上方,其中该遮蔽层包含一电性导电材料,并经由位在该基底的该后表面下方的一第二接触垫而接地。该第二穿基底通孔邻近该第一穿基底通孔设置,其中该第二穿基底通孔通过该基底的该前表面与该后表面而暴露。

依据本公开的一些实施例,该第一穿基底通孔与该第二穿基底通孔包括一大致呈圆柱型形状,且该遮蔽层在该第一穿基底通孔周围设置。

依据本公开的一些实施例,该第一穿基底通孔与该第二穿基底通孔之间的一距离,在该第一穿基底通孔的一半径的1.5到2倍之间。

依据本公开的一些实施例,该第一穿基底通孔与该第二穿基底通孔之间的一距离,在7.5μm到10μm之间。

依据本公开的一些实施例,该半导体结构还包括一第二电路层,设置在该基底的该后表面下方的该第二接触垫与该遮蔽层之间,其中该第二电路层电性连接该基底的该后表面下方的该第二接触垫。

依据本公开的一些实施例,该基底接触该遮蔽层的一底表面。

在本公开中,在该半导体结构中的该遮蔽层可通过射线信号(radiation signal)的耗散能量,以将该射线信号驱动至接地,和避免由该射线信号所造成的该第一穿基底通孔内的一信号的引诱(inducement)一样。由于避免该射线信号到该第一穿基底通孔中的传输,因此该遮蔽层可降低或减缓在该第一穿基底通孔中的噪声所导致的射线。通过避免从该第一穿基底通孔的射线信号传输,该遮蔽层亦降低或减缓由该第一穿基底通孔所造成的由噪声所导致的射线。由于该遮蔽层的噪声与串扰(crosstalk)最小化特性,因此可缩减该第一穿基底通孔与该第二穿基底通孔之间的该距离,并允许在该半导体结构中的所述多个零件的紧密整合(compact integration)。

上文已相当广泛地概述本公开的技术特征及优点,从而使下文的本公开详细描述得以获得较佳了解。构成本公开的权利要求标的的其它技术特征及优点将描述于下文。本公开所属技术领域中技术人员应了解,可相当容易地利用下文公开的概念与特定实施例可作为修改或设计其它结构或制程而实现与本公开相同的目的。本公开所属技术领域中技术人员亦应了解,这类等效建构无法脱离后附的权利要求权利要求所界定的本公开的精神和范围。

附图说明

参阅实施方式与权利要求合并考量附图时,可得以更全面了解本公开的公开内容,附图中相同的元件符号是指相同的元件。

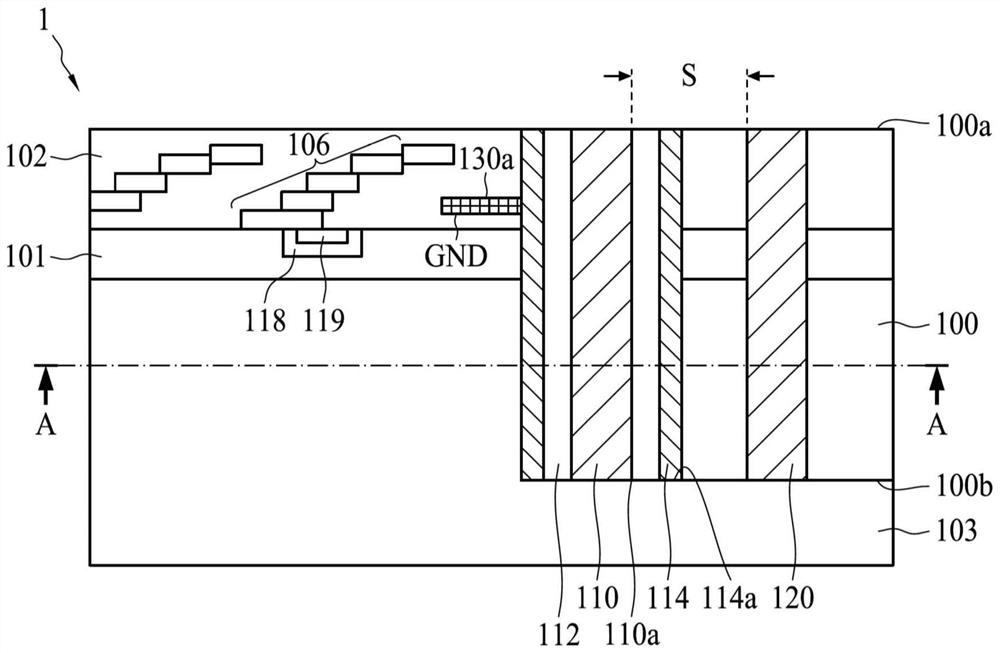

图1为依据本公开一些实施例的一种半导体结构的剖视示意图。

图2为依据本公开一些实施例的一种半导体结构沿剖线A-A的顶视示意图。

图3为依据本公开另一些实施例的一种半导体结构沿剖线A-A的顶视示意图。

图4为依据本公开一些实施例的一种半导体结构的剖视示意图。

图5为依据本公开一些实施例的一种半导体结构的剖视示意图。

图6为依据本公开一些实施例的一种半导体结构的剖视示意图。

附图标记说明:

1 半导体结构

100 基底

100a 前表面

100b 后表面

101 元件区

102 重布层

103 封装基底

106 金属与通孔层

110 第一穿基底通孔

110a 外表面

112 隔离层

114 遮蔽层

114a 底表面

118 半导体晶粒

119 半导体元件

120 第二穿基底通孔

130a 接地层

130b 接地层

141 第一电路层

142 第一接触垫

151 第二电路层

152 第二接触垫

2 半导体结构

3 半导体结构

4 半导体结构

GND 接地

R 半径

S 距离

具体实施方式

本公开的以下说明伴随并入且组成说明书的一部分的附图,说明本公开的实施例,然而本公开并不受限于该实施例。此外,以下的实施例可适当整合以下实施例以完成另一实施例。

“一实施例”、“实施例”、“例示实施例”、“其他实施例”、“另一实施例”等是指本公开所描述的实施例可包含特定特征、结构或是特性,然而并非每一实施例必须包含该特定特征、结构或是特性。再者,重复使用“在实施例中”一语并非必须指相同实施例,然而可为相同实施例。

其将理解的是,虽然用语“第一(first)”、“第二(second)”、“第三(third)”等可用于本文中以描述不同的元件、部件、区域、层及/或部分,但是这些元件、部件、区域、层及/或部分不应受这些用语所限制。这些用语仅用于从另一元件、部件、区域、层或部分中区分一个元件、部件、区域、层或部分。因此,以下所讨论的“第一元件(firstelement)”、“部件(component)”、“区域(region)”、“层(layer)”或“部分(section)”可以被称为第二元件、部件、区域、层或部分,而不背离本文所教示。

本文中使用的术语仅是为了实现描述特定实施例的目的,而非意欲限制本发明。如本文中所使用,单数形式“一(a)”、“一(an)”,及“该(the)”意欲亦包括多个形式,除非上下文中另作明确指示。将进一步理解,当术语“包括(comprises)”及/或“包括(comprising)”用于本说明书中时,这些术语规定所陈述的特征、整数、步骤、操作、元件,及/或组件的存在,但不排除存在或增添一或更多个其他特征、整数、步骤、操作、元件、组件,及/或上述各者的群组。

图1为依据本公开一些实施例的一种半导体结构1的剖视示意图。请参考图1,在一些实施例中,半导体结构1包括一基底100、至少一半导体元件119、一第一穿基底通孔(TSV)110、一隔离层112、一遮蔽层114以及一第二穿基底通孔120。第一穿基底通孔110设置在基底100中,隔离层112围绕第一穿基底通孔110设置,遮蔽层114围绕隔离层112设置,第二穿基底通孔120邻进第一穿基底通孔110设置。半导体结构1还可包括一元件区(deviceregion)101、一重布层(redistribution layer)102以及一封装基底(package substrate)103。重布层102设置在元件区101上。在一些实施例中,基底100具有一前表面100a以及一后表面100b。半导体元件119设置在基底100的元件区101中。再者,半导体元件119可为一主动元件(active device),其是可包含在一半导体晶粒118中,而半导体晶粒118电性连接重布层102的多个金属与通孔层(metal and via layers)106。举例来说,半导体元件119可为一电子熔丝(electrical fuse)、一二极管、一可变电容二极管、一闸流器(thyristor)、一场效晶体管、一双极性晶体管(bipolar transistor),或其他所属技术领域中所熟知的半导体元件种类,其是产生及/或敏感于所接收的射线传输。举例来说,所述多个金属与通孔层106可为多个金属层(metal layers)与多个通孔层(via layers)交错在重布层102中。封装基底103可通过设置在基底100与封装基底103之间的多个锡球(图未示)而贴合到基底100。再者,封装基底103亦可包括多个额外的内连接(interconnect)或重布线层(图未示)。

在一些实施例中,第一穿基底通孔100通过基底100的前表面100a与后表面100b而暴露。隔离层112包含一电性隔离材料,例如聚亚酰胺(polyimide)材料。在一些实施例中,隔离层112在第一穿基底通孔110的纵向长度周围延伸,且隔离层112并未在基底100的前表面100a与后表面100b上方延伸。举例来说,隔离层112可为一内扇出晶圆级层(inter fan-out wafer-level layer),其是通过所属技术领域中所熟知的扇出晶圆级封装技术所制造。在一些实施例中,第一穿基底通孔110经由隔离层112而延伸,并可与形成在第一穿基底通孔110的两端的所述多个通孔(图未示)相互耦接。在一些实施例中,第一穿基底通孔110与第二穿基底通孔120具有一大致呈圆柱型形状,其是沿一纵轴延伸。依据一些实施例,第二穿基底通孔120可邻近第一穿基底通孔110设置,且第二穿基底通孔120可通过基底100的前表面100a与后表面100b而暴露。第二穿基底通孔120可与形成在第二穿基底通孔120的两端的所述多个通孔(图未示)相互耦接。

在一些实施例中,遮蔽层114包含一电性导电材料,并经由一接地层(groundlayer)130a而接地GND。在一些实施例中,基底100接触遮蔽层114的一底表面114a。遮蔽层114通过隔离层112而与第一穿基底通孔110电性隔离。在一些实施例中,接地层130a可连接半导体结构1的重布层102中的其他零件(elements)。在一些实施例中,遮蔽层114避免射线信号传输到第一穿基底通孔110或是避免射线信号从第一穿基底通孔110传输。遮蔽层114亦可使第一穿基底通孔110与射线信号隔离,所述多个射线信号是从半导体元件119所产生。举例来说,当一射线信号产生在第一穿基底通孔110附近时,则在到达第一穿基底通孔110之前,射线信号即遭遇遮蔽层114。遮蔽层114能通过射线信号的耗散能量,将该射线信号通过接地层130a而驱动到接地GND,和避免由射线信号所造成的第一穿基底通孔110内的一信号的引诱一样。据此,由于避免射线信号到第一穿基底通孔110的传输,因此遮蔽层114能降低或减缓在第一穿基底通孔110中的由噪声所导致的射线。通过避免从第一穿基底通孔110的射线信号传输,遮蔽层114亦降低或减缓由第一穿基底通孔110所造成的由噪声所导致的射线。由于遮蔽层114的噪声与串扰(crosstalk)最小化特性,因此可缩减第一穿基底通孔110与第二穿基底通孔120之间的一距离S,其是导致在半导体结构1中的所述多个零件的紧密整合。

在一些实施例中,遮蔽层114完全地包围第一穿基底通孔110的一外表面110a。在其他实施例中,遮蔽层114可设置在基底100上方及/或下方的多层(layers)中。如图1所示,依据一些实施例,遮蔽层114延伸到重布层102中,其是可当作限制所述多个金属与通孔层106的所述多个零件之间的射线传输。所属技术领域中技术人员应可理解,遮蔽层114的架构可依据半导体结构1的应用而加以改良。举例来说,在一些实施例中,遮蔽层114可均延伸到封装结构102与重布层102中。在一些实施例中,依据半导体结构1的应用,第一穿基底通孔110与遮蔽层114沿着该纵轴的长度可相互不同。在其他实施例中,第一穿基底通孔110与遮蔽层114沿着该纵轴的长度可相同。再者,遮蔽层114可通过多个额外的内扇出隔离层(图未示)而被隔离,所述多个内扇出隔离层可隔离遮蔽层114与围绕的多个封装零件(packageelements)。在一些实施例中,遮蔽层114的底表面114a可包括一介电层(图未示),其是由氧化硅、二氧化硅、氮氧化硅,或其组合所制。在一些实施例中,第一穿基底通孔110、遮蔽层114以及第二穿基底通孔120可由相同的电性导电材料所制,举例来说,例如铜。然而,本公开的实施例并不以此为限。所属技术领域中技术人员能对第一穿基底通孔110、遮蔽层114以及第二穿基底通孔120进行改良,和半导体结构1的其他零件取决于实际应用一样。

图2为依据本公开一些实施例的一种半导体结构1沿剖线A-A的顶视示意图。图3为依据本公开另一些实施例的一种半导体结构1沿剖线A-A的顶视示意图。请参考图2,描述第一穿基底通孔110与第二穿基底通孔120的架构。在如图2所示的架构中,第一穿基底通孔110与第二穿基底通孔120之间的距离S,大致等于第一穿基底通孔110的半径R(radius)的两倍。在一些实施例中,依据半导体结构1的应用,设置在第一穿基底通孔110周围的遮蔽层114可使第一穿基底通孔110与第二穿基底通孔120之间的距离S的缩减成为可能,如图3所示。请参考图3,描述第一穿基底通孔110与第二穿基底通孔120在其间具有一缩减空间。在图3所示的架构中,第一穿基底通孔110与第二穿基底通孔120之间的距离S,大致等于第一穿基底通孔110的半径R的1.5倍。在一些实施例中,第一穿基底通孔110与第二穿基底通孔120之间的距离S,可在第一穿基底通孔110的半径R的1.5到2倍之间。在一些实施例中,第一穿基底通孔110与第二穿基底通孔120之间的距离S,可在7.5μm到10μm之间。遮蔽层114的噪声与串扰最小化特性允许缩减第一穿基底通孔110与第二穿基底通孔120之间的距离S,导致在半导体结构1中的所述多个零件的紧密整合。当不存在包围第一穿基底通孔110的遮蔽层114时,由于遮蔽层114的噪声与串扰最小化特性需要用于在半导体结构1中的所述多个零件的紧密整合,因此第一穿基底通孔110与第二穿基底通孔120之间的距离S可需要增加到第一穿基底通孔110的半径R的两倍。

所属技术领域中技术人员应可理解,在一些实施例中,虽然第一穿基底通孔110与第二穿基底通孔120的半径显示大致等于如图2及图3所示,但是第一穿基底通孔110与第二穿基底通孔120的半径可依据半导体结构1的应用而改良成相互不同。理应注意的是,邻近第一穿基底通孔110设置的第二穿基底通孔120的数量,并不受如图2及图3所示的架构所限制。

虽然接地层130a设置在如图1所描述的半导体结构1的重布层102中,但在一些实施例中,将第一穿基底通孔110的遮蔽层114耦接到接地GND的接地层130a可设置在半导体结构1的不同区域中。图4为依据本公开一些实施例的一种半导体结构2的剖视示意图。请参考图4,半导体结构2类似于图1的半导体结构1,除了一接地层130b设置在基底100的元件区101中之外。如图4所示,由于接地层130b设置在半导体元件119周围的元件区101中,因此将遮蔽层114耦接到接地GND的接地层130b能将半导体元件119与所述多个传输及/或接受的射线信号隔离。在一些实施例中,举例来说,当半导体元件119为一射频发射元件(radiofrequency(RF)emitting device)时,将遮蔽层114耦接到接地GND的接地层130b可避免射频信号传输不会使半导体元件119干扰半导体结构2的其他零件。在一些实施例中,接地层130b可连接半导体结构2的元件区101中的其他零件。半导体元件119亦可包括任何适合的主动半导体元件,其是产生及/或敏感于接收射线传输。

图5为依据本公开一些实施例的一种半导体结构3的剖视示意图。请参考图5,半导体结构5类似于图1的半导体结构1,除了遮蔽层114经由基底100的前表面100a上的一第一接触垫142而耦接接地GND之外。在一些实施例中,半导体结构3还包括一第一电路层141,设置在第一接触垫142与遮蔽层114之间。在一些实施例中,第一电路层141电性连接基底100的前表面100a上的第一接触垫142,且第一接触垫142连接接地GND。举例来说,电路层141的线距(line pitch)可大于1μm,虽然本公开的实施例并不以此为限。图6为依据本公开一些实施例的一种半导体结构4的剖视示意图。请参考图6,半导体结构4类似于图1的半导体结构1,除了遮蔽层114经由基底100的后表面100b下方的一第二接触垫152而耦接到接地GND之外。在一些实施例中,半导体结构4还包括一第二电路层151,设置在第二接触垫152与遮蔽层114之间。在一些实施例中,第二电路层151电性连接基底100的后表面100b下方的第二接触垫152,且第二接触垫152连接接地GND。举例来说,电路层151的线距可大于1μm,虽然本公开的实施例并不以此为限。在图5与图6所描述的半导体结构3、4可依据实际应用而由所属技术领域中技术人员进行改良。

本公开的半导体结构可通过所属技术领域中技术人员所熟知的任何适合的技术所制造。举例来说,第一穿基底通孔110、遮蔽层114以及第二穿基底通孔120可通过使用反应离子(reactive ion)蚀刻制程及/或传统蚀刻制程在基底100中形成多个沟槽(trenches)所制造,和传统镀覆(plating)制程一样。半导体元件119、元件区101、重布层102、所述多个电路层141与151以及所述多个接触垫142与152,可使用适合的蚀刻及沉积制程所形成。可在基底100的前表面100a与后表面100b上执行化学机械平坦化(chemicalmechanical planarization,CMP)制程,以移除多余材料。理应注意的是,基底100可包含任何适合的材料,包括Si、SiC、SiGe、SiGeC、GaAs、InP、InAs或其他II-VI或III-V族化合物半导体,但并不以此为限。在一些实施例中,本公开的所述多个半导体结构可包括额外的多个内连接结构(interconnection structures)(图未示)以及一或多个层间介电质,所述多个内连接结构包含交错堆叠的多个线路层(wiring layers)与通孔(vias)(图未示),而所述多个层间介电质包围所述多个线路层与所述多个通孔设置。举例来说,基底100可包括一半导体晶圆、半导体芯片,或晶圆部分。理应注意的是,基底100亦可为所属技术领域中技术人员所熟知的其他任何不同结构,包括以陶瓷或有机物为主的基底,但并不以此为限。

据此,遮蔽层114可通过射线信号的耗散能量,以将射线信号驱动至接地GND,和避免由射线信号所造成的第一穿基底通孔110内的一信号的引诱一样。由于避免射线信号到第一穿基底通孔110中的传输,因此遮蔽层114可降低或减缓在第一穿基底通孔110中的噪声所导致的射线。通过避免从第一穿基底通孔110的射线信号传输,遮蔽层114亦降低或减缓由第一穿基底通孔110所造成的由噪声所导致的射线。由于遮蔽层114的噪声与串扰最小化特性,因此可缩减第一穿基底通孔110与第二穿基底通孔120之间的距离S,并允许在半导体结构中的所述多个零件的紧密整合。

本公开的一实施例提供一种半导体结构。该半导体结构包括一基底、至少一半导体元件、一第一穿基底通孔、一隔离层、一遮蔽层以及一第二穿基底通孔。该基底具有一前表面与一后表面。该半导体元件设置在该基底的一元件区中。该第一穿基底通孔设置在该基底中,其中该第一穿基底通孔通过该基底的该前表面与该后表面而暴露。该隔离层围绕该第一穿基底通孔设置,其中该隔离层包含一电性隔离材料。该遮蔽层围绕该隔离层设置,其中该遮蔽层包含一电性导电材料,并经由一接地层而接地。该第二穿基底通孔邻近该第一穿基底通孔设置,其中该第二穿基底通孔通过该基底的该前表面与该后表面而暴露。

本公开的另一实施例提供一种半导体结构。该半导体结构包括一基底、至少一半导体元件、一第一穿基底通孔、一隔离层、一遮蔽层以及一第二穿基底通孔。该基底具有一前表面与一后表面。该半导体元件设置在该基底的一元件区中。该第一穿基底通孔设置在该基底中,其中该第一穿基底通孔通过该基底的该前表面与该后表面而暴露。该隔离层围绕该第一穿基底通孔设置,其中该隔离层包含一电性隔离材料。该遮蔽层围绕该隔离层设置,其中该遮蔽层包含一电性导电材料,并经由位在该基底的该前表面上的一第一接触垫而接地。该第二穿基底通孔邻近该第一穿基底通孔设置,其中该第二穿基底通孔通过该基底的该前表面与该后表面而暴露。

本公开的另一实施例提供一种半导体结构。该半导体结构包括一基底、至少一半导体元件、一第一穿基底通孔、一隔离层、一遮蔽层以及一第二穿基底通孔。该基底具有一前表面与一后表面。该半导体元件设置在该基底的一元件区中。该第一穿基底通孔设置在该基底中,其中该第一穿基底通孔通过该基底的该前表面与该后表面而暴露。该隔离层围绕该第一穿基底通孔设置,其中该隔离层包含一电性隔离材料。该遮蔽层设置在该隔离层上方,其中该遮蔽层包含一电性导电材料,并经由位在该基底的该后表面下方的一第二接触垫而接地。该第二穿基底通孔邻近该第一穿基底通孔设置,其中该第二穿基底通孔通过该基底的该前表面与该后表面而暴露。

虽然已详述本公开及其优点,然而应理解可进行各种变化、取代与替代而不脱离权利要求所定义的本公开的精神与范围。例如,可用不同的方法实施上述的许多制程,并且以其他制程或其组合替代上述的许多制程。

再者,本公开的范围并不受限于说明书中所述的制程、机械、制造、物质组成物、手段、方法与步骤的特定实施例。该技艺的技术人士可自本公开的公开内容理解可根据本公开而使用与本文所述的对应实施例具有相同功能或是达到实质上相同结果的现存或是未来发展的制程、机械、制造、物质组成物、手段、方法、或步骤。据此,这些制程、机械、制造、物质组成物、手段、方法、或步骤是包含于本公开的权利要求内。

- 氮化物半导体结构、氮化物半导体发光元件、氮化物半导体晶体管元件、氮化物半导体结构的制造方法以及氮化物半导体元件的制造方法

- 衬底结构、包含衬底结构的半导体封装结构,以及制造半导体封装结构的半导体工艺