半导体封装结构及其制造方法

文献发布时间:2023-06-19 10:08:35

技术领域

本公开涉及半导体封装技术领域,具体涉及半导体封装结构及其制造方法。

背景技术

半导体封装结构可包含将电子组件对接到衬底的电连接结构,例如焊球。通常先设置导电柱以维持预设距离产生预设空间,进而在电子组件与衬底对接时通过该预设空间填入底部填充胶。在制造该电连接结构的过程中(例如在回流焊过程中),形成焊球的焊料可能与导电柱接触形成金属间化合物(IMC,Intermetallic Compound),而金属间化合物的存在会导致焊点产生裂纹,从而降低焊点的可靠性,影响电性能。

发明内容

第一方面,本公开提供了一种半导体封装结构,该半导体封装结构包括:堆叠介电层,由至少一个第一介电层堆叠而成,第一介电层具有第一表面、与第一表面相对的第二表面、以及由第一表面向第二表面延伸的第一凹部,第一表面设置有贯穿第一凹部的导电结构,导电结构与第一介电层之间设置粘合层;导电连接结构,设置于与堆叠介电层的最下层第一介电层的第二表面,导电连接结构与堆叠介电层的最下层第一介电层的导电结构之间设置有粘合层;电子组件,通过堆叠介电层中的导电结构与导电连接结构连接;底部填充胶,填入于堆叠介电层和电子组件之间。

在一些可选的实施方式中,第一介电层的厚度在5μm到20μm之间。

在一些可选的实施方式中,第一凹部的底部形状为圆形,以及第一凹部的底部直径在10μm到50μm之间。

在一些可选的实施方式中,导电结构包括至少一个导电迹线,导电迹线的线宽及线间距L/S在2μm/2μm到3μm/3μm之间。

在一些可选的实施方式中,导电迹线的厚度在2μm到3μm之间。

在一些可选的实施方式中,导电连接结构包括:阻挡层、焊层及焊料元件。

在一些可选的实施方式中,阻挡层为钛铜合金或钛镍铜合金。

在一些可选的实施方式中,焊层为金、银、铜、镍、铝合金或其合金。

在一些可选的实施方式中,焊层的厚度在0.1μm到3μm之间。

在一些可选的实施方式中,焊料元件为焊球,焊球的直径在5μm到80μm之间。

在一些可选的实施方式中,焊料元件为锡或锡银合金。

在一些可选的实施方式中,导电连接结构包括至少一个焊料凸块,焊料凸块的直径和间距小于等于5μm/5μm。

在一些可选的实施方式中,导电结构具有邻近第二表面的第三表面,其中,第三表面被第一介电层与粘合层完全覆盖。

在一些可选的实施方式中,粘合层包括钛。

在一些可选的实施方式中,半导体封装结构还包括:封装材,封装材包覆电子组件。

第二方面,本公开提供了一种制造半导体封装结构的方法,该方法包括:提供载体;在载体形成导电连接结构;在导电连接结构形成堆叠介电层,堆叠介电层是由至少一个第一介电层堆叠而成,第一介电层具有第一表面、与第一表面相对的第二表面、以及由第一表面向第二表面延伸的第一凹部,第一表面设置有贯穿第一凹部的导电结构,导电结构与第一介电层之间设置粘合层;在堆叠介电层上放置电子组件,将电子组件与堆叠介电层电连接,以及在电子组件与堆叠介电层之间填入底部填充胶。

在一些可选的实施方式中,在载体形成导电连接结构,包括:在载体形成种子层;在种子层形成第二介电层;在第二介电层形成第二凹部,并在第二凹部形成导电连接结构;以及方法还包括:去除载体、种子层以及第二介电层。

在一些可选的实施方式中,在导电连接结构形成堆叠介电层,包括:在导电连接结构形成第一介电层,在第一介电层形成第一凹部以暴露导电连接结构;

在一些可选的实施方式中,在第一介电层依次形成粘合层和导电结构。

在一些可选的实施方式中,第一介电层和第二介电层的材料不同。

在一些可选的实施方式中,该方法还包括:去除第一介电层的部分。

在一些可选的实施方式中,导电连接结构包括阻挡层、焊层以及焊料元件。

在一些可选的实施方式中,焊料元件为焊球,以及该方法还包括:对焊料进行回焊处理形成焊球。

在一些可选的实施方式中,该方法还包括:注入封装材以包覆电子组件。

为解决现有技术中半导体封装结构中可能存在因产生金属间化合物而导致焊点的可靠性降低的问题。本公开提供的半导体封装结构及其制造方法,通过在介电层定义出具有预设高度的凹部以维持预设距离方便底部填充胶的填入,并且设置贯穿该凹部的导电结构以实现导电柱的电连接功能,再设置粘合层以包裹该导电结构,避免导电结构暴露与焊球接触形成金属间化合物。

附图说明

通过阅读参照以下附图所作的对非限制性实施例所作的详细描述,本公开的其它特征、目的和优点将会变得更明显:

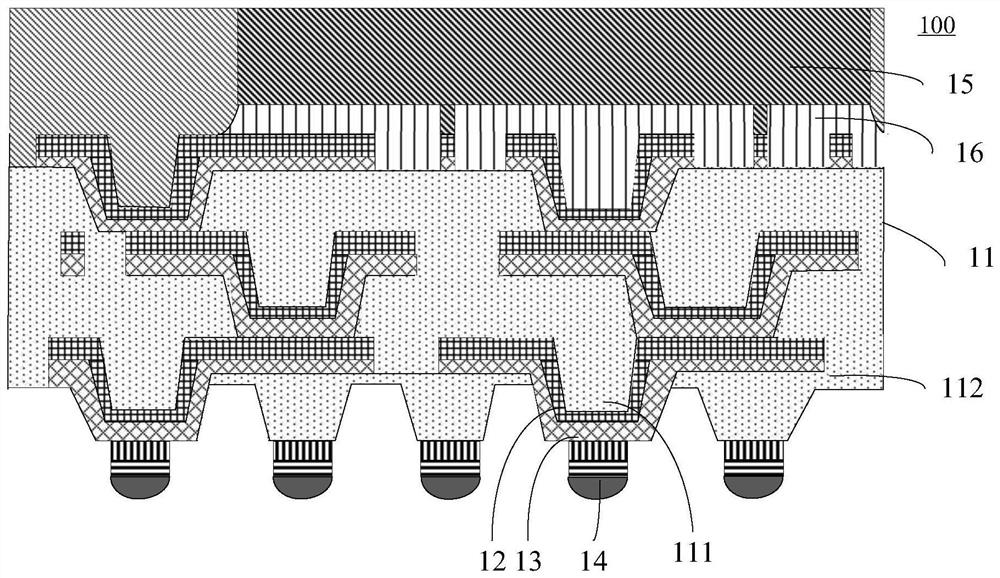

图1是根据本公开的半导体封装结构的一个实施例的结构示意图;

图2是根据本公开的半导体封装结构的又一个实施例的结构示意图;

图3A到图3Q是图2实施例的半导体封装结构的制造过程中的结构示意图。

符号说明:

11-堆叠介电层,111-第一凹部,112-第一介电层,12-导电结构,13-粘合层,14-导电连接结构,15-电子组件,16-底部填充胶,17-封装材,31-载体,32-种子层,33-第二介电层,34-第二凹部。

具体实施方式

下面结合附图和实施例对说明本公开的具体实施方式,通过本说明书记载的内容本领域技术人员可以轻易了解本公开所解决的技术问题以及所产生的技术效果。可以理解的是,此处所描述的具体实施例仅仅用于解释相关发明,而非对该发明的限定。另外,为了便于描述,附图中仅示出了与有关发明相关的部分。

需要说明的是,说明书附图中所绘示的结构、比例、大小等,仅用于配合说明书所记载的内容,以供本领域技术人员的了解与阅读,并非用以限定本公开可实施的限定条件,故不具技术上的实质意义,任何结构的修饰、比例关系的改变或大小的调整,在不影响本公开所能产生的功效及所能达成的目的下,均应仍落在本公开所揭示的技术内容得能涵盖的范围内。同时,本说明书中所引用的如“上”、“第一”、“第二”及“一”等用语,也仅为便于叙述的明了,而非用以限定本公开可实施的范围,其相对关系的改变或调整,在无实质变更技术内容下,当也视为本公开可实施的范畴。

请参考图1,图1示出了根据本公开的半导体封装结构的一个实施例的结构示意图。半导体封装结构100可以包括堆叠介电层11、导电结构12、粘合层13、导电连接结构14、电子组件15以及底部填充胶16。其中,堆叠介电层11,由至少一个第一介电层112堆叠而成,第一介电层112具有第一表面和与第一表面相对的第二表面、以及由第一表面向第二表面延伸的第一凹部111,第一表面设置有贯穿第一凹部111的导电结构12,导电结构12与第一介电层112之间设置粘合层13;导电连接结构14,设置于与堆叠介电层11的最下层第一介电层112的第二表面,导电连接结构14与堆叠介电层11的最下层第一介电层112的导电结构12之间设置有粘合层13;电子组件15,通过堆叠介电层11中的导电结构12与导电连接结构14连接;底部填充胶16,填入于堆叠介电层11和电子组件15之间。

堆叠介电层11所包括的至少一个第一介电层112可以采用各种有机材料,例如环氧树脂(Epoxy)、PI树脂等。

电子组件15可以是有源组件,例如芯片等,也可以是无源组件,例如电容器、电感器、电阻器等。

底部填充胶16例如可以是毛细底部填充料(CUF,capillary underfill)、成型底部填充料(MUF,molded underfill)、非导电胶(NCP,Non-conductive Paste)等。底部填充胶16可以填充空隙,从而达到加固的目的。

粘合层13可以改善导电结构12与第一介电层112之间的结合力,也可以防止金属间互相扩散。

在一些可选的实施方式中,第一介电层112的厚度在5μm到20μm之间。

在一些可选的实施方式中,第一凹部111的底部形状为圆形,以及第一凹部111的底部直径在10μm到50μm之间。

在一些可选的实施方式中,导电结构12包括至少一个导电迹线,导电迹线的线宽及线间距Line/Space在2μm/2μm到3μm/3μm之间。

在一些可选的实施方式中,导电迹线的厚度在2μm到3μm之间。

在一些可选的实施方式中,导电连接结构14包括:阻挡层、焊层及焊料元件。

在一些可选的实施方式中,阻挡层为钛铜合金或钛镍铜合金。

在一些可选的实施方式中,焊层为金、银、铜、镍、铝合金或其合金。

在一些可选的实施方式中,焊层的厚度在0.1μm到3μm之间。

在一些可选的实施方式中,焊料元件为焊球,焊球的直径在5μm到80μm之间。

在一些可选的实施方式中,焊料元件为锡或锡银合金。

在一些可选的实施方式中,导电连接结构14包括至少一个焊料凸块,焊料凸块的直径和间距小于等于5μm/5μm。

在一些可选的实施方式中,粘合层13包括钛。

在一些可选的实施方式中,导电结构12具有邻近第二表面的第三表面,其中,第三表面被第一介电层112与粘合层13完全覆盖。这样可以避免导电结构12暴露。

在一些可选的实施方式中,半导体封装结构还包括:封装材17,封装材17包覆电子组件15。

这里,封装材17例如可以是环氧树脂(Epoxy)、PI树脂、BT(BismaleimideTriazine)等。

半导体封装结构100通过在第一介电层112上定义出第一凹部111,设置贯穿第一凹部111的导电结构12,再设置粘合层13以包裹该导电结构12,避免导电结构12暴露进而与焊球接触形成金属间化合物。

请参考图2,图2示出了根据本公开的半导体封装结构的又一个实施例的结构示意图。半导体封装结构200为半导体封装结构100中堆叠介电层11包括一个第一介电层112的结构示意图。

图3A到图3Q是图2实施例的半导体封装结构的制造过程中的结构示意图。为了更好地理解本公开的各方面,已简化各图。

请参考图3A,提供载体31。可以采用各种工艺在载体31形成种子层32。种子层32可以采用铜或其他合适材料。

请参考图3B,在种子层32形成第二介电层33。第二介电层33可以采用有机材料,例如环氧树脂(Epoxy)、PI树脂等。

请参考图3C,在第二介电层33形成第二凹部34。例如可以通过激光钻孔或光刻蚀刻等其他合适工艺形成第二凹部34。

请参考图3D,在第二凹部34形成导电连接结构14。可以在第二凹部34依次镀覆焊料、焊层以及阻挡层,以形成导电连接结构14。

请参考图3E,在第二介电层33上形成第一介电层112。第一介电层112和第二介电层33可以选用不同的材料。

请参考图3F,在第一介电层112形成第一凹部111。例如可以通过激光钻孔或光刻蚀刻等其他合适工艺形成第一凹部111。

请参考图3G,在第一介电层112形成粘合层13。可以在第一介电层112镀覆粘合层13,该粘合层13贯穿第一凹部111。

请参考图3H,在粘合层13上形成金属层。可以在粘合层13镀覆金属层,金属层可以采用铜或其他合适材料。

请参考图3I,在金属层上图形化定义出导电结构12。通过光刻蚀刻等工艺定义出导电结构12。

请参考图3J,将电子组件15与第一介电层112电连接,以及在电子组件15与第一介电层112之间填入底部填充胶16。可以将电子组件15的凸块与导电结构12进行对接,将电子组件15与第一介电层112电连接,并在电子组件15与第一介电层112之间填入底部填充胶16,以填充电子组件15与第一介电层112之间的空隙。

请参考图3K,注入封装材17以包覆电子组件15。

请参考图3L,去除载体31。

请参考图3M,去除种子层32。可以采用蚀刻去除种子层32。

请参考图3N,去除第二介电层33。可以采用剥离去除第二介电层33。

请参考图3O,去除部分第一介电层112。可以采用剥离去除部分第一介电层112。

请参考图3P,对焊料回焊处理形成焊球。经过回焊处理工艺,可以将图3D中镀覆的焊料(锡膏)加热融化至液态球状,之后冷却形成球状的焊球(凸块)。

在一些可选的实施方式中,请参考图3Q,图3Q为图3P所示的结构示意图的仰视图,其呈现了回焊处理后形成的焊球阵列。这里,可以根据实际设计需要,设置规则或不规则排列。

尽管已参考本公开的特定实施例描述并说明本公开,但这些描述和说明并不限制本公开。所属领域的技术人员可清楚地理解,可进行各种改变,且可在实施例内替代等效元件而不脱离如由所附权利要求书限定的本公开的真实精神和范围。图示可能未必按比例绘制。归因于制造过程中的变量等等,本公开中的艺术再现与实际设备之间可能存在区别。可存在未特定说明的本公开的其它实施例。应将说明书和图式视为说明性的,而非限制性的。可作出修改,以使特定情况、材料、物质组成、方法或过程适应于本公开的目标、精神以及范围。所有此些修改都打算属于在此所附权利要求书的范围内。虽然已参考按特定次序执行的特定操作描述本文中所公开的方法,但应理解,可在不脱离本公开的教示的情况下组合、细分或重新排序这些操作以形成等效方法。因此,除非本文中特别指示,否则操作的次序和分组并不限制本公开。

- 一种半导体封装结构及半导体封装结构的制造方法

- 用于一半导体封装结构的基板、半导体封装结构及其制造方法