一种基于SCL实时高电平脉宽的I2C从机电路

文献发布时间:2023-06-19 10:08:35

技术领域

本发明涉及I2C从机电路领域,具体涉及一种基于SCL实时高电平脉宽的I2C从机电路。

背景技术

I2C总线是由Philips公司开发的一种简单、双向二线制同步串行总线。它只需要两根线(SCL和SDA)即可在连接于总线上的器件之间传送信息。

I2C总线中,SCL是时钟线,一般由主机发起,从机负责接收。

I2C总线中,SDA是数据线,主机和从机都会通过SDA发送信息给对方。主机和从机并不会同时在SDA上发送数据,通常会根据I2C协议中规定的时序,主机和从机选取适当的时刻发送数据到SDA。

根据I2C的协议,无论主机或者从机,想要在SDA上发送信息时,必须要遵守在SCL低电平区间,I2C主机或者从机才能改变SDA电平发送数据,在SCL高电平期间,不能改变SDA电平的规定。同时还需要满足SDA的建立时间以及保持时间等要求。否则,会造成数据传输的失败。

在芯片内实现I2C从机电路时,需要考虑到I2C总线上的时钟SCL和数据SDA相对于芯片内部工作时钟是异步关系,所以需要先对SCL和SDA做同步处理。如图2-3所示,I2C从机电路一般分为同步及判断电路模块和I2C从机状态机模块,所示同步处理一般是使用芯片内部时钟驱动的2个串联DFF采样异步信号,所以需要耗费2个工作时钟周期。I2C从机电路拿到同步后的SCL和同步后的SDA,会做出SCL/SDA上升沿和SCL/SDA下降沿的判断,再根据自身电路中设计的状态机,处理总线上主机需要的读写操作。

当I2C从机电路需要发送ACK或者发送寄存器读数据时,根据I2C协议必须要选择在SCL的低电平时发送。如果采用上述常规电路设计,如图2所示首先要对SCL做同步处理,同步处理过后,才能判断SCL的下降沿的时刻。在SCL的下降沿判断为真时,从机才能改变SDA电平,发送适当的数据。

因为SCL同步需要消耗2个工作时钟周期,判断SCL下降沿判断为真又需要一个时钟周期,再加上I2C从机电路内部的逻辑延迟,会导致最终I2C从机电路驱动SDA实际电平的变化,会晚于SCL实际的下降沿至少3个工作时钟周期。

当I2C主机需要较高的SCL频率来提高数据带宽,从而保证数据通信的实时性,此时I2C从机电路为了保证3个工作时钟周期的延迟不会违反SDA建立时间的要求,只能选择提高自身的工作时钟频率,如图1所示。

一方面,提高工作时钟频率意味着将会提升芯片的功耗,另一方面,如果芯片内部无法给I2C从机电路提供更高频率的工作时钟,I2C从机电路将无法支持I2C主机发起的高频高数据带宽I2C通信。

发明内容

本发明要解决的技术问题是提供一种基于SCL实时高电平脉宽的I2C从机电路,一方面该电路可以在现有的工作时钟频率下,完成更高频更高带宽I2C通信;另一方面也可以通过调低I2C从机电路的工作时钟频率,有效降低芯片的功耗。

为了解决上述技术问题,本发明提供了一种基于SCL实时高电平脉宽的I2C从机电路,包括同步及判断电路模块和I2C从机状态机模块,所述同步及判断电路模块和I2C从机状态机模块之间设置有检测SCL实时高电平脉宽及预测SCL下降沿时刻功能模块,所述检测SCL实时高电平脉宽及预测SCL下降沿时刻功能模块能够预测SCL下降沿位置,并将预测出的SCL下降沿位置通知I2C从机状态机模块。

本发明一个较佳实施例中,进一步包括所述检测SCL实时高电平脉宽及预测SCL下降沿时刻功能模块包括SCL实时高电平脉宽计数模块、SCL有效高电平脉宽期间判断模块、SCL高电平脉宽周期数判断及缓存模块和预测SCL下降沿时刻模块。

本发明一个较佳实施例中,进一步包括所述SCL实时高电平脉宽计数模块实时计数SCL每个高电平脉宽所需的工作时钟周期,所述SCL实时高电平脉宽计数模块在每个工作时钟上升沿的工作逻辑为:

逻辑S1-1:当检测到SCL时钟上升沿后,寄存器i2c_scl_period_cnt清零;

逻辑S1-2:当逻辑S1-1中没有检测到SCL时钟上升沿时,寄存器i2c_scl_period_cnt自动加1。

本发明一个较佳实施例中,进一步包括所述SCL有效高电平脉宽期间判断模块识别I2C数据传输区间,所述SCL有效高电平脉宽期间判断模块在每个工作时钟上升沿的工作逻辑为:

逻辑S2-1:当检测到i2c_stop和i2c_start时,寄存器i2c_scl_period_start清零;

逻辑S2-2:当没有检测到i2c_stop和i2c_start时,且检测到SCL上升沿时,寄存器i2c_scl_period_start置高;当检测到SCL下降沿时,寄存器i2c_scl_period_start清零;

逻辑S2-3:当没有检测到i2c_stop和i2c_start时,且没有检测到SCL上升沿或下降沿时,寄存器i2c_scl_period_start保持原值。

本发明一个较佳实施例中,进一步包括所述SCL高电平脉宽周期数判断及缓存模块根据SCL实时高电平脉宽计数模块、SCL有效高电平脉宽期间判断模块计数结果,计算出本次I2C全部传输周期内平均SCL高电平脉宽周期数,所述SCL高电平脉宽周期数判断及缓存模块在每个工作时钟上升沿的工作逻辑为:

逻辑S3-1:当检测到i2c_stop和i2c_start时,寄存器i2c_scl_period清零;

逻辑S3-2-1:当没有检测到i2c_stop和i2c_start时,且检测到SCL下降沿与寄存器i2c_scl_period_start为高时,如果寄存器i2c_scl_period当前值为0时,直接将寄存器i2c_scl_period_cnt赋值给寄存器i2c_scl_period;

逻辑S3-2-2:当没有检测到i2c_stop和i2c_start时,且检测到SCL下降沿与寄存器i2c_scl_period_start为高时,如果寄存器i2c_scl_period当前值不为0时,当寄存器i2c_scl_period当前值比寄存器i2c_scl_period_cnt值大的话,寄存器i2c_scl_period减1;当寄存器i2c_scl_period当前值比寄存器i2c_scl_period_cnt值小的话,寄存器i2c_scl_period加1;当上述两个条件都不成立时,寄存器i2c_scl_period保持原值;

逻辑S3-3:当没有检测到i2c_stop和i2c_start时,且没有检测到SCL下降沿与寄存器i2c_scl_period_start为高时,寄存器i2c_scl_period保持原值。

本发明一个较佳实施例中,进一步包括所述预测SCL下降沿时刻模块根据SCL高电平脉宽周期数判断及缓存模块计算出的数据和已知的SCL上升沿,及时向I2C从机状态机模块提供预测的SCL下降沿位置,所述预测SCL下降沿时刻模块的工作逻辑为:

逻辑S4-1:当寄存器i2c_scl_period等于1时,代表SCL的频率刚好是工作时钟频率的4分频,此时预测下降沿i2c_scl_h2l_predict就是上升沿i2c_scl_l2h;

逻辑S4-2:当寄存器i2c_scl_period不等于1时,则将寄存器(i2c_scl_period_cnt==(i2c_scl_period-2))&&i2c_scl_period_start的结果赋值给预测下降沿i2c_scl_h2l_predict。

本发明一个较佳实施例中,进一步包括用于接收I2C主机发送的SCL高电平脉宽,所述SCL高电平脉宽为稳定脉宽。

本发明的有益效果:

本发明根据接收的SCL高电平脉宽可以计算出SCL平均高电平脉宽周期数,进而再利用计算出来的SCL平均高电平脉宽周期数和已知的SCL上升沿就可以准确的预测出SCL下降沿的位置,通过快速预测SCL下降沿的位置取代了现有技术中对SCL采样做同步处理和判断SCL的下降沿的方法,实现了两方面的有益效果:

一方面,保持I2C从机在现有的工作时钟频率下,支持与I2C主机最高通信频率为I2C从机工作时钟频率4分频的I2C通信,实现了更高频更高带宽I2C通信;

另一方面,保持现有的I2C通信的频率和带宽,可以通过调低I2C从机电路的工作时钟频率,有效降低芯片的功耗。

附图说明

图1是现有技术芯片顶层部分架构图;

图2是现有技术I2C从机电路的电路图;

图3是现有技术I2C从机电路的原理框图;

图4是本发明的基于SCL实时高电平脉宽的I2C从机电路的原理框图;

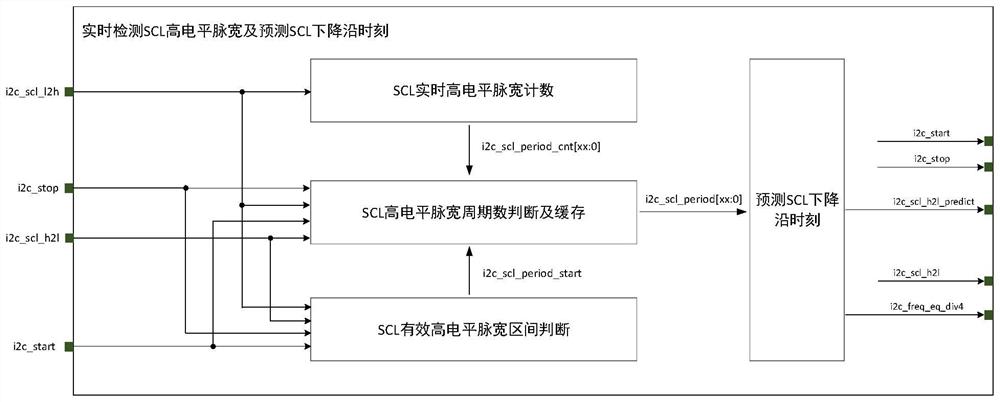

图5是本发明的检测SCL实时高电平脉宽及预测SCL下降沿时刻功能模块的电路原理框图。

具体实施方式

下面结合附图和具体实施例对本发明作进一步说明,以使本领域的技术人员可以更好地理解本发明并能予以实施,但所举实施例不作为对本发明的限定。

参照图1所示,本发明的基于SCL实时高电平脉宽的I2C从机电路的一实施例,包括同步及判断电路模块和I2C从机状态机模块,所述同步及判断电路模块和I2C从机状态机模块之间设置有检测SCL实时高电平脉宽及预测SCL下降沿时刻功能模块,所述检测SCL实时高电平脉宽及预测SCL下降沿时刻功能模块预测SCL下降沿位置,并将预测出的SCL下降沿位置通知I2C从机状态机模块。

本发明的原理是:借助I2C协议规定,在I2C从机第一次需要发送信息到SDA数据线的时刻之前,I2C从机已经接收了8个SCL高电平脉宽。本专利根据已经接收的8次SCL高电平脉宽可以计算出SCL平均高电平脉宽周期数。本专利利用计算出来的高电平脉冲数和已知的SCL上升沿就可以准确的预测出SCL下降沿的位置,并将预测出的下降沿位置通知I2C从机状态机模块。

本发明取代了现有技术中对SCL采样做同步处理和判断SCL的下降沿的方法,实现了两方面的有益效果:

一方面,保持I2C从机在现有的工作时钟频率下,支持与I2C主机最高通信频率为I2C从机工作时钟频率4分频的I2C通信,实现了更高频更高带宽I2C通信;

另一方面,保持现有的I2C通信的频率和带宽,可以通过调低I2C从机电路的工作时钟频率,有效降低芯片的功耗。

参照图2所示,所述检测SCL实时高电平脉宽及预测SCL下降沿时刻功能模块包括SCL实时高电平脉宽计数模块、SCL有效高电平脉宽期间判断模块、SCL高电平脉宽周期数判断及缓存模块和预测SCL下降沿时刻模块;所述SCL实时高电平脉宽计数模块、SCL有效高电平脉宽期间判断模块用于获取真实的SCL高电平脉宽;所述SCL高电平脉宽周期数判断及缓存模块用于利用上述SCL实时高电平脉宽计数模块、SCL有效高电平脉宽期间判断模块得到的真实SCL高电平脉宽,计算和存储I2C本次传输周期内平均SCL高电平脉宽周期数;所述预测SCL下降沿时刻模块根据上述模块提供的数据和上升沿,及时向I2C从机状态机模块提供预测的SCL下降沿位置。

具体地,所述SCL实时高电平脉宽计数模块实时计数SCL每个高电平脉宽所需的工作时钟周期,用寄存器i2c_scl_period_cnt来实现计数,所述SCL实时高电平脉宽计数模块在每个工作时钟上升沿的工作逻辑为:

逻辑S1-1:当检测到SCL时钟上升沿后,寄存器i2c_scl_period_cnt清零;

逻辑S1-2:当逻辑S1-1中没有检测到SCL时钟上升沿时,寄存器i2c_scl_period_cnt自动加1。

具体地,所述SCL有效高电平脉宽期间判断模块识别I2C数据传输区间,只有在I2C真正数据传输区间内,计算出的SCL高电平脉宽周期数才是真实的,所述SCL有效高电平脉宽期间判断模块在每个工作时钟上升沿的工作逻辑为:

逻辑S2-1:当检测到i2c_stop和i2c_start时,寄存器i2c_scl_period_start清零;

逻辑S2-2:当没有检测到i2c_stop和i2c_start时,且检测到SCL上升沿时,寄存器i2c_scl_period_start置高;当检测到SCL下降沿时,寄存器i2c_scl_period_start清零;

逻辑S2-3:当没有检测到i2c_stop和i2c_start时,且没有检测到SCL上升沿或下降沿时,寄存器i2c_scl_period_start保持原值。

具体地,所述SCL高电平脉宽周期数判断及缓存模块根据SCL实时高电平脉宽计数模块、SCL有效高电平脉宽期间判断模块计数结果,计算出本次I2C全部传输周期内平均SCL高电平脉宽周期数,用寄存器i2c_scl_period来实现存储,所述SCL高电平脉宽周期数判断及缓存模块在每个工作时钟上升沿的工作逻辑为:

逻辑S3-1:当检测到i2c_stop和i2c_start时,寄存器i2c_scl_period清零;

逻辑S3-2-1:当没有检测到i2c_stop和i2c_start时,且检测到SCL下降沿与寄存器i2c_scl_period_start为高时,如果寄存器i2c_scl_period当前值为0时,直接将寄存器i2c_scl_period_cnt赋值给寄存器i2c_scl_period;

逻辑S3-2-2:当没有检测到i2c_stop和i2c_start时,且检测到SCL下降沿与寄存器i2c_scl_period_start为高时,如果寄存器i2c_scl_period当前值不为0时,当寄存器i2c_scl_period当前值比寄存器i2c_scl_period_cnt值大的话,寄存器i2c_scl_period减1;当寄存器i2c_scl_period当前值比寄存器i2c_scl_period_cnt值小的话,寄存器i2c_scl_period加1;当上述两个条件都不成立时,寄存器i2c_scl_period保持原值;

逻辑S3-3:当没有检测到i2c_stop和i2c_start时,且没有检测到SCL下降沿与寄存器i2c_scl_period_start为高时,寄存器i2c_scl_period保持原值。

具体地,所述预测SCL下降沿时刻模块根据SCL高电平脉宽周期数判断及缓存模块计算出的数据和已知的SCL上升沿,及时向I2C从机状态机模块提供预测的SCL下降沿位置,所述预测SCL下降沿时刻模块的工作逻辑为:

逻辑S4-1:当寄存器i2c_scl_period等于1时,代表SCL的频率刚好是工作时钟频率的4分频,此时预测下降沿i2c_scl_h2l_predict就是上升沿i2c_scl_l2h;

逻辑S4-2:当寄存器i2c_scl_period不等于1时,则将寄存器(i2c_scl_period_cnt==(i2c_scl_period-2))&&i2c_scl_period_start的结果赋值给预测下降沿i2c_scl_h2l_predict。

具体地,本实施例的I2C从机电路用于实现与I2C主机之间的通讯,对与I2C主机能够保障正常通信的I2C高电平宽度有一定限制,I2C从机电路能够保障与主机正常通信的I2C高电平最长宽度取决于,本专利内部用于检测SCL实时高电平脉宽的寄存器i2c_scl_period和i2c_scl_period_cnt的具体实现位宽,以及取决于I2C从机电路的工作时钟频率,因此,根据不同的I2C主机需求,可以推导出实现两组寄存器i2c_scl_period和i2c_scl_period_cnt不同的位宽。

具体地,本实施例的I2C从机电路用于接收I2C主机发送的SCL高电平脉宽,所述SCL高电平脉宽为稳定脉宽,所述I2C主机还应保证每次发送的SCL高电平脉宽不应波动过大,对于波动较大的数据传输片段,导致计算出的SCL高电平平均脉宽无法应用于波动较大的数据传输片段。

以上所述实施例仅是为充分说明本发明而所举的较佳的实施例,本发明的保护范围不限于此。本技术领域的技术人员在本发明基础上所作的等同替代或变换,均在本发明的保护范围之内。本发明的保护范围以权利要求书为准。

- 一种基于SCL实时高电平脉宽的I2C从机电路

- 一种基于I2C通信协议的获取从机地址的方法及I2C通信系统