配置存储器位线控制电路以及FPGA位线控制系统

文献发布时间:2023-06-19 10:51:07

技术领域

本发明涉及FPGA(Field-Programmable Gate Array,即现场可编程门阵列)设计领域,具体涉及一种配置存储器位线控制电路以及FPGA位线控制系统。

背景技术

FPGA是在PAL(Programmable Array Logic,可编程阵列逻辑)、GAL(GenericArray Logic,通用阵列逻辑)、CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)等可编程器件的基础上进一步发展产生的。它是作为专用集成电路(ApplicationSpecific Integrated Circuit,ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

参见图1,基本的FPGA主要由如下几个部分组成:可编程输入输出IO模块101、可编程互联模块102和可编程逻辑模块103。用户可以通过可配置逻辑模块103来实现各种设计,通过可配置输入输出IO模块101与外界进行通信,并保证输入输出电压与电流标准,通过可配置互联模块102连接可配置输入输出IO模块101与可配置逻辑模块103。

一般来说,FPGA相当于一个超大的数字电路集合,它本身并不具有特定的电路功能,需要通过具体的设计并转换成它支持的配置位流,从而选择该数字电路集合的某些电路进行组合,从而实现我们想要的具体电路。但是,超大规模FPGA进行扩展设计时位线控制会存在一些问题,例如寄生电容电阻的影响等,会对超大规模FPGA的扩展产生一定的限制。

发明内容

本发明要解决的主要技术问题是,提供一种配置存储器位线控制电路以及FPGA位线控制系统,解决现有超大规模FPGA扩展设计时的位线控制存在限制的问题。

为解决上述技术问题,本发明提供一种配置存储器位线控制电路,包括:数据读写控制模块、存储模块、传输模块以及缓冲器;

所述数据读写控制模块,用于根据所述位线控制电路所处的状态以及信号将接收到的数据写入所述存储模块或者将所述存储模块中的数据进行读出;

所述存储模块,用于存储所述数据读写控制模块写入或者读出的数据;

所述传输模块,用于传输所述数据读写控制模块接收到的数据或者从所述存储模块读出的数据;

所述缓冲器,用于在所述数据读写控制模块对接收到的数据写入所述存储模块的传输过程中增加驱动。

可选的,所述传输模块包括位线传输通道,所述缓冲器按照预设距离设置于所述位线传输通道上。

可选的,所述数据读写控制模块包括写字线控制电路、写驱动电路及读配套电路;

所述写驱动电路,用于根据接收到的数据产生BL信号,所述BL信号分别往左往右传输;

所述写字线控制电路,用于将所述BL信号写入所述存储模块;

所述读配套电路,用于读出所述存储模块中数据。

可选的,所述位线控制电路所处的状态包括写入状态和回读状态,所述信号为字线信号;

写状态时,所述写字线控制电路在所述字线信号为1时将所述BL信号写入所述存储模块;

在读状态时,所述读配套电路在所述字线信号为1时读出所述输出信号。

可选的,所述缓冲器为双向。

可选的,所述存储模块包括相互连接的MOS管和反相器。

可选的,所述MOS管包括第一MOS管和第二MOS管,所述反相器包括第一反相器和第二反相器;

所述第一MOS管和所述第二MOS管进行串联连接,所述第一反相器和所述第二反相器进行并行连接并设置于所述第一MOS管和所述第二MOS管之间。

为了解决上述问题,本发明还提供了一种FPGA位线控制系统,包括:配置寄存器、可编程逻辑模块以及如权利要求1-7任一项所述的配置存储器位线控制电路;所述可编程逻辑模块包括至少一个区域,每个区域内设置有所述配置存储器位线控制电路;

所述配置寄存器,用于配置帧地址并将帧地址与数据输出到所述配置存储器位线控制电路;

所述配置存储器位线控制电路,用于在进行写入操作时,将所述数据写到与所述地址对应的所述存储模块中;在进行读出操作时,根据所述地址将对应的所述存储模块中的数据读出。

可选的,所述正配置寄存器包括帧地址寄存器、帧数据输入寄存器以及帧数据输出寄存器;所述配置存储器位线控制电路还包括帧地址数据转换模块;

所述帧地址寄存器,用于配置帧地址并将帧地址数据发送给所述帧地址数据转换模块;

所述帧数据输入寄存器,用于将数据输出到所述数据读写控制模块;

所述数据读写控制模块,用于将所述数据通过所述缓冲器写到与所述地址对应的所述存储模块中;还用于根据所述地址从所述存储模块中读出数据并将读出的数据发送到所述帧数据输入寄存器;

所述帧数据输入寄存器,还用于接收所述数据读写控制模块从所述存储模块中读出的数据;

所述数据读写控制模块,还用于从所述帧数据输入寄存器读出所述数据,并将所述数据发送给所述帧数据输出寄存器。

可选的,所述FPGA位线控制系统还包括至少一个多级缓冲器以及至少一个两级与非门;

所述多级缓冲器,用于接收所述帧数据输入寄存器输入的数据并将所述数据发送至对应区域内的配置存储器位线控制电路;

所述两级与非门,用于在回读时将读出的数据输出到所述帧数据输出寄存器。

本发明的有益效果是:

本发明提供的配置存储器位线控制电路以及FPGA位线控制系统,数据控制读写模块根据位线控制电路所处的状态以及信号将接收到的数据写入存储模块或者将存储模块中的数据进行读出,在数据控制读写模块对接收到的数据写入存储模块的传输过程中进行驱动;可见本发明可以通过增加驱动缓冲器来避免寄生电容电阻的影响,提高了系统可扩展性,缩短了新产品面世的时间,降低产品的研发成本。

本发明其他特征和相应的有益效果在说明书的后面部分进行阐述说明,且应当理解,至少部分有益效果从本发明说明书中的记载变的显而易见。

附图说明

图1为一种FPGA通用结构示意图;

图2为一种超大规模FPGA的结构示意图;

图3为一种通用的FPGA配置存储器接口结构示意图;

图4为本发明实施例一提供的超大规模FPGA的控制结构示意图;

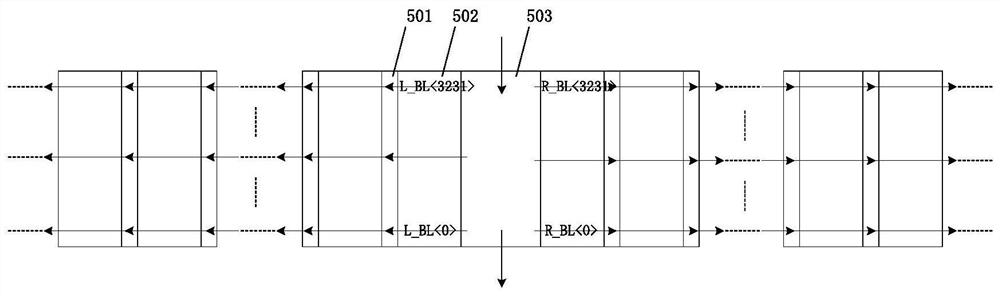

图5为本发明实施例一提供的一个区域内的配置存储器位线控制电路结构示意图;

图6为本发明实施例一提供的配置存储器的电路示意图;

图7为本发明实施例二提供的FPGA系统中多个区域之间的位线控制信号及帧数据输入输出的数据传递示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例只是本发明中一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

参见图2所示的一种超大规模FPGA的结构示意图,超大规模FPGA结构主要包括五个部分,配置控制系统201(Configuration Control System,CCS),可编程输入输出IO模块202,高速serdes203,DLL204(Delay-locked Loop,延迟锁相环)以及可编程逻辑模块205。

配置控制系统主要完成对全芯片的功能配置与控制操作,配置控制系统主要包括配置数据流、配置控制电路、配置存储器等几部分组成;配置控制系统就是将用户的配置位流数据写入到相应的配置数据存储器SRAM中,通过SRAM的输出来控制各电路模块的选通或者关闭,并最终组合成特定功能的电路系统。

FPGA配置控制系统中最基础,也是最重要的功能就是将数量庞大且具有一定格式的配置数据迅速且准确地写到配置存储器内。这个配置的过程与用户的实际电路无关,无论用户的设计复杂度如何,只要芯片规模能满足用户设计的需求,对于配置控制系统来说,其工作过程没有区别。FPGA全芯片分成多个相似的region,主要的可编程逻辑资源分成多个区域,随着门级数量及芯片面积的增大,对整个FPGA的控制系统提出了更高的要求,例如,配置存储器要求FPGA配置控制系统能够选择任意的区域、行、列和帧的存储单元,使其能够灵活地对配置存储器进行配置,达到迅速且准确地进行配置与重配,减少配置的时间,提高配置的效率。

参见图3所示,图3为一种通用的FPGA配置存储器接口结构示意图。如图所示,FPGA配置存储器接口结构包括帧地址数据转换模块和数据读写控制模块,配置寄存器包括帧地址寄存器、帧数据输入寄存器以及帧数据输出寄存器;进行配置操作时,配置寄存器将帧地址寄存器配置的地址和帧数据输入寄存器的数据输出到配置存储器接口,配置存储器接口将数据写到配置存储器对应地址的存储单元中。进行回读操作时,配置存储器接口根据配置寄存器给的帧地址寄存器配置的地址,将配置存储器对应地址的存储单元中存储的数据内容读出到配置寄存器中的帧数据输入寄存器,然后配置存储器接口再从帧数据输入寄存器中读出数据内容,再按照接口标准规范的时序将数据输出到帧数据输出寄存器,最后输出给用户使用。

配置存储器接口中,帧地址数据转换模块将从帧地址寄存器得到的帧地址数据进行处理,转换成配置存储器中对应的区域地址、列地址和帧地址输出给配置存储器,数据读写控制模块根据配置控制系统进行的是配置操作还是回读操作,将数据写入配置存储器对应地址的存储单元中或者从配置存储器对应地址的存储单元中读出。

但是现有的超大规模FPGA中,由于同一个region内存在寄生电阻电容,影响正常写入数据,且多个region之间位线控制存在一定的限制,影响超大规模FPGA继续增加region进行扩展。

为了解决上述问题,本发明提供一种配置存储器位线控制电路,配置存储器位线控制电路包括数据读写控制模块、存储模块、传输模块以及缓冲器,数据控制读写模块根据位线控制电路所处的状态以及信号将接收到的数据写入存储模块或者将存储模块中的数据进行读出,在数据控制读写模块对接收到的数据写入存储模块的传输过程中进行驱动;这样可以通过增加驱动缓冲器来避免寄生电容电阻的影响,提高了系统可扩展性,缩短了新产品面世的时间,降低产品的研发成本。下面通过具体实施方式结合附图对本发明作进一步详细说明。

实施例一:

本实施例提供的配置存储器位线控制电路包括数据读写控制模块、存储模块、传输模块以及缓冲器;

数据读写控制模块,用于根据位线控制电路所处的状态以及信号将接收到的数据写入存储模块或者将存储模块中的数据进行读出;

存储模块,用于存储数据读写模块写入或者读出的数据;

传输模块,用于传输数据读写控制模块接收到的数据或者从存储模块读出的数据;

缓冲器,用于在数据读写控制模块对接收到的数据写入存储模块的传输过程中增加驱动。

超大规模FPGA的控制结构包括多个区域,具体参见图4所示,401、402、403、403分别为region1、region2、region3、region4。需要说明的是,本实施例中超大规模FPGA划分的区域数量仅用来对本发明进行说明,并非用于限定本发明。

本实施例是以一个区域内的配置存储器位线控制电路(参见图5所示)进行详细说明。

本实施例中,传输模块具体包括位线传输通道,缓冲器按照预设距离设置于位线传输通道上。应当理解,位线传输通道上存在有寄生电阻电容,为了避免对正常写入数据产生影响,在位线传输通道上每隔一段距离设置一个双缓冲器以保证在两个缓冲器之间的寄生电阻电容不超过能正常写入数据的寄生电阻电容。在本实施例的一些应用场景中,预设距离可以根据电路最大寄生电阻电容来确定;需要说明的是最大寄生电阻电容需要根据具体的工艺进行具体判定。

本实施例中,缓冲器buffer为双向的;缓冲器多用在总线上,用来提高驱动能力、隔离前后级,因此多半有三态输出功能。具体的,当负载不具有非选通输出为高阻特性时,将起到隔离作用;当总线的驱动能力不够驱动负载时,将起到驱动作用。

本实施例中,数据读写控制模块具体包括写字线控制电路、写驱动电路及读配套电路;写驱动电路可以根据接收到的数据产生BL信号,BL信号分别往左往右传输;写字线控制电路将BL信号写入存储模块;读配套电路读出存储模块中的数据,这样可以支持FPGA在横向上的扩展设计。

具体的参见图5所示,写驱动电路接收到的数据是由CCS内帧数据输入寄存器输入的,接收到的数据通过写驱动电路,产生分别往左往右传输的BL信号,本实施例中BL信号为3232位BL信号。本实施例中,在位线传输通道上每隔一段距离插入一个双向buffer 501以保证在两个buffer之间的寄生电阻电容不超过能正常写入数据的寄生电阻电容;写字线控制电路将BL信号写入存储模块。

本实施例中,存储模块可以为配置存储器,包括但不限于CRAM。

配置存储器的电路图参见图6所示,包括相互连接的MOS管和反相器,具体的,MOS管包括第一MOS管MN1和第二MOS管MN2,反相器包括第一反相器I1和第二反相器I2,第一MOS管MN1和第二MOS管MN2进行串联连接,第一反相器I1和第二反相器I2并行连接并设置于第一MOS管MN1和第二MOS管MN2之间。MN1和MN2的栅极连接电压,为电源电压ADDR,也为字线信号;MN1源极所接电压为ADDR为1时写入的data信号值,MN1漏极连接并行连接的I1和I2一端;MN2源极连接并行连接的I1和I2的另一端,MN2漏极所接电压为datan;I2一端所接电压为ADDR为1时读出的q信号值,I2另一端所接电压为qb。

本实施例中,位线控制电路所处的状态包括写入状态和回读状态,具体的,在写入数据时,通过写字线控制电路及写驱动电路,在配置存储器的ADDR为1时写入data信号的值。读数据时,通过读配套电路,如预充电电路、灵敏放大电路等及读字线控制电路,在配置存储器的ADDR为1时读出q信号的值。需要说明的是,在向配置存储器中写数据时需要通过data放电至低电平,如果在ADDR开启的时间内data不能放电至低电平,则写入数据失效;而data放电后最终的低电平电压值由写数据通路中的相关电阻分压决定。

本实施例中,通过图5所示的配置存储器位线控制电路,可以将配置位流即3,232位BL信号在字线信号ADDR为1时写入可编程逻辑模块502内的配置存储器中,实现具体的功能。

本实施例提供的配置存储器位线控制电路,配置存储器位线控制电路包括数据读写控制模块、存储模块、传输模块以及缓冲器,数据控制读写模块根据位线控制电路所处的状态以及信号将接收到的数据写入存储模块或者将存储模块中的数据进行读出,在数据控制读写模块对接收到的数据写入存储模块的传输过程中增加驱动;这样在超大规模FPGA电路中,同一个region内由于寄生电阻电容影响,一定距离范围内添加位线驱动的双向buffer,从而支持在超大规模FPGA横向上进行扩展设计,提高了系统可扩展性,缩短了新产品面世的时间,降低产品的研发成本。

实施例二:

基于上述实施例,本实施例提供了一种FPGA位线控制系统,包括:配置寄存器、可编程逻辑模块以及配置存储器位线控制电路;配置寄存器用于配置帧地址并将帧地址数据与数据输出到配置存储器位线控制电路;配置存储器位线控制电路,用于在进行写入操作时,将数据写到与地址对应的存储模块中;在进行读出操作时,根据地址将对应的存储模块中的数据读出。

本实施例中,可编程逻辑模块包括至少一个区域,每个区域内设置有配置存储器位线控制电路,配置存储器位线控制电路在上述实施例已进行详细说明,此处不再赘述。

配置寄存器包括帧地址寄存器、帧数据输入寄存器以及帧数据输出寄存器,配置存储器位线控制电路还包括帧地址数据转换模块;

帧地址寄存器用于配置帧地址并将帧地址数据发送给帧地址数据转换模块;

帧数据输入寄存器用于将数据输出到数据读写控制模块;

数据读写控制模块,用于将数据通过缓冲器写到与地址对应的存储模块中以及根据地址从存储模块中读出数据并将读出的数据发送到帧数据输入寄存器;

帧数据输入寄存器,还用于接收数据读写控制模块从存储模块中读出的数据;

数据读写控制模块,还用于从帧数据输入寄存器读出数据内容,并将读出的数据内容发送给帧数据输出寄存器。

本实施例中,配置存储器位线控制电路包括配置存储器和配置存储器接口,配置存储器与存储模块对应,数据读写控制模块设置于配置存储器接口内。

本实施例中,超大规模FPGA的控制结构包括多个区域,因此FPGA位线控制系统还包括至少一个多级缓冲器以及至少一个两级与非门;

多级缓冲器,用于接收帧数据输入寄存器输入的数据并将数据发送至对应区域内的配置存储器位线控制电路;

两级与非门,用于在回读时将读出的数据输出到帧数据输出寄存器。

本实施例中,多级缓冲器由至少两个缓冲器串联组成,两级与非门由至少两个与非门串联组成,缓冲器之间、与非门之间以及缓冲器与region之间、与非门与region之间的具体连接方式参见图7所示。

图7为FPGA系统中多个区域之间的位线控制信号及帧数据输入输出的数据传递示意图。

如图所示,CCS中帧数据输入寄存器输出的帧数据输入信号通过多级缓冲器buffer分别送进每个region的配置存储器位线控制电路;进行回读时,帧数据输出信号在每一个region内通过两级与非门与相邻的region回读信号及控制信号601、603、604、605等控制,并将最终的输出的信号传输到CCS内部的帧数据输出寄存器内,本实施例这,602初始为1。通过这个结构可完成全芯片的配置位流写入及回读功能。

本实施例提供的FPGA位线控制系统,帧数据输入信号通过多级缓冲器buffer分别送进每个region的配置存储器位线控制电路以及回读时帧数据输出信号通过两级与非门与相邻的region回读信号及控制信号进行控制输出帧数据输出信号;实现了在超大规模FPGA电路中,多个region之间信号传递及连接,进而支持在纵向上继续增加region进行扩展设计,提高了系统可扩展性,缩短了新产品面世的时间,降低产品的研发成本。

以上内容是结合具体的实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本发明的保护范围。

- 配置存储器位线控制电路以及FPGA位线控制系统

- 用于在形成快闪存储器装置期间形成位线触点及位线的方法,及包括所述位线及位线触点的装置