超结器件及其制造方法

文献发布时间:2023-06-19 11:06:50

技术领域

本发明涉及半导体集成电路制造领域,特别是涉及一种超结(super junction)器件;本发明还涉及一种超结器件的制造方法。

背景技术

超结器件如超结MOSFET是在现有VDMOS基础上,在纵向的漂移区中插入横向的P型柱。利用P型柱和N型漂移区的横向耗尽,从而在不降低击穿电压的情况下,可以大幅提高漂移区的掺杂浓度,因此可以打破硅器件的一维理论极限。获得更低的比导通电阻。更重要的是,超结器件的比导通电阻的极限值正比于P型柱之间的距离,P型柱之间的距离更近超结器件的比导通电阻更低。这样提供了不断优化器件性能的方向。

目前实现超结结构的P型柱的主要由以下两种方法:

一种是基于多次外延的技术,另外一种是基于深槽刻蚀和P型硅填入工艺。目前这两种技术都是市场上的主流。

通常认为多次外研技术所形成的的器件,它的寄生体二极管反向恢复的软度因子要优于基于深槽刻蚀和P型硅填入工艺的器件。其栅漏耦合电容随偏压的变化也跟采用深槽刻蚀相比,更加的平缓。一个比较重要的原因是多次外延形成了很多类似于葫芦圈的结构,葫芦圈之间的连接部位,P型柱宽度是比较窄的。如图1所示,是现有基于外延技术的超结结构的仿真图;N型柱101是由多次外延工艺形成,P型柱102是由各次外延工艺完成后通过离子注入形成,可以看出,P型柱102的各层外延层对应的离子注入区之间的连接处会变窄,纵向上看,P型柱102呈葫芦圈结构。因为这个葫芦圈结构的原因可以让超结器件其寄生体二极管在反向恢复的过程中多存贮一定的空穴,从而提高反向恢复过程中的软度因子。此外,这也导致栅漏耦合电容随偏压的变化更加的平缓,从而有利于降低在开关过程中的过冲,有利于降低电磁干扰(Electromagnetic Interference,EMI)。

发明内容

本发明所要解决的技术问题是提供一种超结器件,能增加器件的反向恢复的软度因子,能使栅漏电容随偏压变化更加平缓,能有效降低器件在应用电路中的电磁干扰性能以及有效降低器件在应用电路中带来的电流和电压的过冲。为此,本发明还提供一种超结器件的制造方法。

为解决上述技术问题,本发明提供的超结器件包括由多个交替排列的第一导电类型柱和第二导电类型型柱组成的超结结构;每一所述第一导电类型柱和其邻近的所述第二导电类型柱组成一个超结单元。

所述超结结构包括至少一个由第一超结子结构和第二超结子结构纵向叠加而成的第三超结子结构。

所述第一超结子结构由形成于具有第二导电类型的第一外延子层中的第一导电类型子柱一和第二导电类型子柱一交替排列而成。

所述第二超结子结构由形成于具有第一导电类型的第二外延子层中的第一导电类型子柱二和第二导电类型子柱二交替排列而成。

在所述第一外延子层中形成有第一沟槽,所述第一沟槽具有顶部宽度大于底部宽度的侧面倾斜结构;所述第一沟槽穿过所述第一外延子层;所述第一导电类型子柱一由填充于所述第一沟槽中的第一导电类型外延层组成,所述第二导电类型子柱一由位于所述第一导电类型子柱一之间的所述第一外延子层组成。

所述第二外延子层叠加在形成有所述第一导电类型子柱一和所述第二导电类型子柱一的所述第一外延子层的表面上。

在所述第二外延子层中形成有第二沟槽,所述第二沟槽具有顶部宽度大于底部宽度的侧面倾斜结构;所述第二沟槽穿过所述第二外延子层;所述第二导电类型子柱二由填充于所述第二沟槽中的第二导电类型外延层组成,所述第一导电类型子柱二由位于所述第二导电类型子柱二之间的所述第二外延子层组成。

所述第三超结子结构的第一导电类型子柱三由所述第一导电类型子柱一和所述第一导电类型子柱二纵向叠加而成并使所述第一导电类型子柱三具有中间宽度比顶部宽度和底部宽度都大的结构。

所述第三超结子结构的第二导电类型子柱三由所述第二导电类型子柱一和所述第二导电类型子柱二纵向叠加而成并使所述第二导电类型子柱三具有中间宽度比顶部宽度和底部宽度都小的结构。

进一步的改进是,所述超结结构由一个所述第三超结子结构组成;或者,所述超结结构由两个以上的所述第三超结子结构纵向叠加而成。

进一步的改进是,所述超结结构的底部形成有第一导电类型掺杂的缓冲层。

所述缓冲层形成于半导体衬底上。

进一步的改进是,所述第一沟槽的底部表面比所述第一外延子层的底部表面低0微米~2微米;所述第二沟槽的底部表面比所述第二外延子层的底部表面低0微米~2微米。

进一步的改进是,所述第一沟槽的侧面倾角为88度~89度;所述第二沟槽的侧面倾角为88度~89度。

进一步的改进是,所述超结单元在纵向上各位置处的所述第一导电类型柱和所述第二导电类型柱的宽度和保持不变。

进一步的改进是,超结器件由多个器件单元结构并联而成,各所述器件单元结构形成在对应的所述超结单元上。

各所述器件单元结构包括栅极结构、体区和源区。

进一步的改进是,所述栅极结构为平面栅;或者,所述栅极结构为沟槽栅。

为解决上述技术问题,本发明提供的超结器件的制造方法中包括由多个交替排列的第一导电类型柱和第二导电类型型柱组成的超结结构;每一所述第一导电类型柱和其邻近的所述第二导电类型柱组成一个超结单元;所述超结结构的形成步骤至少包括:

步骤一、形成具有第二导电类型的第一外延子层。

步骤二、采用光刻加刻蚀工艺在所述第一外延子层中形成多个第一沟槽,所述第一沟槽具有顶部宽度大于底部宽度的侧面倾斜结构;所述第一沟槽穿过所述第一外延子层。

步骤三、在所述第一沟槽中填充第一导电类型外延层并组成第一导电类型子柱一,由位于所述第一导电类型子柱一之间的所述第一外延子层组成第二导电类型子柱一。

由所述第一导电类型子柱一和所述第二导电类型子柱一交替排列形成第一超结子结构。

步骤四、在形成有所述第一导电类型子柱一和所述第一导电类型子柱二的所述第一外延子层的表面上形成具有第一导电类型的第二外延子层。

步骤五、采用光刻加刻蚀工艺在所述第二外延子层中形成多个第二沟槽,所述第二沟槽具有顶部宽度大于底部宽度的侧面倾斜结构;所述第二沟槽穿过所述第二外延子层。

步骤六、在所述第二沟槽中填充第二导电类型外延层并组成第二导电类型子柱二,由位于所述第二导电类型子柱二之间的所述第二外延子层组成第一导电类型子柱二。

由所述第一导电类型子柱二和所述第二导电类型子柱二交替排列形成第二超结子结构。

由第一超结子结构和第二超结子结构纵向叠加形成第三超结子结构;所述超结结构包括至少一个所述第三超结子结构。

所述第三超结子结构的第一导电类型子柱三由所述第一导电类型子柱一和所述第一导电类型子柱二纵向叠加而成并使所述第一导电类型子柱三具有中间宽度比顶部宽度和底部宽度都大的结构。

所述第三超结子结构的第二导电类型子柱三由所述第二导电类型子柱一和所述第二导电类型子柱二纵向叠加而成并使所述第二导电类型子柱三具有中间宽度比顶部宽度和底部宽度都小的结构。

进一步的改进是,所述超结结构由一个所述第三超结子结构组成;或者,所述超结结构由两个以上的所述第三超结子结构纵向叠加而成;每一个所述第三超结子结构都需要重复一次步骤一至步骤六。

进一步的改进是,所述超结结构的底部形成有第一导电类型掺杂的缓冲层。

所述缓冲层形成于半导体衬底上。

进一步的改进是,所述第一沟槽的底部表面比所述第一外延子层的底部表面低0微米~2微米;所述第二沟槽的底部表面比所述第二外延子层的底部表面低0微米~2微米。

所述第一沟槽的侧面倾角为88度~89度;所述第二沟槽的侧面倾角为88度~89度。

进一步的改进是,所述超结单元在纵向上各位置处的所述第一导电类型柱和所述第二导电类型柱的宽度和保持不变。

进一步的改进是,超结器件由多个器件单元结构并联而成,各所述器件单元结构形成在对应的所述超结单元上。

各所述器件单元结构包括栅极结构、体区和源区。

所述栅极结构为平面栅;或者,所述栅极结构为沟槽栅。

进一步的改进是,第一导电类型为N型,第二导电类型为P型;或者,第一导电类型为P型,第二导电类型为N型。

本发明通过在超结结构中设置第三超结子结构,而第三超结子结构则由第一超结子结构和第二超结子结构叠加而成,和现有技术中纵向叠加的超结子结构都是沟槽和沟槽对齐不同,本发明的第三超结子结构中第一超结子结构的第一沟槽和第二超结子结构的第二沟槽正好错开,这样,使得第三超结子结构的第一导电类型子柱三和第二导电类型子柱三都分别为一个外延子层和一个沟槽填充的外延层叠加而成,由于沟槽都是具有顶部宽底部窄的侧面倾斜结构,由于超结单元的步进相同,同一层的沟槽之间的外延子层则具有顶部窄底部宽的结构,故在纵向上外延子层位于底部和沟槽位于顶部的叠加结构具有中间窄顶部和底部宽的结构即第二导电类型子柱三所具有的结构,而在纵向上外延子层位于顶部和沟槽位于底部的叠加结构具有中间宽顶部和底部窄的结构即第一导电类型子柱三所具有的结构,这样在第三超结子结构的中间位置处会出现第一导电类型子柱三和第二导电类型子柱三具有较大的宽度差异,这种宽度差异有利于器件在反向恢复过程中提供载流子,从而能能增加器件的反向恢复的软度因子;同时也能使栅漏电容随偏压变化更加平缓,能有效降低器件在应用电路中的电磁干扰性能以及有效降低器件在应用电路中带来的电流和电压的过冲。

附图说明

下面结合附图和具体实施方式对本发明作进一步详细的说明:

图1是现有基于外延技术的超结结构的仿真图;

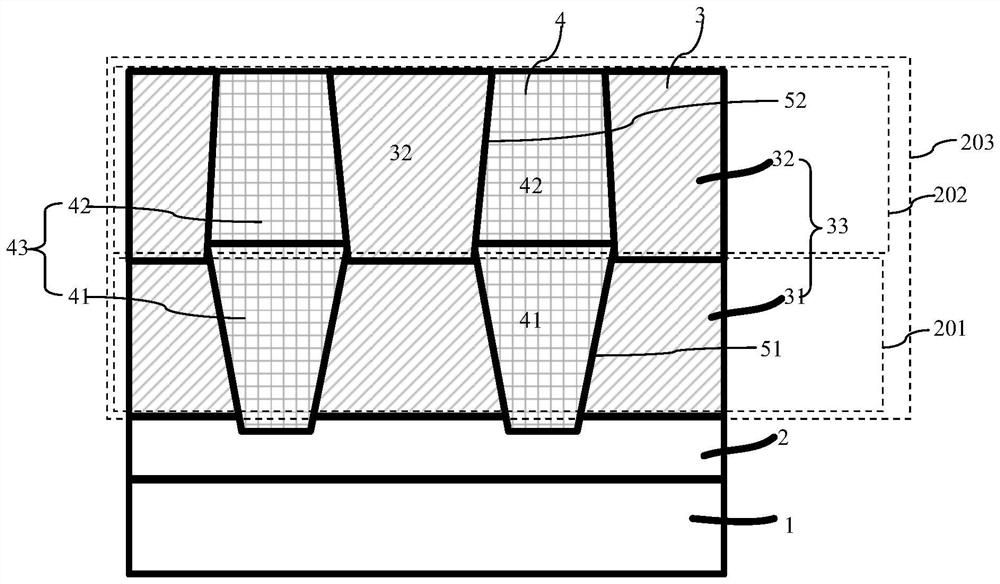

图2是本发明第一实施例超结器件的超结结构的示意图;

图3本发明第一实施例超结器件的示意图;

图4是本发明实施例一超结器件的栅漏电容(Cgd)随漏极电压的变化曲线;

图5是本发明第二实施例超结器件的超结结构的示意图;

图6A-图6E是本发明第一实施例超结器件的制造方法各步骤中的器件结构示意图。

具体实施方式

本发明第一实施例超结器件:

如图2所示,是本发明第一实施例超结器件的超结结构的示意图;如图3所示,本发明第一实施例超结器件的示意图;本发明第一实施例超结器件包括由多个交替排列的第一导电类型柱4和第二导电类型型柱3组成的超结结构;每一所述第一导电类型柱4和其邻近的所述第二导电类型柱3组成一个超结单元。

所述超结结构包括至少一个由第一超结子结构201和第二超结子结构202纵向叠加而成的第三超结子结构203。

所述第一超结子结构201由形成于具有第二导电类型的第一外延子层31中的第一导电类型子柱一41和第二导电类型子柱一31交替排列而成。本发明第一实施例中,所述第二导电类型子柱一31是由第一外延子层31组成的,故二者都采用标记31表示。

所述第二超结子结构202由形成于具有第一导电类型的第二外延子层42中的第一导电类型子柱二42和第二导电类型子柱二32交替排列而成。本发明第一实施例中,所述第一导电类型子柱二42是由第二外延子层42组成的,故二者都采用标记42表示。

在所述第一外延子层31中形成有第一沟槽51,所述第一沟槽51具有顶部宽度大于底部宽度的侧面倾斜结构;所述第一沟槽51穿过所述第一外延子层31;所述第一导电类型子柱一41由填充于所述第一沟槽51中的第一导电类型外延层组成,所述第二导电类型子柱一31由位于所述第一导电类型子柱一41之间的所述第一外延子层31组成。

所述第二外延子层42叠加在形成有所述第一导电类型子柱一41和所述第二导电类型子柱一31的所述第一外延子层31的表面上。

在所述第二外延子层42中形成有第二沟槽52,所述第二沟槽52具有顶部宽度大于底部宽度的侧面倾斜结构;所述第二沟槽52穿过所述第二外延子层42;所述第二导电类型子柱二32由填充于所述第二沟槽52中的第二导电类型外延层组成,所述第一导电类型子柱二42由位于所述第二导电类型子柱二32之间的所述第二外延子层42组成。

所述第三超结子结构203的第一导电类型子柱三43由所述第一导电类型子柱一41和所述第一导电类型子柱二42纵向叠加而成并使所述第一导电类型子柱三43具有中间宽度比顶部宽度和底部宽度都大的结构。

所述第三超结子结构203的第二导电类型子柱三33由所述第二导电类型子柱一31和所述第二导电类型子柱二32纵向叠加而成并使所述第二导电类型子柱三33具有中间宽度比顶部宽度和底部宽度都小的结构。

本发明第一实施例中,所述超结结构由一个所述第三超结子结构203组成,也即:所述第一导电类型柱4直接由所述第一导电类型子柱三43组成,所述第二导电类型型柱3直接由所述第二导电类型子柱二32组成。

所述超结结构的底部形成有第一导电类型掺杂的缓冲层2。

所述缓冲层2形成于半导体衬底1上。

所述第一沟槽51的底部表面比所述第一外延子层31的底部表面低0微米~2微米;所述第二沟槽52的底部表面比所述第二外延子层42的底部表面低0微米~2微米。

所述第一沟槽51的侧面倾角为88度~89度;所述第二沟槽52的侧面倾角为88度~89度。

所述超结单元在纵向上各位置处的所述第一导电类型柱4和所述第二导电类型柱3的宽度和保持不变。

超结器件由多个器件单元结构并联而成,各所述器件单元结构形成在对应的所述超结单元上。图3中显示了一个所述超结单元。各所述器件单元结构包括栅极结构、体区7和源区8。

图3中,所述栅极结构为平面栅;所述栅极结构包括依次叠加的栅介质层5和多晶硅栅6。在其他实施例中也能为:所述栅极结构为沟槽栅。

所述体区7形成在所述第二导电类型柱3的顶部并延伸到所述第一导电类型柱4中。

所述栅极结构覆盖在体区7的表面以及相邻的两个所述体区7之间的所述第一导电类型柱4的表面上。被所述多晶硅栅6所覆盖的所述体区7的表面用于形成沟道。

所述源区8形成于所述体区7并和所述多晶硅栅6对应的侧面自对准。

所述源区8具有第一导电类型重掺杂,所述体区7具有第二导电类型掺杂。在所述体区7中还形成有第二导电类型重掺杂的体引出区9,体引出区9为第二导电类型载流子的收集区。

所述半导体衬底1背面减薄后进行第一导电类型重掺杂形成漏区。

在所述体区7之间的所述第一导电类型柱4的表面还形成JFET注入区10。

本发明第一实施例中,超结器件为N型器件,第一导电类型为N型,第二导电类型为P型。在其他实施例中也能为:超结器件为P型器件,第一导电类型为P型,第二导电类型为N型。

现结合具体参数来说明本发明第一实施例超结器件:

所述多晶硅栅6的厚度通常在

所述栅介质层5通常为栅氧化层如二氧化硅层,所述栅介质层5的厚度决定了栅极结构的耐压,其耐压正比于所述栅介质层5的厚度。所述栅介质层5的厚度也决定了阈值电压,所述栅介质层5的厚度越厚,阈值电压越高。对于超结MOSFET,通常要求其阈值电压大于3V,因此所述栅介质层5的厚度通常需要大于

所述源区8的掺杂的剂量通常是在1e15/cm

所述体区7的掺杂剂量通常是在5e13/cm

漂移区主要由所述第一导电类型柱4组成,所述漂移区的掺杂的体浓度通常是在1e15/cm

所述JFET注入区10的掺杂浓度使JFET注入区10处的掺杂浓度和其他区域的漂移区的掺杂浓度相比会增加10倍以上。

所述半导体衬底1能为硅衬底,所述半导体衬底1的电阻率通常为1mΩ*cm附近。所述半导体衬底1的电阻率越低越好,所述半导体衬底1的厚度越薄越好,以降低衬底电阻。

所述缓冲层2的厚度越厚对器件的鲁棒性有帮助。此外所述缓冲层2的厚度越厚在反向恢复的过程中可以存贮多余的空穴,有利于提高反向恢复的软度因子。但是这是以牺牲比导通电阻为代价的。

所述第一导电类型柱4的厚度正比于器件的击穿电压。对于600V的超结MOSFET,所述第一导电类型柱4的厚度通常为40μm,对于900V的超结MOSFET器件,所述第一导电类型柱4的厚度通常为60μm。

所述第二导电类型柱3跟现有基于深槽刻蚀形成的P型柱不同,它是上面宽中间窄下面宽。而现有深槽刻蚀形成的P柱都是上面宽下面窄,是不能形成所述第二导电类型柱3的形貌的。注意,理论上我们都希望深槽刻蚀的角度是垂直的,但是实际工艺中,深槽刻蚀的角度都是倾斜的,有一定的倾斜角度,即第一沟槽51和第二沟槽52的侧面都为倾斜结构。

采用本发明第一实施例超结器件结构,利用TCAD仿真,可以实现:比导通电阻为1.2Ω*cm2,对应的击穿电压达到800V。对于一个导通电阻典型值为30mΩ的超结MOSFET,其栅漏电容随漏压的变化如图4所示,曲线301表示本发明实施例一超结器件的栅漏电容随漏极电压的变化曲线,可以看到Cgd随漏极电压的变化变得比较平缓。

本发明第一实施例通过在超结结构中设置第三超结子结构203,而第三超结子结构203则由第一超结子结构201和第二超结子结构202叠加而成,和现有技术中纵向叠加的超结子结构都是沟槽和沟槽对齐不同,本发明第一实施例的第三超结子结构203中第一超结子结构201的第一沟槽51和第二超结子结构202的第二沟槽52正好错开,这样,使得第三超结子结构203的第一导电类型子柱三43和第二导电类型子柱三33都分别为一个外延子层和一个沟槽填充的外延层叠加而成,由于沟槽都是具有顶部宽底部窄的侧面倾斜结构,由于超结单元的步进相同,同一层的沟槽之间的外延子层则具有顶部窄底部宽的结构,故在纵向上外延子层位于底部和沟槽位于顶部的叠加结构具有中间窄顶部和底部宽的结构即第二导电类型子柱三33所具有的结构,而在纵向上外延子层位于顶部和沟槽位于底部的叠加结构具有中间宽顶部和底部窄的结构即第一导电类型子柱三43所具有的结构,这样在第三超结子结构203的中间位置处会出现第一导电类型子柱三43和第二导电类型子柱三33具有较大的宽度差异,这种宽度差异有利于器件在反向恢复过程中提供载流子,从而能能增加器件的反向恢复的软度因子;同时也能使栅漏电容随偏压变化更加平缓,能有效降低器件在应用电路中的电磁干扰性能以及有效降低器件在应用电路中带来的电流和电压的过冲。

本发明第二实施例超结器件:

如图5所示,是本发明第二实施例超结器件的超结结构的示意图;本发明第二实施例超结器件和本发明第一实施例超结器件的区别之处为,本发明第二实施例超结器件中具有如下特征:

所述超结结构由两个以上的所述第三超结子结构203纵向叠加而成。多层所述第三超结子结构203的叠加结构能在保持每一层的沟槽的刻蚀和填充的难度不变的条件下增加整个所述超结结构的厚度;或者能在保证所述超结结构的厚度不变的条件下降低各层沟槽的刻蚀和填充的难度。

本发明第一实施例超结器件的制造方法:

如图6A至图6E所示,是本发明第一实施例超结器件的制造方法各步骤中的器件结构示意图。本发明第一实施例超结器件的制造方法中包括由多个交替排列的第一导电类型柱4和第二导电类型型柱3组成的超结结构;每一所述第一导电类型柱4和其邻近的所述第二导电类型柱3组成一个超结单元;所述超结结构的形成步骤至少包括:

步骤一、如图6A所示,提供半导体衬底1,在半导体衬底1上形成第一导电类型掺杂的缓冲层2。

如图6B所示,形成具有第二导电类型的第一外延子层31。

步骤二、如图6C所示,采用光刻加刻蚀工艺在所述第一外延子层31中形成多个第一沟槽51,所述第一沟槽51具有顶部宽度大于底部宽度的侧面倾斜结构;所述第一沟槽51穿过所述第一外延子层31。

所述第一沟槽51的底部表面比所述第一外延子层31的底部表面低0微米~2微米。

所述第一沟槽51的侧面倾角为88度~89度。

步骤二主要包括如下分步骤:

形成硬质掩膜层401。

之后,采用光刻工艺定义出所述第一沟槽51的形成区域。

依次对所述硬质掩膜层401和所述第一外延子层31进行刻蚀形成所述第一沟槽51。

所述硬质掩膜层401可以在形成所述第一沟槽51之后去除;也能在后续步骤三形成所述第一导电类型柱一41之后再去除。

步骤三、如图6D所示,在所述第一沟槽51中填充第一导电类型外延层并组成第一导电类型子柱一41,由位于所述第一导电类型子柱一41之间的所述第一外延子层31组成第二导电类型子柱一31。

由所述第一导电类型子柱一41和所述第二导电类型子柱一31交替排列形成第一超结子结构201。

步骤四、如图6E所示,在形成有所述第一导电类型子柱一41和所述第一导电类型子柱二42的所述第一外延子层31的表面上形成具有第一导电类型的第二外延子层42。

步骤五、如图6E所示,采用光刻加刻蚀工艺在所述第二外延子层42中形成多个第二沟槽52,所述第二沟槽52具有顶部宽度大于底部宽度的侧面倾斜结构;所述第二沟槽52穿过所述第二外延子层42。

所述第二沟槽52的底部表面比所述第二外延子层42的底部表面低0微米~2微米。所述第二沟槽52的侧面倾角为88度~89度。

步骤五主要包括如下分步骤:

形成硬质掩膜层402。

之后,采用光刻工艺定义出所述第二沟槽52的形成区域。

依次对所述硬质掩膜层402和所述第二外延子层42进行刻蚀形成所述第二沟槽52。

所述硬质掩膜层402可以在形成所述第二沟槽52之后去除;也能在后续步骤六形成所述第二导电类型子柱二32之后再去除。

步骤六、如图2所示,在所述第二沟槽52中填充第二导电类型外延层并组成第二导电类型子柱二32,由位于所述第二导电类型子柱二32之间的所述第二外延子层42组成第一导电类型子柱二42。

由所述第一导电类型子柱二42和所述第二导电类型子柱二32交替排列形成第二超结子结构202。

由第一超结子结构201和第二超结子结构202纵向叠加形成第三超结子结构203;所述超结结构包括至少一个所述第三超结子结构203。

所述第三超结子结构203的第一导电类型子柱三43由所述第一导电类型子柱一41和所述第一导电类型子柱二42纵向叠加而成并使所述第一导电类型子柱三43具有中间宽度比顶部宽度和底部宽度都大的结构。

所述第三超结子结构203的第二导电类型子柱三33由所述第二导电类型子柱一31和所述第二导电类型子柱二32纵向叠加而成并使所述第二导电类型子柱三33具有中间宽度比顶部宽度和底部宽度都小的结构。

本发明第一实施例方法,所述超结结构由一个所述第三超结子结构203组成。

所述超结单元在纵向上各位置处的所述第一导电类型柱4和所述第二导电类型柱3的宽度和保持不变。

本发明第一实施例中,超结器件为N型器件,第一导电类型为N型,第二导电类型为P型。在其他实施例中也能为:超结器件为P型器件,第一导电类型为P型,第二导电类型为N型。

现结合具体参数来说明本发明第一实施例方法的超结结构的各制造步骤:

步骤一中,所述半导体衬底1为N型高掺杂的硅衬底,通常采用砷掺杂,电阻率的典型值在2mΩ*cm。

所述缓冲层2的电阻率为0.8Ω*cm,对应的厚度为10微米。所述缓冲层2为硅外延层。

所述第一外延子层31的厚度是20微米,对应的电阻率是2.2Ω*cm。所述第一外延子层31为硅外延层。

步骤二中,所述硬质掩膜层401通常是氧化层,也能为ONO结构即氧化层、氮化层和氧化层的叠加结构。因为进行所述第一沟槽51的硅刻蚀的时候,刻蚀液也会刻蚀所述硬质掩膜层401,所以所述硬质掩膜层401的厚度需要足够厚。所述第一沟槽51的开口为6微米,开口之间的间距(Space)是3微米,故步进为9微米。所述第一沟槽51的深度为22微米。比所述第一外延子层31的厚度要大2微米,这是需要保证即使工艺发生一定的变化时所述第一沟槽51也可以完全穿过所述第一外延子层31,工艺变化如所述第一外延子层31厚度的变化,所述第一沟槽51的刻蚀深度的变化以及面内的均匀性变化。

步骤三中,所述第一导电类型子柱一41的N型杂质填入的剂量是跟所述第一沟槽51刻蚀的角度有关,需要保证P型杂质的剂量和N型杂质的总剂量的相匹配。在实际工艺中,为了保证填入过程中没有缺陷,所述第一沟槽51刻蚀的角度通常在88~89度之间。所述第一沟槽51刻蚀的角度越接近于理想(垂直状态),N型杂质的剂量也越淡。在所述第一导电类型子柱一41的外延填充完成之后通常还需要进行化学机械研磨(CMP)工艺。这样形成的所述第一导电类型子柱一41顶部的开口宽度是3微米,底部宽度为4微米,这时因为所述第一沟槽51刻蚀的角度倾斜使底部宽度增加,形成了下面宽上面窄的形貌。

步骤四中形成的所述第二外延子层42的掺杂浓度为1.2Ω*cm,对应的厚度为20微米。接着沉积一层硬质掩膜层402。硬质掩膜层402的开口为4微米,开口之间的距离为5微米。对硬质掩膜层402进行刻蚀,刻蚀完以后利用硬质掩膜层402作为阻挡层,继续刻蚀硅。刻蚀的深度为22微米。

接着进行步骤六的第二导电类型子柱二32的P型杂质外延填充,之后再进行CMP。

从上可知,本发明第一实施例方法形成的P型柱即所述第二导电类型柱3是由两段组成:最下面一段P型子柱即所述第二导电类型子柱一31,是由P型外延层组成;上面一段P型子柱即所述第二导电类型子柱二32是由深槽刻蚀以后,由P型外延层填入形成的。因此,其形状可以组成顶部开口大,两端连接的地方开口小,底部开口大。

同样,N型漂移区即所述第一导电类型柱4也是由两段组成:其中最下面一段是由深槽刻蚀后的N型硅填入组成,上面一段是由N型外延层组成的。

形成所述超结结构之后,再在所述超结结构的表面形成所述超结器件的各器件单元结构。超结器件由多个器件单元结构并联而成,各所述器件单元结构形成在对应的所述超结单元上。图3中显示了一个所述超结单元。各所述器件单元结构包括栅极结构、体区7和源区8。

图3中,所述栅极结构为平面栅;所述栅极结构包括依次叠加的栅介质层5和多晶硅栅6。在其他实施例中也能为:所述栅极结构为沟槽栅。

所述体区7形成在所述第二导电类型柱3的顶部并延伸到所述第一导电类型柱4中。

所述栅极结构覆盖在体区7的表面以及相邻的两个所述体区7之间的所述第一导电类型柱4的表面上。被所述多晶硅栅6所覆盖的所述体区7的表面用于形成沟道。

所述源区8形成于所述体区7并和所述多晶硅栅6对应的侧面自对准。

所述源区8具有第一导电类型重掺杂,所述体区7具有第二导电类型掺杂。在所述体区7中还形成有第二导电类型重掺杂的体引出区9,体引出区9为第二导电类型载流子的收集区。

所述半导体衬底1背面减薄后进行第一导电类型重掺杂形成漏区。

在所述体区7之间的所述第一导电类型柱4的表面还形成JFET注入区10。

本发明第二实施例超结器件的制造方法:

本发明第二实施例超结器件的制造方法和本发明第一实施例超结器件的制造方法的区别之处为,本发明第二实施例超结器件的制造方法中具有如下特征:

所述超结结构由两个以上的所述第三超结子结构203纵向叠加而成;每一个所述第三超结子结构203都需要重复一次步骤一至步骤六。图5中显示了所述超结结构由两个所述第三超结子结构203纵向叠加而成,故总共需要做两次步骤一至步骤六;如果叠加结构中需要更多层的所述第三超结子结构203,则需要增加步骤一至步骤六的循环次数。

以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

- 超结器件的制造方法及超结器件

- 超结器件的制造方法及超结器件