电路板结构及其制造方法

文献发布时间:2023-06-19 11:49:09

本申请是中国发明专利申请(申请号:201611014475.1,申请日:2016年11月18日,发明名称:电路板结构及其制造方法)的分案申请。

技术领域

本发明涉及一种电路板,尤其涉及一种具有独立金属垫的电路板结构及其制造方法。

背景技术

现有电路板结构在成形金手指的时候,大致依循图1至图3所示的步骤,具体说明如下。如图1,在基板1a上成形有金属层2a,并且金属层2a包含待镀金区21a及非镀金区22a,而位于上述待镀金区21a两侧的非镀金区22a是以防焊层3a覆盖。如图2,在金属层2a的待镀金区21a上形成金层4a,并且上述金层4a包含有功能区块41a与无效区块42a。如图3,去除功能区块41a上侧的部分无效区块42a及非镀金区22a。

依上所述,现有电路板结构100a在金层4a的功能区块41a的相反两侧,还留有相连接的无效区块42a(如图3),并且现有电路板结构100a在图3的步骤中还必须去除已完成镀金的区块。因此,现有电路板结构100a显然产生许多不必要的贵金属(如:金)浪费。

于是,本发明人认为上述缺陷可改善,特潜心研究并配合科学原理的运用,终于提出一种设计合理且有效改善上述缺陷的本发明。

发明内容

本发明的目的在于提供一种电路板结构及其制造方法,用来有效地改善现有电路板结构所可能产生的缺失。

为达上述目的,本发明公开一种电路板结构,包括:一基板,包含有位于相反侧的一第一板面与一第二板面;一线路,设置于所述基板的所述第一板面;以及一独立金属垫,设置于所述基板的所述第一板面,所述独立金属垫与所述线路呈间隔设置且相互电性隔离;其中,所述独立金属垫包含有设置于所述第一板面的一接合部及形成于所述接合部上的一硬金层。

优选地,所述接合部包含有设置于所述第一板面的一铜层及连接所述铜层与所述硬金层的一镍层,所述铜层与所述线路具有相同的高度。

优选地,所述铜层侧壁未包覆于所述硬金层,并且所述铜层的宽度自邻近所述第一板面朝向远离所述第一板面逐渐地缩小。

优选地,所述硬金层的外侧部位凸伸出所述铜层。

优选地,所述电路板结构进一步包括有设置于所述第一板面的一防焊层,所述防焊层围绕于所述独立金属垫外侧,并且所述线路至少部分埋置于所述防焊层,而所述独立金属垫未接触于所述防焊层。

优选地,所述硬金层相较于所述第一板面的高度不小于所述防焊层相较于所述第一板面的高度。

本发明实施例也公开一种电路板结构制造方法,包括:提供一基板与设置于所述基板上的一导电层;其中,所述基板包含有位于相反侧的一第一板面与一第二板面,所述导电层设置于所述第一板面;在所述导电层的一预定区块上形成有一键结层及设置于所述键结层的一硬金层;以及将所述导电层蚀刻成所述预定区块及与所述预定区块相互分离的一线路;其中,所述预定区块、所述键结层、及所述硬金层合称为一独立金属垫。

优选地,在所述导电层上设置有一图案层;其中,所述图案层具有一图形孔,以裸露所述导电层的所述预定区块;在所述图形孔内的所述预定区块上依序成形所述键结层与所述硬金层,而后去除所述图案层。

优选地,在所述硬金层及所述导电层的一预定线路区块上形成一遮蔽层,并蚀刻未被所述遮蔽层所覆盖的所述导电层部位,以使所述导电层成形为所述预定区块及所述线路,而后去除所述遮蔽层。

优选地,所述电路板制造方法进一步包括:于所述第一板面形成一防焊层,并使所述防焊层围绕于所述独立金属垫外侧且将所述线路的至少部分埋置于其内。

综上所述,本发明实施例所公开的电路板结构及其制造方法,可无需移除任何硬金层而形成独立金属垫,并且所述独立金属垫不会连接任何无效区块,以避免电路板结构产生不必要的贵金属(如:金)浪费。

再者,由于本实施例的电路板结构在形成独立金属垫的过程中,无需如现有般以非镀金区作为待镀金区的导引,所以本实施例的电路板结构能够在基板上的任何位置形成有独立金属垫,进而使基板上的独立金属垫的外型、尺寸、位置、及密度,较不会受到限制,用于有效地促进电路板结构的发展。

为能更进一步了解本发明的特征及技术内容,请参阅以下有关本发明的详细说明与附图,但是此等说明与附图仅用来说明本发明,而非对本发明的保护范围作任何的限制。

附图说明

图1为现有电路板结构的制造步骤(一);

图2为现有电路板结构的制造步骤(二);

图3为现有电路板结构的制造步骤(三);

图4A为本发明电路板结构制造方法的步骤S110的示意图;

图4B为图4A沿IVB-IVB剖线的剖视示意图;

图5A为本发明电路板结构制造方法的步骤S120与步骤S130的示意图;

图5B为图5A沿VB-VB剖线的剖视示意图;

图6A为本发明电路板结构制造方法的步骤S140的示意图;

图6B为图6A沿VIB-VIB剖线的剖视示意图;

图7A为本发明电路板结构制造方法的步骤S150的示意图;

图7B为图7A沿VⅡB-VⅡB剖线的剖视示意图;

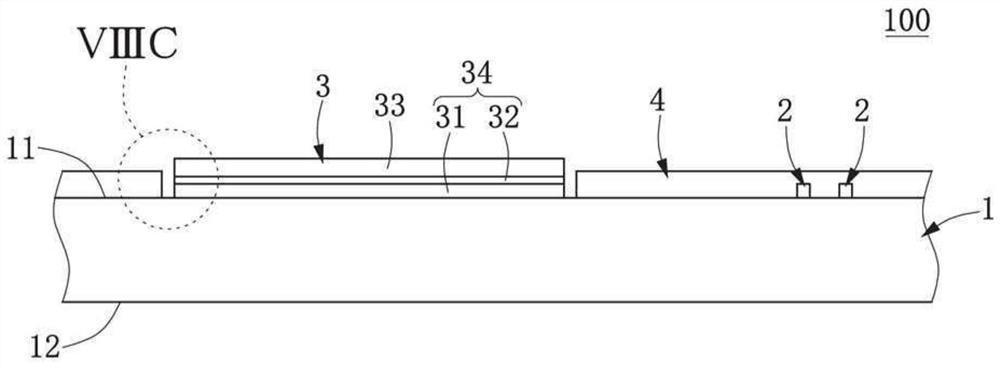

图8A为本发明电路板结构制造方法的步骤S160的示意图;

图8B为图8A沿VⅢB-VⅢB剖线的剖视示意图;

图8C为图8B中的VⅢC部位的局部放大示意图。

符号说明

[现有技术]

100a:现有电路板结构

1a:基板

2a:金属层

21a:待镀金区

22a:非镀金区

3a:防焊层

4a:金层

41a:功能区块

42a:无效区块

[本发明实施例]

100:电路板结构

1:基板

11:第一板面

12:第二板面

13:贯孔

2’:预定线路区块

2:线路

3:独立金属垫

31’:预定区块

31:铜层

32:键结层(镍层)

33:硬金层

34:接合部

4:防焊层

41:开孔

10:导电层

20:图案层

201:图形孔

30:遮蔽层

H1、H2:高度

具体实施方式

请参阅图4A至图8C,为本发明的实施例,需先说明的是,本实施例对应附图所提及的相关数量与外型,仅用来具体地说明本发明的实施方式,以便于了解本发明的内容,而非用来局限本发明的保护范围。

本实施例提供一种电路板结构100及其制造方法,上述电路板结构100例如是应用在伺服器或半导体测试等方面,但本发明不以此为限。再者,为便于理解本实施例,下述将先大致说明电路板结构制造方法的各个步骤(如:步骤S110~步骤S160),而后再接着介绍所述电路板结构100的构造特征。其中,在说明电路板结构制造方法的各个步骤时,附图仅以局部区块作为示意,此并非用以局限本发明的数量与实施范围。

步骤S110:请参阅图4A和图4B所示,提供一基板1与设置于所述基板1上的一导电层10。其中,所述基板1包含有位于相反侧的一第一板面11(如图4B中的基板1顶面)与一第二板面12(如图4B中的基板1底面),并且所述导电层10设置于上述基板1的第一板面11。

进一步地说,本实施例的导电层10是通过铜电镀方式成形于基板的整个第一板面11,但本发明不受限于此。举例来说,在一未绘示的实施例中,所述导电层10也可以是通过铜箔压合方式成形于基板1的第一板面11。

再者,本实施例的基板1也可以形成有自所述第一板面11贯穿至第二板面12的多个贯孔13,并于上述每个贯孔13内设有连接于所述导电层10的一导电材料(图中未示出),但本发明不以此为限。

步骤S120:请参阅图5A和图5B所示,在所述导电层10上设置有一图案层20。其中,所述图案层20具有一图形孔201,以裸露所述导电层10的一预定区块31’。

进一步地说,本实施例的图案层20是在导电层10上先贴附干膜,而后将上述干膜以曝光显影方式形成具有特定形状的图形孔201,用于使图形孔201能够露出设计者所需的特定形状的预定区块31’。其中,上述图案层20的成形过程中,较佳的环境条件为温度20℃~24℃、湿度50%~60%。因此,本实施例所采用的步骤S120可以依据设计者的不同需求,而实现各种形状的预定区块31’,用于跳脱现有金手指的长条状限制。

步骤S130:请参阅图5A和图5B所示,在所述图形孔201内的预定区块31’上依序成形一键结层32与一硬金层(hard gold layer)33,进一步地说,在所述导电层10的预定区块31’上以例如电镀方式沉积形成有上述键结层32及设置于键结层32的硬金层33;而后去除所述图案层20。

其中,所述键结层32与硬金层33于本实施例中是大致填满上述图形孔201,亦即,上述硬金层33外表面大致齐平于图案层20的外表面,但本发明不受限于此。

再者,由于所述硬金层33与材质为铜的导电层10之间难以稳固地结合,所以本实施例是通过键结层32来使硬金层33能够稳固地附着于导电层10上。更详细地说,本实施例的键结层32为镍层32,并且所述镍层32能够分别与硬金层33及材质为铜的导电层10产生强度较佳的键结。

步骤S140:请参阅图6A和图6B所示,在所述硬金层33及导电层10的一预定线路区块2’上形成一遮蔽层30。也就是说,设计者能通过特定图案的遮蔽层30覆盖导电层10的预定线路区块2’,来成形所需要的线路图案。其中,上述预定线路区块2’与预定区块31’为导电层10中相互分离的两个部位,并且本实施例的预定线路区块2’可以设置于上述基板1设有贯孔13的部位上,但不以此为限。

进一步地说,本实施例的遮蔽层30是在硬金层33与导电层10上先贴附干膜,而后将导电层10上的干膜以曝光显影方式形成具有特定形状的遮蔽层30,用于使遮蔽层30能够覆盖设计者所需的特定形状的预定线路区块2’。其中,上述遮蔽层30的成形过程中,较佳的环境条件为温度20℃~24℃、湿度50%~60%。因此,本实施例所采用的步骤S140可以依据设计者的不同需求,而实现各种形状的预定线路区块2’。

步骤S150:请参阅图7A和图7B所示,通过蚀刻上述未被遮蔽层30覆盖的导电层10部位,以使所述导电层10成形为(或留下)铜层31(即预定区块31’)及至少一线路2(即预定线路区块2’),而后去除所述遮蔽层30。也就是说,将所述导电层10蚀刻成铜层31及与上述铜层31相互分离的至少一线路2。上述铜层31(即预定区块31’)、键结层32、及硬金层33于本实施例中合称为一独立金属垫3。

其中,上述”蚀刻”于本实施例中是以化学蚀刻方式实施,并且上述化学蚀刻较佳是采用的不会侵蚀硬金层33的蚀刻液,用于利于独立金属垫3的硬金层33能够维持设计者所预定的外型,但本发明不受限于此。

再者,所述独立金属垫3的硬金层33于本实施例中适用于接触式连接,用于通过碰触外部元件而形成连通,进而应用在伺服器或半导体测试等方面,但本发明不以此为限。

步骤S160:请参阅图8A和图8B所示,于所述基板1的第一板面11形成一防焊层4,并使所述防焊层4围绕于所述独立金属垫3外侧且将所述线路2的至少部分埋置于其内。进一步地说,所述防焊层4能设有用来露出部分线路2的至少一开孔41,以使上述经由开孔41露出的线路2部位能够连接(如:焊接或插接等)于一外部元件。

再者,所述防焊层4在成形的过程中,较佳是防焊层4未接触于独立金属垫3,并且所述硬金层33相较于第一板面11的高度H1不小于所述防焊层4相较于第一板面11的高度H2,但本发明不受限于此。

据此,经由实施上述步骤S110~S160之后,即可制造完成本实施例的电路板结构100,但上述各个步骤S110~S160在实际运用时,能够以合理的方式置换、变化或取代,而不局限于本实施例所载。举例来说,所述基板1的第一板面11与第二板面12可以皆成形有独立金属垫3,或者是上述第一板面11与第二板面12的其中之一成形有独立金属垫3。

再者,本实施例于下述将接着说明经由实施步骤S110~S160所完成的电路板结构100的构造特征,但本发明的电路板结构100并不局限于以步骤S110~S160所完成。

请参阅图8A至图8C,所述电路板结构100包括一基板1、设置于所述基板1且相互分离的一线路2与一独立金属垫3、及设置于所述基板1的一防焊层4。其中,所述基板1包含有位于相反侧的一第一板面11与一第二板面12,并且上述线路2、独立金属垫3、及防焊层4皆设置于基板1的第一板面11。

再者,所述独立金属垫3与线路2呈间隔设置且相互电性隔离,并且所述独立金属垫3包含有设置于上述第一板面11的一接合部34及形成于接合部34上的一硬金层33。

更详细地说,所述接合部34于本实施例中包含有设置于所述基板1第一板面11的一铜层31及连接上述铜层31与硬金层33的一镍层32,并且本实施例中的铜层31与线路2是通过相同的导电层10所制造而具有相同的高度。须说明的是,本实施例的接合部34虽是以铜层31与镍层32为例,但本发明的接合部34不排除以其他构造或材质取代上述铜层31与镍层32。

进一步地说,所述铜层31侧壁未包覆于所述硬金层33与镍层32,并且铜层31的宽度自邻近第一板面11朝向远离第一板面11(如图8B中的由下而上的方向)逐渐地缩小。所述硬金层33与镍层32的宽度大致相等,并且所述硬金层33与镍层32的外侧部位凸伸出上述铜层3,而所述硬金层33相较于第一板面11的高度H1不小于(如:大于)所述防焊层4相较于第一板面11的高度H2。

另,所述防焊层4围绕于独立金属垫3外侧,并且所述线路2至少部分埋置于所述防焊层4内。其中,所述独立金属垫3较佳是未接触于防焊层4。

综上所述,本发明实施例所公开电路板结构及其制造方法,可无需移除任何硬金层33而形成独立金属垫3,并且所述独立金属垫3不会连接任何无效区块,以避免电路板结构100产生不必要的贵金属浪费。

再者,由于本实施例的电路板结构100在形成独立金属垫3的过程中,无需如现有般以非镀金区作为待镀金区的导引(如图1),所以本实施例的电路板结构100能够在基板1上的任何位置形成有独立金属垫3,进而使基板1上的独立金属垫3的外型、尺寸、位置、及密度,较不会受到限制,用于有效地促进电路板结构100的发展。

以上所述仅为本发明的优选可行实施例,并非用来局限本发明的保护范围,凡依本发明权利要求所做的均等变化与修饰,皆应属本发明的权利要求书的保护范围。

- 电路板结构制造方法、电路板结构及电子设备

- 电路板结构的制造方法和电路板结构