内存内运算器及其运算方法

文献发布时间:2023-06-19 12:16:29

技术领域

本发明涉及一种内存内运算器及其运算方法,特别是涉及一种可调整感测放大器的数码转换范围的内存内运算器及其运算方法。

背景技术

随着人工智能技术的成熟,具有人工智能运算能力的电子装置随着蓬勃产生。为提升执行人工智能运算的类神经网络,一种内存内运算(computation in memory,CIM)的概念被提出。

内存内运算是通过利用记忆胞来做为类神经网络中的节点,并对记忆胞写入数据,通过改变记忆胞的等校阻值或转导值来做为权重,再藉由对记忆胞提供输入信号,以使多个记忆胞对多个输入信号执行乘加运算(或卷积运算),来产生运算结果。内存内运算的作法可大幅降低电路面积,提升类神经网络的执行效益。

值得注意的,现有技术的内存内运算器常设置具备固定参考信号的感测放大器,来对记忆胞数组所产生的读出信号进行转换动作。然而,读出信号的电流值的大小范围,可能会随着输入信号的规模,类神经网络的节点数而产生变异。因此,利用具有固定参考信号感测放大器来执行读出信号的转换动作时,可能造成转换时间的浪费,或过度的功率损耗的问题。

发明内容

本发明是针对一种可降低功耗并提升指令周期的内存内运算器及其运算方法。

根据本发明的实施例,内存内运算器包括字线计算器、决策器以及感测放大器。字线计算器计算内存的被开启字线数量。决策器耦接运算控制器,依据内存的被应用尺寸以及被开启字线数量的至少其中之一来产生多个参考信号,参考信号用以设定分布范围中。感测放大器耦接至内存以及决策器,接收内存的读出信号,并依据参考信号来转换该读出信号以获得运算结果。

根据本发明的实施例,内存内运算方法包括:计算内存的被开启字线数量;依据内存的被应用尺寸以及被开启字线数量的至少其中之一来产生多个参考信号,参考信号用以设定一分布范围;以及,接收内存的读出信号,并依据参考信号来转换读出信号以获得运算结果。

基于上述,本发明提供决策器以依据内存的被应用尺寸以及被开启字线数量的至少其中之一来产生多个参考信号,再通过参考信号以设定感测放大器的数码转换范围,并藉以提升指令周期,并降低其功耗。

附图说明

包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

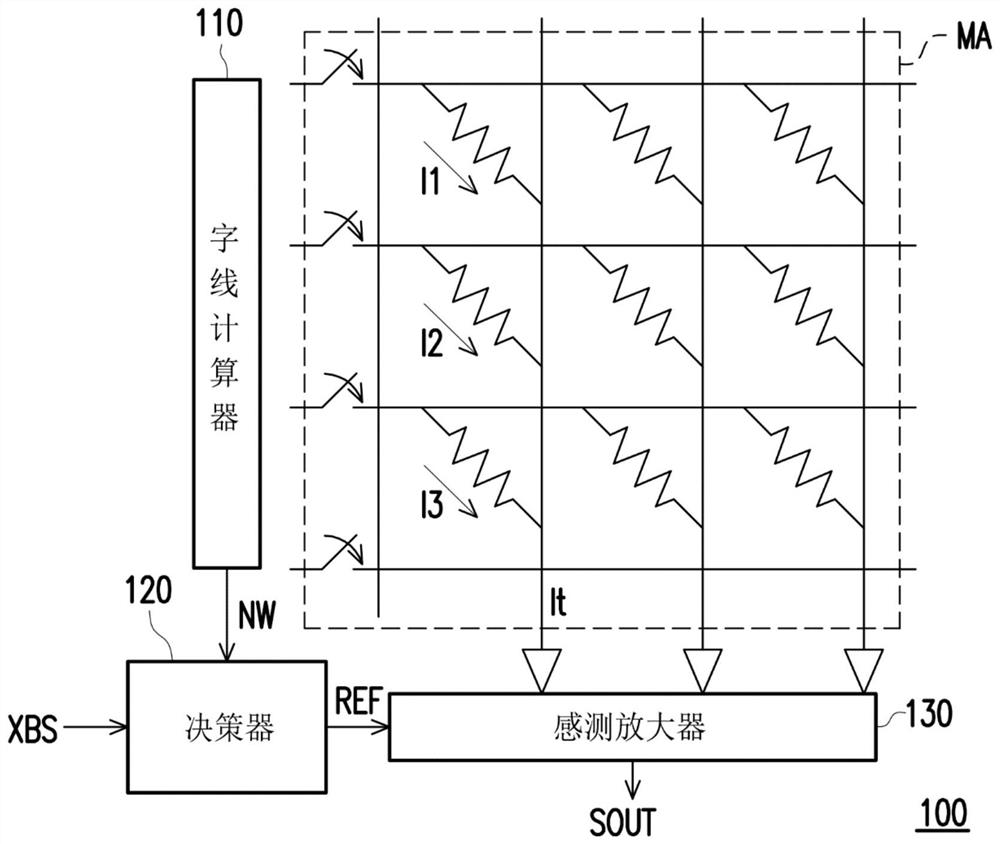

图1为本发明一实施例的内存内运算器的示意图;

图2为本发明另一实施例的内存内运算器的示意图;

图3A至图3C分别为本发明实施例中,产生参考信号的不同实施方式的示意图;

图4绘示本发明实施例的内存内运算方法的流程图。

其中,附图标记:

100、202:内存内运算器;

110、2221:字线计算器;

120、2222:决策器;

130、2223:感测放大器;

2224:运算控制器;

200:系统;

201:主机端;

230:内存;

231:内存控制器;

232:字线;

233:输入输出端口;

234:记忆胞数组;

I1~I3:信号;

It:读出信号;

MA:记忆胞数组;

NW:被开启字线数量;

REF、REF311~REF312、REF321~REF322、REF331~REF332:参考信号;

ROD:读出信号;

SOUT:运算结果;

XBS:被应用尺寸;

S410~S430:运算方法的步骤。

具体实施方式

现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在图式和描述中用来表示相同或相似部分。

请参照图1,图1为本发明一实施例的内存内运算器的示意图。内存内运算器100包括字线计算器110、决策器120以及感测放大器130。字线计算器110耦接至记忆胞数组MA,并用以计算记忆胞数组MA的被开启字线数量NW。决策器120耦接至字线计算器110。决策器120接收记忆胞数组MA的被开启字线数量NW以及记忆胞数组MA的被应用尺寸XBS,并依据记忆胞数组MA的被应用尺寸XBS以及被开启字线数量NW的至少其中之一来产生多个参考信号REF。

在另一方面,感测放大器130耦接至记忆胞数组MA以及决策器120。感测放大器130接收参考信号REF,其中参考信号REF可用来设定感测放大器130所执行的数码转换的一分布范围。感测放大器130并由记忆胞数组MA接收读出信号It,并依据参考信号REF来转换读出信号It以获得运算结果SOUT。细节上来说明,感测放大器130读出信号It来与多个参考信号REF进行比较,来获得运算结果SOUT。

在本实施例中,记忆胞数组MA中的多个记忆胞用以储存多个权重(例如以记忆胞的转导值来表示)。记忆胞并在接收输入信号后,通过被开启的字线,依据输入信号以及记忆胞所储存的权重来产生信号I1~I3(电流信号)。读出信号It则可以为信号I1~I3的和。内存内运算器100可用以实施类神经网络运算。

在实际实施方面,记忆胞数组MA可以为非挥发性内存,例如闪存、电阻式内存或任意可多次被读写的非挥发性内存。

附带一提的,记忆胞数组MA的被应用尺寸XBS可以依据类神经网络运算对应的分析对象来设定。记忆胞数组MA可以具有一个相对大的尺寸,来因应不同种类的分析对象,并因应具有不同节点数量的类神经网络。记忆胞数组MA的被应用尺寸XBS则可设定为不大于记忆胞数组MA总尺寸的一个数值。

在本实施例中,感测放大器130可以为一模拟转数字转换电路。感测放大器130并依据参考信号REF来设定所执行的模拟数字动作中,所产生的数字码的数码分布范围。具体来说明,当记忆胞数组MA的被应用尺寸XBS及/或被开启字线数量NW相对小时,表示感测放大器130所可能接收到的读出信号也具有相对小的数值。因此,通过调低参考信号REF所形成的分布范围,可以提升感测放大器130所执行的模拟转数字转换动作的效率。相对的,当记忆胞数组MA的被应用尺寸XBS及/或被开启字线数量NW相对大时,感测放大器130所可能接收到的读出信号也具有相对大的数值。而通过适度的调大参考信号REF所形成的分布范围,可维持感测放大器130所执行的模拟转数字转换动作的正确性,并提升工作效能。

如此一来,感测放大器130可适应性的依据记忆胞数组MA的被应用尺寸XBS以及被开启字线数量NW的至少其中之一,来调整所要产生的运算结果SOUT的分布范围,可提升转换速度并减低功率消耗。

此外,本实施例中,决策器120可以应用数字电路来实施。决策器120可通过硬件描述语言(Hardware Description Language,HDL)或是其他任意本领域具通常知识者所熟知的数字电路的设计方式来进行设计,并通过现场可程序逻辑门数组(Field ProgrammableGate Array,FPGA)、复杂可程序逻辑装置(Complex Programmable Logic Device,CPLD)或是特殊应用集成电路(Application-specific Integrated Circuit,ASIC)的方式来实现的硬件电路。或者,决策器120也可以是具运算能力的任意形式的处理器,没有特定的限制。

在本发明实施例中,字线计算器110也可通过数字电路来实施,并用以计数在每一次运算中,记忆胞数组MA同时被开启的字线的数量。

以下请参照图2,图2为本发明另一实施例的内存内运算器的示意图。内存内运算器202耦接至主机端201并形成一系统200。内存内运算器202可依据主机端201的指令以执行类神经网络运算。内存内运算器202包括内存230以及缓冲器221。内存内运算器202包括字线计算器2221、决策器2222、感测放大器2223以及运算控制器2224。内存230则包括内存控制器231、字线232、输入输出端口233以及记忆胞数组234。

在本实施例中,运算控制器2224用以操控每一次类神经网络的运算行为。字线计算器2221用以计数每一次运算中,字线232的被开启数量NW。基于上述,字线计算器2221可通过运算控制器2224来得知字线232的被开启数量NW。决策器2222耦接至字线计算器2221,并藉以接收字线232的被开启数量NW。另外,决策器2222接收内存230的被应用尺寸XBS,并依据被开启数量NW以及被应用尺寸XBS的至少其中之一来产生运算数值A1。决策器2222再依据运算数值A1来产生多个参考信号REF。

决策器2222提供参考信号REF至感测放大器2223。感测放大器2223则可依据参考信号REF来设定分布范围,并依据多个参考信号REF来转换记忆胞数组234所提供的读出信号ROD,并藉以获得一运算结果SOUT。

在本实施例中,缓冲器221可以提供内存内运算器202以作为数据暂存的媒介。缓冲器221可以利用任意形式的随机存取内存(Random Access Memory,RAM)来建构,没有特定的限制。

此外,本实施例中,内存230的被应用尺寸XBS可以由主机端201设定,并通过写入命令的方式来输入至决策器2222。决策器2222中可提供缓存器或内存来储存被应用尺寸XBS。缓冲器221也作为记录被应用尺寸XBS的媒介,没有特定的限制。

在另一方面,内存控制器231用以执行记忆胞数组234的读写动作,输入输出端口233则作为记忆胞数组234的数据存取媒介。

在实施细节方面,请同步参照图2以及图3A至图3C。图3A至图3C分别为本发明实施例中,产生参考信号的不同实施方式的示意图。在图3A至图3C中,横轴表示被开启字线数量NW,而纵轴则表示感测放大器2223所设定的数码分布范围。

请先参照图3A,在本实施方式中,决策器2222可仅依据记忆胞数组234中的被开启字线数量NW的平方根来设定参考信号REF311~REF312。其中,对应相同的被开启字线数量NW,参考信号REF311以及REF312的绝对值是相同的。并且,在图3A中,参考信号REF311~REF312随着被开启字线数量NW的变化呈现非线性的变化,并且,分布范围的大小与被开启字线数量NW为非线性的正相关。也就是说,被开启字线数量NW越多时,参考信号REF311~REF312的分布范围越大。

以被开启字线数量NW为m为范例,参考信号REF311~REF312可以依据

接着请参照图3B,在图3B中,决策器2222仅依据记忆胞数组234的被应用尺寸的平方根来设定参考信号REF321~REF322。在本实施方式中,参考信号REF321~REF322可依据

值得一提的,上述的k为在内存230中具有最大字线开启数量所获得的记忆胞数组234的被应用尺寸XBS。上述的参考信号REF321~REF322在决定后,不会随着被开启字线数量NW发生变化而生改变。但值得注意的,类神经网络中常具有多个层,对应多个层所分别设置的多个内存内运算器中,数值k是可以不相同的。

接着请参照图3C,在图3C中,决策器2222可据记忆胞数组234中的被开启字线数量NW以及被应用尺寸XBS的平方根来设定参考信号REF331~REF332。其中,参考信号REF331~REF332可依据

在本实施方式中,参考信号REF331~REF332随着被开启字线数量NW的变化呈现线性的变化,并且,分布范围的大小与被开启字线数量NW为线性的正相关。

值得一提的,在图3A~图3C中,参考信号的数量都没有一定的限制。设计者可以依据感测放大器2223所要产生的运算结果SOUT的位数来设定参考信号的数量。

以下请参照图4,图4为本发明实施例的内存内运算方法的流程图。在步骤S410中,计算内存的被开启字线数量。接着,步骤S420中依据内存的被应用尺寸以及被开启字线数量的至少其中之一来产生多个参考信号,上述的参考信号可用以设定分布范围。步骤S430则接收内存的读出信号,并依据参考信号以设定数码分布范围,并依据数码分布范围来转换读出信号以获得运算结果。

关于上述步骤的实施细节,在前述的实施例以及实施方式中都有详细的说明,以下恕不多赘述。

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

- 内存内运算器及其运算方法

- 一种忆阻存内矢量矩阵运算器及运算方法