一种背面照射的单光子雪崩二极管及其制作方法

文献发布时间:2023-06-19 12:16:29

技术领域

本发明属于单光子探测技术领域,具体涉及一种背面照射的低暗计数率单光子雪崩二极管及其制作方法。

背景技术

单光子探测技术在国防建设、工业和民用生活领域具有广泛的应用前景,比如:量子密钥分发、激光雷达、荧光寿命成像和三维视觉系统等。基于CMOS工艺的单光子雪崩二极管(single photon avalanche photodiode,记为SPAD)作为单光子探测的一类核心器件,愈加受到研究人员的关注和重视。盖革模式下的单光子雪崩二极管是一种能探测极微弱光信号的探测器,它具有内部增益大、灵敏度高、响应速度快、探测效率高、噪声低、体积小、结构坚固以及易于集成等优点。随着单光子探测应用领域的不断扩展,对SPAD的性能要求也越来越高,暗计数率特性是判断SPAD器件性能的核心参数之一。暗计数较小的器件,能更好的排除噪声信号的干扰,准确的探测到信号光。

传统的单光子雪崩二极管暗计数率较高,而且目前研究较多的为光正面照射的单光子雪崩二极管,这种结构的单光子雪崩二极管与淬灭电路和读出电路集成时,电路被制造在单光子雪崩二极管的周围,单光子雪崩二极管的感光区域只占整个像素的一小部分,使得其探测效率很低。

发明内容

发明目的:本发明的目的在于针对现有单光子雪崩二极管结构存在的不足,提出一种背面照射的单光子雪崩二极管及其制作方法,使器件在常温下具有更低的暗计数率和更高的探测效率。本发明采用P型雪崩掺杂区、P型外延层中心区与N型雪崩掺杂区,可得到较低的雪崩区电场,避免隧穿效应的产生,从而降低器件的暗计数率。采用光从器件背面照射的方式,将电路集成在器件的下方,可以有效提高器件的探测效率。

技术方案:为实现上述目的,本发明提供如下技术方案:

背面照射的单光子雪崩二极管,包括P型外延层,在所述的P型外延层的内部设置P+重掺杂区,在所述的P+重掺杂区的外围同轴设置P-低掺杂区,在所述的P-低掺杂区的下方同轴设置P型雪崩掺杂区,在所述的P+重掺杂区的两侧设置N+重掺杂区,在所述的N+重掺杂区的下方同轴设置N阱区,在所述的P型雪崩掺杂区下方间隔设置N型雪崩掺杂区,在所述的N型雪崩掺杂区的下方设置N-低掺杂区。

进一步地,所述的P+重掺杂区被包含在P-低掺杂区的内部。

进一步地,所述的P型雪崩掺杂区与P-低掺杂区、N型雪崩掺杂区与N-低掺杂区均有部分重叠。

进一步地,所述的P型外延层中心区为P型外延层的一部分。

进一步地,所述的P型雪崩掺杂区与N型雪崩掺杂区中间被外延层中心区间隔开。

进一步地,在所述的N+重掺杂区上端引出阴极;在所述的P+重掺杂区上端引出阳极。

进一步地,所述的背面照射的单光子雪崩二极管的制作方法,包括以下步骤:

1)用外延工艺生长出P型外延层;

2)在P型外延层(1)上端面热生长二氧化硅层;

3)在二氧化硅层上旋涂光刻胶,通过掩模版选择性曝光和显影,暴露出P+重掺杂区(2)所在区域的二氧化硅层;

4)通过刻蚀工艺,将所述的P+重掺杂区(2)所在区域的二氧化硅清除,暴露出所述的P型外延硅;

5)离子注入P型杂质后,去除所述的光刻胶;形成所述的P+重掺杂区(2);

6)在所述步骤5)形成的结构上端面旋涂光刻胶,通过曝光显影工艺,暴露出所述的P-低掺杂区(3)所在区域,通过离子注入P型杂质,形成所述的P-低掺杂区(3);去除所述光刻胶;

7)在步骤6)形成的结构上端面旋涂光刻胶,通过曝光显影工艺,暴露出所述的P型雪崩掺杂区(4)所在区域;通过离子注入P型杂质,形成所述的P型雪崩掺杂区(4);去除所述光刻胶;

8)在所述步骤7)形成的结构上端面旋涂光刻胶,通过曝光显影工艺,暴露出所述的N+重掺杂区(5)所在区域;通过离子注入N型杂质,形成所述的N+重掺杂区(5);去除所述光刻胶;

9)在所述步骤8)形成的结构上端面旋涂光刻胶,通过曝光显影工艺,暴露出所述的N阱区(6)所在区域;通过离子注入N型杂质,形成所述的N阱区(6),去除所述光刻胶;

10)在所述步骤9)形成的结构上端面旋涂光刻胶,通过曝光显影工艺,暴露出所述的N型雪崩掺杂区(7)所在区域;通过离子注入N型杂质,形成所述的N型雪崩掺杂区(7);去除所述光刻胶;

11)在所述步骤10)形成的结构上端面旋涂光刻胶,通过曝光显影工艺,暴露出所述的N-低掺杂区(8)所在区域;通过离子注入N型杂质,形成所述的N-低掺杂区(8);去除所述光刻胶;

12)进行退火工艺;

13)在所述步骤12)形成的结构上端面淀积一定厚度的二氧化硅保护层;

14)在所述步骤13)形成的结构上端面旋涂光刻胶,通过曝光显影工艺,暴露出所述的阴极(9)和阳极(10)所在区域;通过刻蚀工艺,清除所述的阴极(9)和阳极(10)所在区域淀积的二氧化硅;去除所述光刻胶;

15)在所述步骤14)形成的结构上端面,利用磁控溅射的工艺,淀积金属铝;

16)在所述步骤15)形成的结构上端面旋涂光刻胶,通过曝光显影工艺,暴露所述的阴极(9)和阳极(10)所在区域之外的区域;通过刻蚀工艺,清除所述的阴极(9)和阳极(10)所在区域之外的区域的金属铝;去除所述光刻胶;

17)通过热处理工艺,完成所述步骤16)形成的结构中阴极(9)和阳极(10)的合金化。

本发明的有益效果是:与现有的技术相比,本发明的背面照射单光子雪崩二极管,通过优化结构,使光从器件的背面照射,并将外围电路集成在器件的下方,增大了器件感光区域占整个像素的面积,提高了器件的探测效率。采用P阱中心区、P型外延层中心区与中心N型区形成的雪崩区,掺杂水平较低,雪崩结为缓变结,显著降低雪崩区的电场,因此抑制了隧穿效应的产生,使其暗计数率明显低于目前已有结构的器件。

附图说明

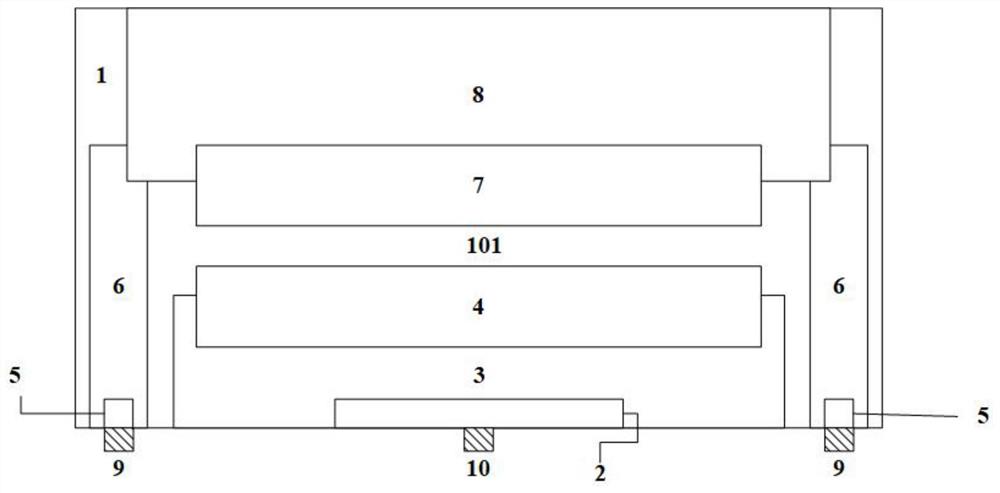

图1为单光子雪崩二极管的横截面结构示意图;

图2为单光子雪崩二极管横截面的仿真电场分布图;

图3为单光子雪崩二极管仿真的探测效率曲线图;

附图标记:1-P型外延层、2-P+重掺杂区、3-P-低掺杂区、4-P型雪崩掺杂区、5-N+重掺杂区、6-N阱区、7-N型雪崩掺杂区、8-N-低掺杂区、9-阴极、10-阳极、101-P型外延层中心区。

具体实施方式

为了更好的理解本发明专利的内容,下面结合附图来进一步说明本发明的技术方案。

如图1所示,背面照射的单光子雪崩二极管,包括P型外延层1,P型外延层1的内部设置P+重掺杂区2,P+重掺杂区2的外围同轴设置P-低掺杂区3,P-低掺杂区3的下方同轴设置P型雪崩掺杂区4,P+重掺杂区2的两侧设置N+重掺杂区5,N+重掺杂区5的下方同轴设置N阱区6,P型雪崩掺杂区4下方间隔设置N型雪崩掺杂区7,N型雪崩掺杂区7的下方设置N-低掺杂区8。

P+重掺杂区2被包含在P-低掺杂区3的内部。

P型雪崩掺杂区4与P-低掺杂区3、N型雪崩掺杂区7与N-低掺杂区8均有部分重叠。

P型外延层中心区101为P型外延层1的一部分。

P型雪崩掺杂区4与N型雪崩掺杂区7中间被外延层中心区101间隔开。

N+重掺杂区5上端引出阴极9;在所述的P+重掺杂区2上端引出阳极10。

本发明并不局限于以下实施例。图2为实施例的仿真电场分布图,图3为实施例的探测效率曲线图。经测量,本发明中PN结的反偏击穿电压为46.5V,在常温时,外加5V过偏压下,暗计数率为0.81Hz/μm

该背面照射的单光子雪崩二极管的制作方法,包括以下步骤:

1)用外延工艺生长出P型外延层1;

2)在P型外延层1上端面热生长二氧化硅层;

3)在二氧化硅层上旋涂光刻胶,通过掩模版选择性曝光和显影,暴露出P+重掺杂区2所在区域的二氧化硅层;

4)通过刻蚀工艺,将所述的P+重掺杂区2所在区域的二氧化硅清除,暴露出所述的P型外延硅;

5)离子注入P型杂质后,去除所述的光刻胶;形成所述的P+重掺杂区2;

6)在所述步骤5)形成的结构上端面旋涂光刻胶,通过曝光显影工艺,暴露出所述的P-低掺杂区3所在区域,通过离子注入P型杂质,形成所述的P-低掺杂区3;去除所述光刻胶;

7)在步骤6)形成的结构上端面旋涂光刻胶,通过曝光显影工艺,暴露出所述的P型雪崩掺杂区4所在区域;通过离子注入P型杂质,形成所述的P型雪崩掺杂区4;去除所述光刻胶;

8)在所述步骤7)形成的结构上端面旋涂光刻胶,通过曝光显影工艺,暴露出所述的N+重掺杂区5所在区域;通过离子注入N型杂质,形成所述的N+重掺杂区5;去除所述光刻胶;

9)在所述步骤8)形成的结构上端面旋涂光刻胶,通过曝光显影工艺,暴露出所述的N阱区6所在区域;通过离子注入N型杂质,形成所述的N阱区6,去除所述光刻胶;

10)在所述步骤9)形成的结构上端面旋涂光刻胶,通过曝光显影工艺,暴露出所述的N型雪崩掺杂区7所在区域;通过离子注入N型杂质,形成所述的N型雪崩掺杂区7;去除所述光刻胶;

11)在所述步骤10)形成的结构上端面旋涂光刻胶,通过曝光显影工艺,暴露出所述的N-低掺杂区8所在区域;通过离子注入N型杂质,形成所述的N-低掺杂区8;去除所述光刻胶;

12)进行退火工艺;

13)在所述步骤12)形成的结构上端面淀积一定厚度的二氧化硅保护层;

14)在所述步骤13)形成的结构上端面旋涂光刻胶,通过曝光显影工艺,暴露出所述的阴极9和阳极10所在区域;通过刻蚀工艺,清除所述的阴极9和阳极10所在区域淀积的二氧化硅;去

除所述光刻胶;

15)在所述步骤14)形成的结构上端面,利用磁控溅射的工艺,淀积金属铝;

16)在所述步骤15)形成的结构上端面旋涂光刻胶,通过曝光显影工艺,暴露所述的阴极9和阳极10所在区域之外的区域;通过刻蚀工艺,清除所述的阴极9和阳极10所在区域之外的区域的金属铝;去除所述光刻胶;

17)通过热处理工艺,完成所述步骤16)形成的结构中阴极9和阳极10的合金化。

以上仅是本发明的优选实施方式,应当指出:对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以对器件结构中各区域的掺杂浓度以及器件的制备工艺进行调整,这些调整也应视为本发明的保护范围。

- 一种背面照射的单光子雪崩二极管及其制作方法

- 一种近红外宽光谱的CMOS单光子雪崩二极管探测器及其制作方法