有源双锥天线和接收阵列

文献发布时间:2023-06-19 19:16:40

技术领域

本文公开的技术总体上涉及接收天线,并且具体涉及双锥形和Vivaldi接收天线。

背景技术

在以下公开中,采用术语“无源天线”和“有源天线”。有源天线包括内置到单元中的集成低噪声信号放大器。无源天线是不具有放大级的天线。相同类型的有源或无源天线的天线元件之间没有差异;唯一的区别是一个具有低噪声放大器,而另一个没有低噪声放大器。有源天线可以用于接收和发射应用。当天线用于接收时,集成的低噪声放大器提升由天线拾取的射频(RF)信号以补偿下游电缆损耗,从而允许更长的远程电缆延伸。如本文所使用的,术语“缓冲放大器”(亦称为“缓冲器”)是放大器,出于减轻天线阻抗可以产生的驻波的影响的目的,该放大器提供一个电路到另一个电路的电阻抗隔离。换言之,从天线缓冲接收器。

无源双锥形天线是使用与频率无关的天线的原理的宽带天线。这意味着由于几何形状仅由角度指定,所以辐射特性独立于频率,在低端处由天线的尺寸限制,并且在高端处由馈电点(在天线的顶点处)的公差限制。低频率限制在非常高的频带中尤其繁重,其中,实现高性能所需要的尺寸和重量与系统要求不一致。典型的无源双锥形天线可以接收在1-10GHz频率范围(在本文中称为“传统频带”)内的信号。在其中天线变得太小的所谓的“扩展频带”(例如,0.1-1GHz)的频率处,双锥形天线表现得像电学上小的偶极天线。性能从根本上受到Bode-Fano和Chu限制的限制。

将高阻抗缓冲放大器结合到偶极子天线的馈电中的有源偶极子天线在0.1-1GHz的频率范围内实现改进的性能,但是当天线不是电学上小的时,它们不利用宽带行为。代替宽带行为,有源偶极天线具有几个高阶谐振。

Vivaldi天线(亦称为锥形缝隙天线)是共平面宽带天线,其可以由金属片、印刷配线板或在一侧或两侧上金属化的介电基板制成。有源宽带Vivaldi天线已经被设计为在0.1-10GHz的范围内操作,但是是定向天线。在许多情况下,需要全向天线。

无源双锥形天线和无源Vivaldi天线的组合将能够实现测向。然而,这种组合可能在扩展频带中具有降低的灵敏度。

发明内容

以下详细公开的主题部分地涉及与宽带低噪声缓冲放大器组合的双锥形天线(或单个天线锥体),其中,缓冲放大器在扩展频带中具有高阻抗,该扩展频带被定义为双锥形天线与系统阻抗匹配(或可替代地具有一定大小)的频率以下的频带。具有集成缓冲放大器的双锥形天线在本文中被称为“有源双锥形天线”。以下详细公开的主题进一步涉及包括有源双锥形天线和多个有源Vivaldi天线的天线阵列。

本文公开的宽带双锥形型接收天线既在“传统频带”操作(其中天线尺寸在最小频率处大于约1/4λ)又在低频“扩展频带”操作(其中天线尺寸小于1/4λ)。传统频带和扩展频带在边界频率f

有源双锥形天线包括双锥形(或圆锥形)天线和直接集成到天线的馈电中的缓冲放大器。如本文中所使用的,项“直接到馈电中”意指用于将天线的馈电连接到缓冲放大器的任何传输线比在扩展频带中的任何频率处的波长短得多。

缓冲器被配置为在扩展频带中具有高阻抗输入(即,比传统频带中的天线的阻抗高得多)。在一些实施方式中,缓冲器的输入阻抗在传统频带中也高,而在其他实施方式中,缓冲器在扩展频带中与天线阻抗匹配。缓冲器优选地包括具有由氮化镓(GaN)制成的半导体沟道的场效应晶体管(FETs)。缓冲器输出与传统频带和延展频带两者上的接口阻抗(通常为50、75或100欧姆)阻抗匹配。

集成双锥形天线和缓冲放大器的目的是将宽带全向(在方位平面中)接收天线的可用带宽扩展到较低频率,而不增加天线尺寸(例如,体积)。例如,与无源双锥形天线相比,扩展频带中的接收器灵敏度可被提高10dB,同时在传统频带中被保持在不变的水平。

本文所提出的创新技术的另一方面涉及将有源双锥形天线与有源Vivaldi天线集成,以在扩展频带中形成具有改善的接收器灵敏度的阵列。将有源双锥形天线与有源宽带Vivaldi天线组合使得具有测向功能,同时还能够进行低频带宽扩展。

尽管下面将详细描述有源双锥形天线和包括有源双锥形和Vivaldi天线的组合的接收阵列,但这些实施方式中的一个或多个可以以下方面中的一个或多个为特征。

以下详细公开的主题的一个方面是一种有源双锥形天线,包括:上锥体和下锥体,上锥体和下锥体中的每个包括相应的截头顶点;第一馈电点和第二馈电点,分别连接到上锥体和下锥体的截头顶点;第一导体和第二导体,分别连接至第一馈电点和第二馈电点;以及缓冲放大器,包括分别连接到第一导体和第二导体的第一输入端和第二输入端。缓冲放大器具有输入阻抗和输出阻抗,输入阻抗与处于和高于但不低于频率f

根据在前一段落中描述的有源双锥形天线的一个实施方式,缓冲放大器包括场效应晶体管,该场效应晶体管具有连接至第一导体的栅极和连接至在下锥体的截头顶点附近的第二导体的源极/接地。根据另实施方式,缓冲放大器包括以共源共栅配置布置的第一场效应晶体管和第二场效应晶体管;第一场效应晶体管包括与第一导体连接的第一栅极;以及第二场效应晶体管包括连接到电压源的第二栅极。根据另一实施方式,缓冲放大器包括具有分别连接到第一导体和第二导体的相应栅极的第一场效应晶体管和第二场效应晶体管。

根据一个实施方式,缓冲放大器包括共源场效应晶体管以及连接场效应晶体管的栅极和漏极的RC反馈电路。RC反馈电路包括:电阻器,与场效应管的栅极连接,电阻器的阻值在双锥形天线接收传统频段信号时,使得第一缓冲放大器的输入阻抗与双锥形天线的阻抗相匹配;以及电容器,连接到电阻器并连接到场效应晶体管的漏极,电容器的电容在从传统频带延伸到小于传统频带的最低频率的频率的延伸频带中防止反馈。

以下详细公开的主题的另一方面是一种测向系统,包括:双锥形天线;Vivaldi天线;接收器,具有多个端口;第一缓冲放大器,具有连接到双锥形天线的输入端且具有连接到多个端口中的第一端口的输出端;以及第二缓冲放大器,具有连接到Vivaldi天线的输入端,并具有连接到多个端口中的第二端口的输出端。

以下详细公开的主题的另一方面是一种有源锥形天线,包括:锥体,包括截头顶点和连接至截头顶点的馈电点;接地平面;第一导体和第二导体,分别连接至馈电点和接地平面;以及缓冲放大器,包括分别连接到第一导体和第二导体的第一输入端和第二输入端。缓冲放大器具有输入阻抗和输出阻抗,输入阻抗与处于和高于但不低于频率f

下文公开了有源双锥形天线及包含有源双锥形天线及Vivaldi天线的组合的接收阵列的其他方面。

附图说明

前述部分中讨论的特征、功能和优点可以在各种实施方式中独立地实现,或者可以在其他实施方式中组合。为了说明上述和其他方面的目的,在下文中将参考附图描述各种实施方式。所附的图均未按比例绘制。

图1是表示根据第一实施方式的双锥形天线的示图,该双锥形天线包括连接至低噪声缓冲放大器的一对天线锥体。

图2是表示根据第二实施方式的双锥形天线的示图,该双锥形天线包括一对天线锥体,该一对天线椎体连接至设置在下天线锥体内的低噪声缓冲放大器。

图3是表示根据第三实施方式的双锥形天线的示图,该双锥形天线包括一对天线椎体,该一对天线椎体连接至设置在连接至接地平面的天线锥体内的低噪声缓冲放大器。

图4是表示根据第四实施方式的锥形天线的示图,该锥形天线包括连接至低噪声缓冲放大器的一个输入端的单个天线锥体,低噪声缓冲放大器的另一个输入端连接至接地平面。

图5是表示根据一个实施方式的具有高阻抗输入、单端输出和频率相关的分路反馈的低噪声缓冲放大器的部件的电路图。

图6是表示根据另一个实施方式的具有高阻抗输入、单端输出和频率相关的分路反馈的低噪声缓冲放大器的部件的电路图。

图7是表示根据另一个实施方式的具有高阻抗输入、单端输出、以及提供反馈的逐渐滚降的RC网络的两级低噪声缓冲放大器的部件的电路图。

图8和图9分别是绘制两个模拟低噪声缓冲放大器的RC反馈网络的模拟阻抗相位和幅值对接收信号的频率的曲线图:一个模拟缓冲放大器具有一个RC反馈电路(由虚线曲线表示的相位)并且另一个模拟缓冲放大器具有四个并行RC电路(由实线曲线表示的相位)。

图10和图11是对分别具有一个RC反馈电路和四个并行RC反馈电路的模拟缓冲放大器绘制相关联的稳定性因子对接收信号的频率的曲线图。

图12是表示根据一个提出的实现方式的包括有源双锥形天线和四个有源Vivaldi天线的测向系统的一些部件的三维(3-D)视图的示图(未示出缓冲放大器)。

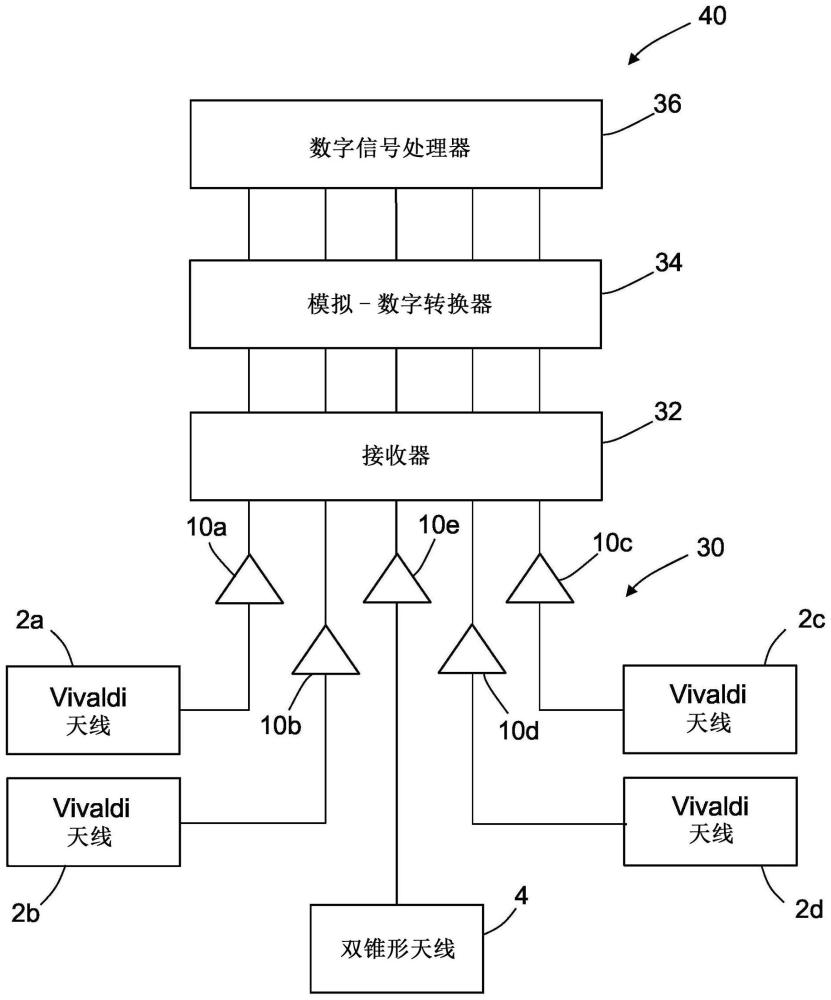

图13是根据一个实施方式识别包括有源双锥形天线和四个有源Vivaldi天线的测向系统的部件的框图。

图14是绘制具有如本文所提出的集成缓冲器的模拟有源Vivaldi天线的模拟增益和灵敏度益处的曲线图。

图15是绘制具有如在本文中提出的集成缓冲器的模拟有源双锥形天线的模拟增益和灵敏度益处的曲线图。

图16是表示具有集成缓冲放大器的活动Vivaldi天线的几个部件的示图。

图17是表示根据一个实施方式的印刷配线板的示图,该印刷配线板包括介电基板、Vivaldi天线的两个臂以及尽可能合理地靠近臂的近端设置的缓冲放大器。

图18是表示根据第一实施方式的具有高阻抗输入并且没有反馈的缓冲放大器的部件的电路图。

图19是表示根据第二实施方式的具有高阻抗输入并且没有反馈的缓冲放大器的部件的电路图。

图20是表示根据第三实施方式的具有高阻抗输入和反馈的缓冲放大器的部件的电路图。

图21是表示根据第四实施方式的具有高阻抗输入和反馈的缓冲放大器的部件的电路图。

图22是示出跨导级的单端实施方式的示图。

图23是示出跨导级的差分实施方式的示图;

在下文中,将参考附图,其中,不同附图中的类似元件具有相同的参考标号。

具体实施方式

下文更详细地描述有源双锥形天线及包括有源双锥形天线及Vivaldi天线的组合的接收阵列的说明性实施方式。然而,在本说明书中没有描述实际实现的所有特征。本领域技术人员将认识到,在任何这种实际实施方式的开发中,必须做出许多实现方式特定的决定,以实现开发者的特定目标,例如,遵守与系统相关的和与商业相关的约束,这些约束将因实现方式而异。此外,应当理解,这样的开发努力可能是复杂且耗时的,但是对于受益于本公开的本领域普通技术人员来说仍然是常规任务。

宽带接收天线在“传统频带”的频率中以及在低频“扩展频带”中操作,在“传统频带”中,天线尺寸大于在该频带中的最小频率f

如本文所使用的,“直接进入馈电”和“直接进入馈电点”是指用于将天线连接至缓冲放大器的输入元件(例如,FET的栅极)的任何传输线比在扩展频带中的任何频率处的波长短得多(优选地,在扩展频带中的任何频率处小于0.1波长),并且还优选地,在传统频带中的任何频率处小于1/4波长。缓冲放大器优选地被配置为在与天线阻抗Z

双锥形天线通常包括高度为h并且旋转对称角度为α的两个导电锥体。这些锥体优选地被设置成使得它们沿着相同的旋转对称轴线对准并且它们共享顶点。每个锥体的点被移除以允许插入两个馈电触点。锥体具有导电表面,这可以通过实心导体(例如金属)、金属丝网或筛网、或从顶点向外张开的多个线性导体来实现。在传统的操作频带中,阻抗由张角α确定。频率上限取决于顶点可以多小,而下限取决于张角和高度。当天线的尺寸远大于波长时,仅通过张角α有效地描述天线,这产生“频率无关天线”。随着波长增加,使得大小约为半波长,无源双锥形天线变得谐振。随着波长进一步增加,天线表现为短偶极并且主要是电容性的并且辐射电阻减小。因此,辐射品质因数增加,且变得无法在宽带宽上实现无源共轭阻抗匹配。在现有技术中,通常将天线设计为在高频传统频带中阻抗匹配到50欧姆。已知低频扩展频带中的任何操作具有差的实现增益,并且因此具有差的接收器灵敏度。

本文中所公开的创新性天线配置使用直接集成到天线馈电中的低噪声缓冲放大器来克服前一段落中所阐述的限制以克服这些挑战。缓冲器被配置为将由入射波在天线锥体上诱发的信号发射到输出,但具有对天线阻抗不敏感的输出阻抗。

图1是表示根据第一实施方式的双锥形天线4的示图,该双锥形天线4包括连接至缓冲放大器10的一对天线椎体。更具体地,双锥形天线4包括上天线锥体8a和下天线锥体8b。缓冲放大器10的相应输入端通过短的馈电导体1a和1b连接到上天线锥体8a和下天线锥体8b的顶点处的相应馈电点18。馈电导体1a和1b的电长度比扩展频带中的波长短得多。在该实例中,短馈电导体1a和1b垂直于椎体轴线延伸。在该实施方式中,优选的是,接收器导体垂直于天线极化,以避免馈线对入射波的散射。此外,在本实施方式中,缓冲放大器10优选具有差分输入。

图2是表示根据第二实施方式的双锥形天线4的示图,该双锥形天线4包括通过短馈电导体1a和1b连接至缓冲放大器10的上天线锥体8a和下天线锥体8b。在本实施方式中,缓冲放大器10布置在下天线锥体8b的内部。在下天线锥体8b的顶点附近设有反反馈通孔孔。缓冲放大器10的一个输入端子在反反馈通孔孔附近连接到下天线锥体8b;缓冲放大器10的另一个输入端穿过反馈通孔并且在其截头顶点处连接至上天线锥体8a。在该实施方式中,优选地,缓冲器具有单端输入。

图3是表示根据第三实施方式的双锥形天线4的示图。图3中描绘的双锥形天线4包括通过短馈电导体1a和1b(以与图2中描绘的布置相同的方式)连接到缓冲放大器10的上天线锥体8a和下天线锥体8b。第三实施方式与第二实施方式的不同之处在于下天线锥体8b位于接地平面上并连接到接地平面。

图4是表示根据第四实施方式的锥形天线的示图,锥形天线包括连接至缓冲放大器10的一个输入的单个天线锥体8,缓冲放大器10的另一个输入连接至接地平面20。接地平面20包括在截头顶点附近的反馈通孔。缓冲放大器10的第一输入端子连接至反馈通孔附近的接地平面20,并且缓冲放大器10的第二输入端子通过导体1a连接至天线锥体8。

缓冲放大器10优选地包括共源输入级,该共源输入级包括场效应晶体管,优选地是氮化镓(GaN)晶体管。缓冲放大器10的输入阻抗在低频扩展频带中优选地较高,并且与传统频带中的天线阻抗匹配,优选地50欧姆。输出阻抗优选地在低频扩展频带和高频传统频带两者上与系统阻抗(例如,50欧姆)匹配。

图5是表示根据一个实施方式的具有高阻抗输入、单端输出和频率相关的分路反馈的低噪声缓冲放大器10的部件的电路图。低噪声缓冲放大器10包括FET12和RC电路3,FET12具有连接到地的源极S,RC电路3提供频率相关的分路反馈。源极/接地被连接到反馈通孔附近的双锥形天线的下锥体。RC电路3跨过结J1和FET12的漏极D连接。结J1通过馈电导体1与FET12的栅极G连接。电阻器R1被选择为提供如上所述的阻抗匹配。电容器C1被选择为防止在低频扩展频带中的该反馈。这导致增加的增益和高输入阻抗。

根据图6中示出的优选实施方式,缓冲放大器10包括FET12和RC网络,该FET12具有接地的源极S,该RC网络包括提供反馈的逐渐滚降的多个RC电路3。更具体地,RC网络包括跨结点J1和J2并联连接的m个RC电路3。第一RC电路包括与电容器C1串联连接的电阻器R1。第m个RC电路包括与电容器Cm串联连接的电阻器Rm。结果是缓冲放大器具有高阻抗输入、单端输出和频率相关的分路反馈。

进一步优选的是使用共源共栅配置来减小输入米勒电容,所述输入米勒电容可以使高频处的宽带阻抗匹配劣化。图7是表示根据另一个实施方式的具有高阻抗输入、单端输出、以及提供反馈的逐渐滚降的RC网络的两级低噪声缓冲放大器的部件的电路图。两级低噪声缓冲放大器包括馈入共栅极级的共源极级,以减小从FET12b的漏极到栅极的米勒效应反馈电容。共源共栅配置包括:FET12b,其具有连接到结J1的栅极G、连接到地的源极S和连接到结J3的漏极D;以及FET12a,具有连接到电压源Vb的栅极G、连接到结J3的源极S和连接到结J2的漏极D。在图7中描述的缓冲放大器10的单端输入连接至结点J1,而单端输出连接至FET12a的漏极D。

实现图5中描述的缓冲器的稳定性可能具有挑战性,因为将截止频率放置在操作频带中的要求降低了相位裕度。在高频处,相位是0度;在RC极处,其为45度;并且在RC极点之下,其为90度。这使得难以实现无条件的稳定性,因为电感源阻抗将提供额外的相位。这在图8至图11中示出。

图8和图9分别是绘制两个模拟低噪声缓冲放大器的RC反馈网络的模拟阻抗相位和幅值对接收信号的频率的曲线图:一个模拟缓冲放大器具有如图5所示的一个RC反馈电路(图8中由虚线曲线表示的相位)并且另一个模拟缓冲放大器具有四个(m=4(图6中由实线曲线表示的相位)并联RC电路(图8中由实线曲线表示的相位)。

图10和图11是对分别具有一个RC反馈电路和四个并行RC反馈电路的模拟缓冲放大器绘制相关联的稳定性因子对接收信号的频率的曲线图。如图10所示,RC极点约为80MHz,从这一点到更低频率,稳定性因数远低于1。在优选实施方式中,多个RC网络并联连接以提供反馈的逐渐滚降(见图6)。图11示出了具有四个并联RC电路的模拟缓冲放大器的稳定性因子。这在低得多的频率上提供了大于-30度的相位,从而使得该反馈能够在相位裕度上仅少量减小的情况下被滚降。这对应于更接近于一体的稳定性因子,并且可以在较小的性能劣化的情况下被稳定。建议将潜在不稳定性推至操作频带下方,其中,可通过高通滤波来减轻不稳定性。进一步优选的是,使用图7中所描绘的共源共栅配置来减小可使高频处的宽带阻抗匹配劣化的输入密勒电容。

图12为表示根据一个提出的实现方式(未示出缓冲放大器)的包括有源双锥形天线4和四个有源Vivaldi天线2a-2d的接收阵列30的一些部件的3-D视图的示图。测向系统还包括顶部接地平面20a和底部接地平面20b,顶部接地平面20a和底部接地平面20b均为金属板。双锥形天线4包括上天线锥体8a和下天线锥体8b。下天线锥体8b的截头顶点的孔26在图12中可见。孔26使得能够实现将缓冲放大器连接到上天线锥体8a的电导体的前述反馈通孔。

在图12所示的接收阵列30中,有源Vivaldi天线2a-2d相互正交并且从底部接地平面20b向上延伸。顶部接地平面20a位于有源Vivaldi天线2a-2d的顶部。下天线锥体8b由顶部接地平面20a支撑。用于支撑上天线锥体8a的装置未在图12中示出。

在图12所示的实例中,四个有源Vivaldi天线2a-2d以90度角径向向外延伸。然而,本文提出的接收阵列可具有不同于四个的Vivaldi天线的数目,例如,一个、两个、八个或十二个。Vivaldi天线从中心管24径向向外延伸,中心管24具有与Z轴同轴的轴。接地平面垂直于Z轴。将顶部接地平面20a连接至底部接地平面20b的电导体穿过中心管24。在替代实施方式中,该管本身是导电的。

Vivaldi天线可以是印刷电路板。每个Vivaldi天线的臂可耦接至顶部接地平面和底部接地平面,并且双锥形天线可放置在顶部接地平面上方并且以图3中所描述的方式电耦接至缓冲放大器10。根据一个提出的实现方式,将用于Vivaldi天线的缓冲放大器放置在尽可能靠近天线馈线的相应印刷电路板上。用于双锥形天线的缓冲放大器尽可能靠近天线锥体的顶点放置,天线锥体的顶点可位于下部天线锥8b内部或管24内部。

图13是识别测向系统40的组件的框图,测向系统40包括连接到具有多个通道的接收器32的接收阵列30。测向系统40还包括具有多个输入端口的数字信号处理器36和将来自接收器32的模拟信号转换成数字信号以用于数字信号处理的多个模数转换器34。模数转换器34具有连接到接收器32的输出端口的相应输入端和连接到数字信号处理器36的输入端口的相应输出端。

根据图13中所描绘的所提出的实施方式,测向系统40的接收阵列30包括以下组件:(a)连接到第一缓冲放大器10a的第一Vivaldi天线2a;(b)连接到第二缓冲放大器10b的第二Vivaldi天线2b;(c)连接到第三缓冲放大器10c的第三Vivaldi天线2c;(d)连接到第四缓冲放大器10d的第四Vivaldi天线2d;(e)与第五缓冲放大器10e连接的双锥形天线4。第一至第五缓冲放大器10a-10e的输出连接到接收器32的相应通道。

模拟具有以45度角间隔从中心管径向向外延伸的八个Vivaldi天线的接收阵列的性能。根据图7设计模拟缓冲放大器,其中FETs12a和12b均为栅极长度为0.25微米的GaNFETS。反馈网络包括4个RC电路,加上输入和输出匹配网络。生成接收模型,其基于天线的全波模拟和缓冲放大器的详细噪声模拟来模拟耦合到天线的缓冲器的天线增益和接收器灵敏度。对无源天线(如图12所示,除了包括八个Vivaldi天线之外)和有源天线(包括图7所示的缓冲器)模拟该性能。为了比较,在这两种情况下,假设天线耦合到具有5-dB噪声指数的接收器。

图14是绘制具有如本文所提出的集成缓冲放大器的有源Vivaldi天线的模拟增益和灵敏度益处的曲线图。图15是绘制具有如在本文中提出的集成缓冲放大器的有源双锥形天线的模拟增益和灵敏度益处的曲线图。增益益处是具有缓冲器的所实现的天线增益与不具有缓冲器的所实现的天线增益的比率。对于一阶,该比率是缓冲器的增益,但是阻抗匹配的二阶效应也影响值。灵敏度益处是没有缓冲器的最小可检测信号(MDS)与具有缓冲器的MDS的比率。显然,灵敏度益处高于假设的5-dB接收器噪声系数。这表明,改善不仅仅是由于利用放大器增益克服接收器噪声。而是,这是由于天线与低噪声缓冲器的有利配对。

图16是表示具有集成的缓冲放大器10的有源Vivaldi天线2的几个部件的示图。有源Vivaldi天线2包括一对平衡臂6a和6b,其从天线馈电点18处的喉部区域发散。缓冲放大器10的输出通过导体28连接至接收器(图17中未示出,但是见图13中的接收器32)。

图17是表示根据一个实施方式的印刷电路板11的示图。印刷电路板11包括介电基板14、Vivaldi天线2的两个臂6a和6b、以及缓冲放大器芯片16,缓冲放大器芯片16布置为尽可能合理地靠近臂6a和6b的近端处的馈电点18。Vivaldi天线2的臂6a和6b可以是介电基板14的表面上的金属化层。缓冲放大器芯片16可以是集成电路,其包括被布置成使得芯片16上的馈电触点直接接合到Vivaldi天线2的臂6a和6b的近端处的相应馈电点18的GaN FETs。馈电点18靠近缓冲放大器的FETs的栅极G设置。长度d的传输线连接Vivaldi天线2的臂6a和6b的端部处的馈电点18。这些传输线优选地通过紧邻上述馈电触点38形成FETs的栅极G制造得尽可能短,如图18至图21所示。

图18是表示根据第一实施方式的具有高阻抗输入并且没有反馈的缓冲放大器10’的组件的电路图。图18中描绘的缓冲放大器10’包括一对FETs12a和12b(例如,GaN FETs),被配置为向接收器(图18中未示出;缓冲放大器的偏置网络也未示出)提供差分输出。每个FET具有连接到芯片16的相应馈电触点38的栅极G、连接到公共接地节点的源极S、以及连接到相应缓冲放大器输出的漏极D。差分输出被带到接收器或可选择地第二放大级(未示出)。

图18中所描绘的类型的相应缓冲放大器10’可以替代图13中所描绘的缓冲放大器10a-10e中的每个。在每个实例中,缓冲放大器10’包括直接耦接至Vivaldi或双锥形天线的平衡馈电端子(馈电触点38)的相应一个的差分对共源放大器。该连接可以利用匹配于传统频带中的天线阻抗的传输线进行,但是也可以利用两个导体的另一布置(例如,未布置在传统传输线中的电线或迹线)进行。

图18所示的每个栅极G与芯片16上的相应馈电触点38相隔距离d。根据一个提出的实现方式,天线端子与缓冲放大器10’中的每个FET之间的这种连接的长度d等于在扩展频带的最高频率处的波长(在该实例中为1GHz)。

图19是表示根据第二实施方式的具有高阻抗输入并且没有反馈的缓冲放大器10”的部件的电路图。图19中所示的缓冲放大器10”包括一对FETs12a和12b(例如,GaN FETs)以及被配置为向接收器(图19中未示出;缓冲放大器的偏置网络也未示出)提供单端输出的变压器22。每个FET具有连接到相应馈电触点38的栅极G、连接到公共接地节点的源极S、以及连接到相应结J4和J5的漏极D。更具体地,FET12a的漏极连接到结J4;FET12b的漏极连接到结J5。变压器22包括一对绕组9a和9b。绕组9a跨接点J4和J5连接。绕组9b的一端接地,另一端与缓冲放大器10”的输出端连接。

图20是表示根据第三实施方式的具有高阻抗输入和反馈的缓冲放大器10*的部件的电路图。图20中所示的缓冲放大器10*包括被配置为提供差分输出至接收器的一对FETs12a和12b(例如,GaN FETs)以及被设计为提供输入阻抗的相应高通RC反馈电路3a和3b,该输入阻抗是低频扩展频带中的高阻抗并且与高频传统频带中的天线阻抗相匹配。每个RC反馈电路3a和3b包括串联连接的电阻器R和电容器C,以实现在扩展频带中具有高输入阻抗并且与传统频带中的天线阻抗相匹配的缓冲器。

再次,每个FET具有连接至芯片16的相应馈电触点38的栅极G、连接至公共接地节点的源极S、以及连接至相应缓冲放大器输出的漏极D。差分输出被带到接收器或可选择地第二放大级(未示出)。更具体地,RC反馈电路3a将结点J6连接至结点J7。结J6连接到FET12a的栅极G;结J7连接到FET12a的漏极D。类似地,RC反馈电路3b将结点J8连接至结点J9。结J8连接至FET12b的栅极G;结J9连接到FET12b的漏极D。接点J6和J8进而连接到芯片16上的相应馈电触点38。在一些实施方式中,每个FET12a和12b的输出阻抗优选地被设定为可以等于50欧姆的系统阻抗。电阻器R可以具有50欧姆的电阻;电容器C可以具有2pF的电容。

图21是表示根据第四实施方式的具有高阻抗输入和反馈的缓冲放大器10**的部件的电路图。图21中所描绘的缓冲放大器10**包括一对FETs12a和12b(例如,GaN FETs)以及相应的高通RC反馈电路3a和3b,该高通RC反馈电路被设计成(如之前参照图20所描述的)提供输入阻抗,该输入阻抗在低频扩展频带中是高阻抗并且与高频传统频带中的天线阻抗相匹配。缓冲放大器10**进一步包括变压器22,该变压器被配置成用于(如之前参照图19所描述的)向接收器提供单端输出。

以上公开的所有实施方式的共同方面是每个缓冲放大器包括耦合到In端子和Out端子的跨导级,其中流入跨导级的输出电流I2与输入电压V1(来自天线)乘以增益因子g

跨导级优选地包括一个或多个FETs。在替代实施方式中,可使用其他类型的晶体管(例如,双极晶体管或类似真空装置)代替FETs。在以上所描述的所有实施方式中,技术人员将认识到需要并且能够供应适当的DC偏置电流和电压以实现小信号模拟操作。应进一步理解,“耦合”可以指通过电容耦合、电耦合的AC,并且可以包括高达约100欧姆的小电阻。

在图5和图6所示的第一实施方式中,跨导级包括FET12,其中栅极G耦合到输入端,漏极D耦合到输出端,源极S接地。在图7所示的第二实施方式中,跨导级包括共源共栅布置的FET12a和12b,其中输入耦合到FET12b的栅极G,输出耦合到FET12a的漏极D,FET12b的源极S接地。在图18至图21所示的第三实施方式中,跨导级包括FET12a和12b的差分对,其中差分输入端耦接至FET12a和12b的栅极G,差分输出端耦接至FET12a和12b的漏极D,并且源极S耦接至公共电位。根据第四实施方式,基于上述描述(尽管未在附图中示出),本领域技术人员将清楚,跨导级包括被布置为差分对共源共栅跨导级的四个FET,其中第一差分输入耦合至第一共源共栅级的输入,第二差分输入耦合至第二共源共栅级的输入,第一差分输出耦合至第一共源共栅级的输出,第二差分输出耦合至第二共源共栅级的输出,且第一共源共栅级和第二共源共栅级的地连接于公共电位。

缓冲放大器优选地被设计为使得高于反馈网络的RC截止频率,输入阻抗和最佳噪声阻抗两者都接近天线阻抗。另一期望的特征是设计RC截止频率使得反馈在扩展频带中被最小化,同时保持放大器稳定性和与扩展频带中的天线阻抗相比相对高的输入阻抗。

项1.一种有源双锥形天线(4),包括:

上锥体(8a)和下锥体(8b),上锥体和下锥体的每个包括相应的截头顶点;

第一馈电点和第二馈电点(18),分别连接到上锥体和下锥体的截头顶点;

第一导体(1a)和第二导体(1b),分别连接至第一馈电点和第二馈电点;以及

缓冲放大器(10),包括分别连接至第一导体和第二导体的第一输入端子和第二输入端子,

其中,缓冲放大器具有输入阻抗和输出阻抗,输入阻抗与处于和高于但不低于频率f

其中,第一导体和第二导体的长度小于在频率f

项2.根据项1所述的有源双锥形天线,进一步包括支撑下锥体的接地平面(20)。

项3.根据项1或2所述的有源双锥形天线,其中,缓冲放大器包括跨导级(42a)。

项4.根据项3所述的有源双锥形天线,其中,缓冲放大器进一步包括RC反馈网络,RC反馈网络连接至跨导级。

项5.根据项4所述的有源双锥形天线,其中,RC反馈网络包括多个RC反馈电路(3a,3b)。

项6.根据项4或5所述的有源双锥形天线,其中,跨导级包括场效应晶体管(12),该场效应晶体管具有连接至第一导体的栅极(G)、连接至第二导体的源极/地(S)、以及连接至输出端的漏极(D)。

项7.根据项4-6所述的有源双锥形天线,其中:

跨导级包括布置成共源共栅配置的第一场效应晶体管(12a)和第二场效应晶体管(12b);

第一场效应晶体管(12a)包括连接到第一导体的第一栅极(G);以及

第二场效应晶体管(12b)包括连接至电压源的第二栅极(G)。

项8.根据项3所述的有源双锥形天线,其中,跨导级包括具有分别连接至第一导体和第二导体的相应栅极(G)的差分场效应晶体管对(12a、12b)。

项9.根据项8所述的有源双锥形天线,进一步包括变压器(22),变压器包括第一绕组和第二绕组(9a,9b),其中,第一绕组(9a)的一端连接到第一场效应晶体管的漏极(D),并且另一端连接到第二场效应晶体管的漏极(D)。

项10.一种测向系统,包括:

双锥形天线(4);

第一Vivaldi天线(2a);

接收器(32),具有多个端口;

第一缓冲放大器(10e),具有连接至双锥形天线的输入端并具有连接至多个端口中的第一端口的输出端;以及

第二缓冲放大器(10a),具有连接至第一Vivaldi天线的输入端并具有连接至多个端口中的第二端口的输出端。

项11.根据项10所述的测向系统,还包括布置在双锥形天线和第一Vivaldi天线之间的第一接地平面(20a),其中,双锥形天线和第一Vivaldi天线附接至第一接地平面的相对侧。

项12.根据项10或11所述的测向系统,进一步包括:

第二Vivaldi天线(2b);以及

第三缓冲放大器(10b),具有连接到第二Vivaldi天线的输入端并具有连接到多个端口中的第三端口的输出端。

项13.根据项12所述的测向系统,进一步包括第二接地平面(20b),其中,第一Vivaldi天线和所述第二Vivaldi天线布置在第一接地平面和第二接地平面之间。

项14.根据项11所述的测向系统,其中,第一缓冲放大器包括场效应晶体管(12a)和将场效应晶体管的栅极(G)连接到漏极(D)的RC反馈电路(3a)。

项15.根据项14所述的测向系统,其中,RC反馈电路包括:

电阻器(R),连接到场效应晶体管的栅极(G),当双锥形天线接收具有传统频带中的频率的信号时,电阻器的电阻使第一缓冲放大器的输入阻抗与双锥形天线的阻抗匹配;以及

电容器(C),连接至电阻器并且连接至场效应晶体管的漏极(D),电容器具有防止在从传统频带延伸至小于传统频带的最低频率的频率的延伸频带中的反馈的电容。

项16.根据项10所述的测向系统,其中,双锥形天线被配置成具有:

输入阻抗,该输入阻抗与处于和高于但不低于频率f

输出阻抗,在高于和低于f

项17.根据项16所述的测向系统,还包括将双锥形天线连接到第一缓冲放大器的第一导体(1a)和第二导体(1b),其中:

该双锥形天线包括上锥体(8a)和下锥体(8b),上锥体和下锥体中的每一个包括相应的截头顶点以及连接至该截头顶点的馈电点(18);

第一导体和第二导体分别连接到上锥体和下锥体的馈电点;以及

第一缓冲放大器包括分别连接至第一导体和第二导体的第一输入端和第二输入端,其中,第一导体和第二导体的长度小于在频率f

项18.一种有源锥形天线,包括:

锥体(8),包括截头顶点以及连接至截头顶点的馈电点(18);

接地平面(20);

第一导体和第二导体(1a,1b),分别连接至馈电点和接地平面;以及

缓冲放大器(10),包括分别连接至第一导体和第二导体的第一输入端子和第二输入端子,

其中,缓冲放大器具有输入阻抗和输出阻抗,输入阻抗与处于和高于但不低于频率f

其中,第一导体和第二导体的长度小于在频率f

项19.根据项18所述的有源锥形天线,其中,缓冲放大器包括跨导级(42a)。

项20.根据项19所述的有源锥形天线,其中,跨导级进一步包括场效应晶体管(12),该场效应晶体管包括耦接至第一导体的栅极(G)。

虽然已经参考各种实施方式描述了有源双锥形天线和包括有源双锥形和Vivaldi天线的组合的接收阵列,但是本领域技术人员将理解,在不背离本文的教导的情况下,可以进行各种改变并且等同物可以代替其元件。此外,可以做出许多修改以使本文所公开的实践的概念和缩减适于特定情况。因此,旨在权利要求涵盖的主题不限于所公开的实施方式。

- 一种有源阵列天线接收增益噪声温度比的测试方法

- 有源阵列、有源阵列的制造方法和随机存储器