数字视频数据流接口单元IP核及人工智能芯片

文献发布时间:2023-06-19 09:23:00

技术领域

本发明涉及高清视频传输技术领域,具体涉及一种数字视频数据流接口单元IP核及人工智能芯片。

背景技术

BT1120格式的数字视频数据流广泛用于摄像机、各类安防设备及视频工作站中,可由专门的视频解码芯片完成。BT1120数据流中不仅含有有效的视频数据、辅助数据,还包含无效的消隐数据,因此如何对输入的BT1120数据流进行有效数据的分离,然后把有效数据转化成用户需求的数据格式显得十分重要。

BT1120格式数字视频流的处理有采用单片机或数字信号处理器通过软件编程处理,要么处理速度慢,实时性不好,要么需要额外提供显示时序控制器,且开发周期长。可使用专门的ASIC芯片来处理,但在图像分辨率和帧率要求较高的场合无法获得令人满意的效果,且灵活性和可扩展性不佳。

SOC芯片的发展完美地解决了这些问题,因此如何在芯片上集成支持BT1120数据流的视频输入接口IP成为研究的热点。

发明内容

本发明旨在至少解决现有技术中存在的技术问题之一。为此,本发明提出一种数字视频数据流接口单元IP核,通过APB总线实现对寄存器的配置,可实现对外部输入的遵循BT1120协议的16位模式数据进行解析,提取出有效的图像数据并通过AXI总线将数据存储到存储器中,并产生中断信号。

本发明还提出一种包括上述数字视频数据流接口单元IP核的人工智能芯片。

根据本发明的实施例的第一方面的一种数字视频数据流接口单元IP核,包括:

数据采样处理模块,用于通过BT1120对应的数据时钟,对BT1120的16位并行数据进行解析处理;时序分析模块,用于对所述数据采样处理模块提供的信息进行分析;AXI接口时序处理模块,用于根据寄存器的配置,将所述时序分析模块解析出的有效图像数据进行存储转发并产生中断;以及寄存器配置模块,用于配置所述数据采样处理模块、时序分析模块以及AXI接口时序处理模块的寄存器,使所述数据采样处理模块、时序分析模块以及AXI接口时序处理模块根据相应的参数工作。

根据本发明的一些实施例,所述数据采样处理模块包括:时钟信号处理单元,用于将外部输出的BT1120数据对应的时钟信号进行0°和180°的处理。

根据本发明的一些实施例,所述数据采样处理模块包括:特征信号提取单元,用于对输入的16位并行数据按照BT1120协议进行解析,提取出XYZ、EAV及SAV特征信号。

根据本发明的一些实施例,所述时序分析模块包括:时序生成单元,用于分析所述特征信号,产生时序控制信号,所述时序控制信号包括行、场及帧时序控制信号。

根据本发明的一些实施例,所述时序生成单元还用于解析出有效数据的图像数据信号以及帧开始和帧结束标志。

根据本发明的一些实施例,所述AXI接口时序处理模块用于将所述时序分析模块解析出的有效图像数据存储到缓存异步FIFO中。

根据本发明的一些实施例,所述AXI接口时序处理模块用于向AXI总线发送请求,获取授权后,按照AXI3协议格式将存储的有效图像数据发送到所述AXI总线上挂接的存储设备中。

根据本发明的一些实施例,所述AXI接口时序处理模块用于将所述解析出的图像有效数据存储到内部异步FIFO中,当缓存到一定数量的数据后,按照AXI协议向总线发送写缓存请求,当得到授权后,以突发传输的方式向所述总线上挂接的存储设备写数据。

根据本发明的一些实施例,突发传输长度由寄存器配置为1至16。

根据本发明的一些实施例,所述AXI接口时序处理模块用于将一帧图像数据转存到存储设备中后,产生高电平中断给处理器。

根据本发明实施例的一种数字视频数据流接口单元IP核,至少具有如下有益效果:

本发明通过设计带有中断支持的用于人工智能芯片的BT1120接口单元IP核,通过设置相应的配置寄存器进行管理,可以对BT1120协议数据进行正确解析,并且对输入的BT1120数据流进行有效数据的分离,然后把有效数据转化成用户需求的数据格式。

根据本发明的实施例的第二方面的一种人工智能芯片,包括:处理器、APB总线、AXI4总线、存储设备以及本发明实施例第一方面的任一项所述的用于人工智能芯片的BT1120接口单元IP核;所述处理器用于通过所述APB总线对所述用于人工智能芯片的BT1120接口单元IP核进行配置,接收AXI接口时序处理模块产生的高电平中断,以及通过读中断状态寄存器的方式清除中断。

由于本发明实施例的一种人工智能芯片包括数字视频数据流接口单元IP核,因此具有本发明第一方面的所有有益效果。

本发明的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

附图说明

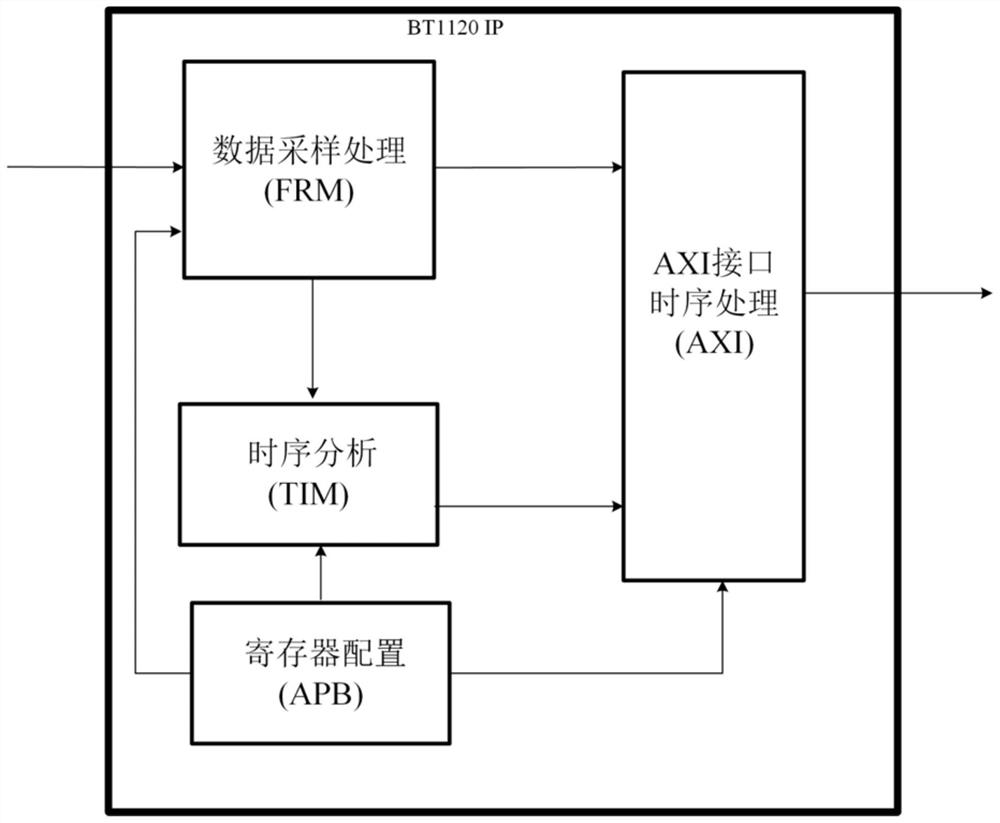

图1是本发明实施例的结构框图;

图2是本发明实施例的内部结构框图。

具体实施方式

以下将结合实施例和附图对本发明的构思、具体结构及产生的技术效果进行清楚、完整的描述,以充分地理解本发明的目的、方案和效果。

参照图1,本发明实施例提供了一种数字视频数据流接口单元IP核,包括:数据采样处理模块,用于通过BT1120对应的数据时钟,对BT1120的16位并行数据进行解析处理;时序分析模块,用于对数据采样处理模块提供的信息进行分析;AXI接口时序处理模块,用于根据寄存器的配置,将时序分析模块解析出的有效图像数据进行存储转发并产生中断;寄存器配置模块,用于配置数据采样处理模块、时序分析模块以及AXI接口时序处理模块的寄存器,使数据采样处理模块、时序分析模块以及AXI接口时序处理模块根据相应的参数工作。

本实施例中还包括AXI4-Lite总线接口,遵守AXI4.0总线标准,通过AXI4-Lite实现GPIO与主机之间的通讯。

在一些实施例中,数据采样处理模块包括时钟信号处理单元,用于将外部输出的BT1120数据对应的时钟信号进行0°和180°的处理。

在一些实施例中,数据采样处理模块包括特征信号提取单元,用于对输入的16位并行数据按照BT1120协议进行解析,提取出XYZ、EAV及SAV特征信号。

在一些实施例中,时序生成单元,用于分析所述特征信号,产生时序控制信号,所述时序控制信号包括行、场及帧时序控制信号。

在一些实施例中,时序生成单元用于解析出有效数据的图像数据信号以及帧开始和帧结束标志。

在一些实施例中,AXI接口时序处理模块用于将时序分析模块解析出的有效图像数据存储到缓存异步FIFO中。

在一些实施例中,AXI接口时序处理模块用于向AXI总线发送请求,获取授权后,按照AXI3协议格式将存储的有效图像数据发送到AXI总线上挂接的存储设备中。

在一些实施例中,AXI接口时序处理模块用于将所述解析出的图像有效数据存储到内部异步FIFO中,当缓存到一定数量的数据后,按照AXI协议向总线发送写缓存请求,当得到授权后,以突发传输的方式向所述总线上挂接的存储设备写数据。

在一些实施例中,突发传输长度由寄存器配置为1至16。

在一些实施例中,AXI接口时序处理模块用于将一帧图像数据转存到存储设备中后,产生高电平中断给处理器。

参照图2,在本实施例中,将BT1120接口单元IP核作为人工智能芯片OAI 18处理器中AXI4总线的片上外设。处理器通过APB总线对BT1120接口单元进行配置后,外部设备输出BT1120协议格式的数据和时钟信号到BT1120接口单元IP端口,该模块能将符合协议的图像数据解析出来并存储到缓存中。接收完一帧图像数据后,产生中断信号给处理器。

如图2所示,本实施例包括数据采样处理模块(FRM)、时序分析模块(TIM)、AXI接口时序处理模块(AXI)以及寄存器配置模块(APB)。

本实施例工作时,该BT1120接收单元支持处理的BT1120数据时钟为74.25MHz,一帧有效数据为1920*1080,支持每秒30帧的逐行数据模式。处理器通过APB总线对BT1120接口单元进行配置,为了降低外部输入的数据和时钟的相位关系要求,BT1120接口单元首先将外部输出的BT1120数据对应的时钟信号进行0°和180°的相位处理,再利用该时钟对输入的16位并行数据进行采样,后续模块对这些数据按照BT1120协议进行解析,提取出XYZ、EAV、SAV等特征信号,进而对数据流进行分析,产生行、场、帧等时序控制信号,并解析出图像对应的有效数据信息,将这些信息数据存储到内部异步FIFO中,当缓存到一定数量的数据后,AXI模块按照AXI协议向总线发送写缓存请求,当得到授权后,以突发传输的方式向人工智能芯片OAI18中的存储设备写数据,突发传输长度支持由寄存器配置为1-16。将一帧图像数据转存到存储设备中后,产生高电平中断给处理器,处理器可通过读中断状态寄存器的方式清除中断,否则中断一直有效。BT1120接收单元支持设置16个不同的存储地址,即可连续存储16帧标准的1920*1080P的图像在存储器中不同的地址。解析完一帧数据后,BT1120接收单元恢复到idle状态,等待下一帧数据的到来,再按照上述方式继续。

以上所述,只是本发明的较佳实施例而已,本发明并不局限于上述实施方式,只要其以相同的手段达到本发明的技术效果,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明保护的范围之内。在本发明的保护范围内其技术方案和/或实施方式可以有各种不同的修改和变化。

- 数字视频数据流接口单元IP核及人工智能芯片

- 神经元计算单元、神经元计算模块及人工神经网络计算核