绝缘体上覆硅背侧触点

文献发布时间:2023-06-19 09:29:07

背景

优先权要求

本专利申请要求于2018年5月31日提交的题为“SILICON-ON-INSULATOR BACKSIDECONTACTS(绝缘体上覆硅背侧触点)”的申请No.15/993,679的优先权,该申请被转让给本申请受让人并由此通过援引明确纳入于此。

技术领域

本公开的各方面涉及绝缘体上覆硅器件,尤其涉及用于绝缘体上覆硅背侧触点的结构和制造方法。

背景技术

绝缘体上覆硅(SOI)技术是指在半导体制造(尤其是微电子学)中使用分层的硅-绝缘体-硅基板代替常规硅基板以减少寄生器件电容,藉此提高性能。使用SOI器件构建的集成电路可以展示出比与之相当的基于体块的集成电路快约30%的处理速度,并且功耗降低多达80%,这使其对于移动设备而言是理想的。SOI芯片还降低了软差错率,软差错率是由宇宙射线和天然放射性背景信号引起的数据损坏。SOI晶体管提供使得CMOS架构更可伸缩的独有机会。氧化物埋层(背绝缘层)限制了深亚微米体块器件上可能存在的穿通。

在一些示例中,层转移工艺被用于将SOI晶片的顶部有源器件部分转移到处置晶片。在该工艺中,SOI晶片的顶部部分被接合到处置晶片,并且SOI晶片的体块基板层(牺牲基板)被移除。除了前侧连接系统之外,该工艺还使得能够形成背侧连接系统。例如,背绝缘层可被减薄。可以在背绝缘层中形成开口,使得可以形成背侧触点以连接到诸如MOSFET的源极、漏极和/或主体之类的器件。另外,可以在背绝缘层上形成一个或多个金属层和通孔,以将电源、接地和/或信号路由到器件。与前侧连接系统中的前侧触点以及金属层和通孔相比,背侧触点以及一个或多个金属层和通孔形成背侧连接系统。通常需要源极和漏极硅化物来促成前侧或背侧连接系统与各器件之间的良好连接。常规地,可能需要双侧硅化工艺,从而形成在源极或漏极的前面用于连接至前侧连接系统的前侧硅化物层、以及在源极或漏极的背面用于连接至背侧连接系统的背侧硅化物层。

在形成各器件和前侧连接系统之后形成背侧硅化物层。因此,形成背侧硅化物层可能造成若干问题。它增加了工艺复杂性,导致附加成本和产量损失。来自额外硅化工艺的较高热量可能会对器件性能和前侧连接系统的完整性造成不利影响。因此,在没有附加的背侧硅化物层的情况下实现背侧连接系统将是有益的。

概述

以下给出对一个或多个实现的简化概述以提供对此类实现的基本理解。此概述不是所有构想到的实现的详尽综览,并且既非旨在标识所有实现的关键性或决定性要素亦非试图界定任何或所有实现的范围。本概述的唯一目的是要以简化形式给出与一个或多个实现相关的概念以作为稍后给出的更详细描述之序。

在一个方面,一种装置包括:在背绝缘层上具有作为源极或漏极的扩散区的SOIMOSFET,其中该扩散区具有前扩散侧以及与该前扩散侧相对的背扩散侧;在该前扩散侧上具有面向该扩散区的背硅化物侧以及与该背硅化物侧相对的前硅化物侧的硅化物层;以及连接至该硅化物层的背侧触点,其中该背侧触点的至少一部分在该背绝缘层中。

在另一方面,一种方法包括:提供SOI晶片,该SOI晶片具有背绝缘层、在该背绝缘层上各自具有作为源极或漏极的扩散区的一个或多个MOSFET、以及在该扩散区上具有面向该扩散区的背硅化物侧以及与该背硅化物侧相对的前硅化物侧的前侧硅化物层;形成穿过该背绝缘层和该扩散区的一部分的触点开口;以及在该触点开口中形成背侧触点,其中该背侧触点通过该背硅化物侧连接至该前侧硅化物层。

在另一方面,一种方法包括:提供SOI晶片,该SOI晶片具有背绝缘层、以及各自具有作为MOSFET的源极或漏极的扩散区的一个或多个该MOSFET,其中该扩散区具有前扩散侧和背扩散侧;从该前扩散侧在该扩散区中的所选凹陷区域中形成凹陷;从该前扩散侧和该凹陷在该扩散区中形成硅化物层,其中该硅化物层具有面向该扩散区的背硅化物侧以及与该背硅化物侧相对的前硅化物侧,并且其中该背硅化物侧在所选凹陷区域下方接触该背绝缘层;在该背绝缘层中形成触点开口;以及在该触点开口中形成背侧触点,其中该背侧触点通过该背硅化物侧在所选凹陷区域下方连接至该硅化物层。

在另一方面,一种方法包括:提供SOI晶片,该SOI晶片具有背绝缘层、各自具有作为MOSFET的源极或漏极的扩散区的一个或多个MOSFET、以及毗邻于该扩散区的浅沟槽隔离开口,其中该扩散区具有前扩散侧、背扩散侧和侧壁,其中该侧壁也是该浅沟槽隔离开口的侧壁;从该前扩散侧和侧壁在该扩散区中形成硅化物层,其中该硅化物层通过该侧壁接触该背绝缘层;在该背绝缘层中形成触点开口;以及在该触点开口中形成背侧触点,其中该背侧触点通过该侧壁连接至该硅化物层。

为了达成前述及相关目的,这一个或多个实现包括在下文充分描述并在权利要求中特别指出的特征。以下说明和所附插图详细阐述了这一个或多个实现的某些解说性方面。但是,这些方面仅仅是指示了可采用各个实现的原理的各种方式中的若干种,并且所描述的实现旨在涵盖所有此类方面及其等效方案。

附图简述

图1解说了根据本公开的某些方面的示例双侧硅化物双侧连接系统SOI器件。

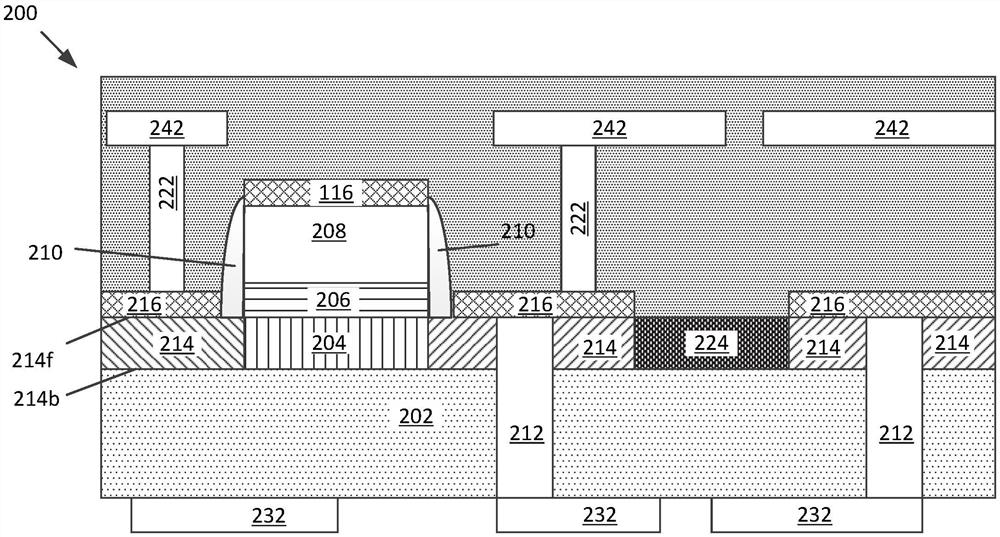

图2解说了根据本公开的某些方面的示例性单侧硅化物双侧连接系统SOI器件。

图3a-3d解说了根据本公开的某些方面的另一示例性单侧硅化物双侧连接系统SOI器件。

图4a-4c解说了根据本公开的某些方面的又一示例性单侧硅化物双侧连接系统SOI器件。

图5解说了根据本公开的某些方面的用于制造示例性单侧硅化物双侧连接系统SOI器件的示例性方法500。

图6解说了根据本公开的某些方面的用于制造示例性单侧硅化物双侧连接系统SOI器件的另一示例性方法600。

图7解说了根据本公开的某些方面的用于制造示例性单侧硅化物双侧连接系统SOI器件的又一示例性方法700。

详细描述

以下结合附图阐述的详细描述旨在作为各种方面的描述,而无意表示可实践本文中所描述的概念的仅有方面。本详细描述包括具体细节以提供对各种概念的理解。然而,对于本领域技术人员将显而易见的是,没有这些具体细节也可以实践这些概念。在一些实例中,以框图形式示出众所周知的结构和组件以便避免湮没此类概念。

绝缘体上覆半导体(SOI)器件因其出色的电属性(包括较低阈值电压、较小寄生电容、较小电流泄漏和良好开关属性等)而被广泛使用。层转移技术使互连布线能够在器件的两侧上,并且在微电子、微机电系统(MEMS)、光学器件和光电领域开辟了新的材料、器件、集成和系统类别。

通常需要双侧硅化工艺来促成双侧布线。图1解说了根据本公开的某些方面的示例双侧硅化物双侧连接系统SOI器件。SOI器件100包括背绝缘层102(例如,包括SiO

每个扩散区114具有前扩散侧114f和背扩散侧114b。每个扩散区114在前扩散侧114f被硅化以具有前侧硅化物层116(例如,包括CoSi或TiSi)。前侧硅化物层116也可以在栅极导电层108之中和之上。扩散区114中的一些也在背扩散侧114b被硅化以具有背侧硅化物层118。前侧硅化物层116和背侧硅化物层118为MOSFET的源极、漏极和栅极提供低电阻连接。

SOI器件100进一步包括连接至相应前侧硅化物层116的一个或多个前侧触点122(例如,包括W、Ti、Cu或Al)、以及连接至相应背侧硅化物层118的一个或多个背侧触点112(例如,包括W、Ti、Cu或Al)。另外,一个或多个前金属层和通孔142(例如,包括Cu或Al)耦合至一个或多个前侧触点122,并且一起形成前侧连接系统。类似地,一个或多个背金属层和通孔132(例如,包括Cu或Al)耦合至背侧触点112,并且一起形成背侧连接系统。

图1中示出的双侧硅化工艺实现了双侧连接系统,从而允许同一管芯中的前侧连接系统和背侧连接系统两者。然而,该技术以增加的工艺复杂性、更高的热预算、潜在的产量损失和潜在的性能降级为代价,提高了电路和互连密度和布通率。

图2解说了根据本公开的某些方面的示例性单侧硅化物双侧连接系统SOI器件。类似于SOI器件100,SOI器件200包括背绝缘层202(例如,包括SiO

每个扩散区214具有前扩散侧214f和背扩散侧214b。每个扩散区214在前扩散侧214f中被硅化以具有前侧硅化物层216(例如,包括CoSi或TiSi)。每个前侧硅化物层216具有面向相应一个扩散区214的背硅化物侧216b以及与背硅化物侧216b相对的前硅化物侧216f。前侧硅化物层216也在相应一个栅极导电层208之中和之上。前侧硅化物层216为MOSFET的源极、漏极和/或栅极触点提供低电阻连接。

SOI器件200还包括通过前硅化物侧216f连接至前侧硅化物层216的一个或多个前侧触点222(例如,包括W、Ti、Cu或Al)。一个或多个前金属层和通孔242耦合至前侧触点222,并且一起形成前侧连接系统。然而,与SOI器件100不同,SOI器件200不包括背侧硅化物层。替代地,一个或多个背侧触点212(例如,包括W、Ti、Cu或Al)在背绝缘层202和相应的扩散区214两者中,并且通过背硅化物侧216b直接连接至相应的前侧硅化物层216。一个或多个背金属层和通孔232耦合至背侧触点212,并且一起形成SOI器件200的背侧连接系统。

如图2中解说的,为了使背侧触点212低电阻地与扩散区214连接,背侧触点212必须穿过扩散区214的一部分以到达前侧硅化物层216。背侧触点212的一部分被扩散区214包围,而一部分被背绝缘层102包围。这需要在前侧硅化物层216下方进行选择性扩散硅蚀刻,以使蚀刻在相应的背硅化物侧216b处停止。可能需要附加的端点感测来进行控制,以避免蚀刻过度或蚀刻不足。

如图2中还解说的,并非每个前侧硅化物层都必须耦合至前侧触点。同样,并非每个前侧硅化物层都必须耦合至背侧触点。另外,前侧硅化物层可耦合至前侧触点和背侧触点两者或不耦合至两者。

前侧触点222和背侧触点212两者都可包括任何合适的一种或多种导电材料(诸如W、Ti、Al或Cu)。可以沿着前侧触点和/或背侧触点的侧壁形成导电扩散势垒。例如,可以沿着前侧触点和/或背侧触点的侧壁形成Ti/TiN衬里。

图3a-3d解说了根据本公开的某些方面的另一示例性单侧硅化物双侧连接系统SOI器件。在图3a中,提供了起始SOI晶片。起始SOI晶片包括牺牲基板362、牺牲基板362上的背绝缘层302、背绝缘层302上各自由作为源极或漏极的扩散区314形成的一个或多个MOSFET、作为沟道的主体区304、栅极绝缘层306、在栅极绝缘层306上的栅极导电层308、和间隔件310。每个扩散区314具有前扩散侧314f和背扩散侧314b。起始SOI晶片还包括浅沟槽隔离区324,以隔离两个或更多个扩散区314。

在图3b中,扩散区314中的一些在前扩散侧314f被图案化和蚀刻,以在所选凹陷区域处形成凹陷334。在所选凹陷区域处的扩散区314被减薄至厚度D。厚度D被选择,使得随后的硅化工艺将消耗所选凹陷区域中的所有扩散硅。

在图3c中,对栅极导电层308以及从前扩散侧314f对包括所选凹陷区域的扩散区314执行硅化工艺。作为结果,在扩散区314和栅极导电层308上形成前侧硅化物层316。每个前侧硅化物层316具有面向相应扩散区314的背硅化物侧316b以及与背硅化物侧316b相对的前硅化物侧316f。

在所选凹陷区域中,因为硅的厚度被减小得足够小,所以硅化工艺会消耗所有剩余的扩散硅。相应前侧硅化物层316的前硅化物侧316f和背硅化物侧316b两者均不是平坦的,而是在所选凹陷区域中向下弯曲。前硅化物侧316f的一部分可以与前扩散侧314f处于相同水平、处于其下方或上方。例如,前硅化物侧316f中未在所选凹陷区域中的部分可处于前扩散侧314f上方,而前硅化物侧316f中在所选凹陷区域中的部分可处于前扩散侧314f下方。此外,前侧硅化物层316的背硅化物侧316b的一部分(诸如前侧硅化物层316中在所选凹陷区域中的部分)接触背绝缘层302。

在图3d中,在形成前侧硅化物层316之后,一个或多个前侧触点322(例如,包括W、Ti、Cu或Al)通过前硅化物侧316b连接至相应的前侧硅化物层316,并且一个或多个前金属层和通孔342耦合至前侧触点322。它们一起形成前侧连接系统。

在形成前侧连接系统之后,处置晶片(未示出)被接合到起始SOI晶片。在接合处置晶片(未示出)之后,移除牺牲基板362,从而曝露背绝缘层302(其可被进一步减薄)。一个或多个背侧触点312(例如,包括W、Ti、Cu或Al)形成在背绝缘层302中,并且在所选凹陷区域下方通过背硅化物侧316b直接连接至相应的前侧硅化物层316。由于前侧硅化物层316在所选凹陷区域中的部分接触背绝缘层302,因此一个或多个背侧触点312不必穿过扩散区314,从而节省了选择性蚀刻的过程。

在形成背侧触点312之后,形成耦合至背侧触点312的一个或多个背金属层和通孔332。它们一起形成背侧连接系统。

如图3d中解说的,并非每个前侧硅化物层都必须耦合至前侧触点。同样,并非每个前侧硅化物层都必须耦合至背侧触点。另外,前侧硅化物层可耦合至前侧触点和背侧触点两者或不耦合至两者。因此,不必在每个扩散区314中形成凹陷334。仅耦合至背侧连接系统的扩散区314将形成凹陷334。

前侧触点322和背侧触点312两者都可包括任何合适的一种或多种导电材料(诸如W、Ti、Al或Cu)。可以沿着前侧触点和/或背侧触点的侧壁形成导电扩散势垒。例如,可以沿着前侧触点和/或背侧触点的侧壁形成Ti/TiN衬里。

图4a-4c解说了根据本公开的某些方面的又一示例性单侧硅化物双侧连接系统SOI器件。在图4a中,提供了起始SOI晶片。起始SOI晶片包括牺牲基板462、牺牲基板462上的背绝缘层402、背绝缘层402上各自由作为源极或漏极的扩散区414形成的一个或多个MOSFET、作为沟道的主体区404、栅极绝缘层406、在栅极绝缘层406上的栅极导电层408、和间隔件410。每个扩散区414具有前扩散侧414f和背扩散侧414b。另外,在两个或更多个扩散区414之间存在一个或多个浅沟槽隔离开口434。该一个或多个浅沟槽隔离开口434处于适当位置以用于稍后将形成的浅沟槽隔离。扩散区414的侧壁434s也是相应的一个或多个浅沟槽隔离开口434的侧壁。

在图4b中,对栅极导电层408以及从前扩散侧414f对包括该一个或多个浅沟槽隔离开口434中的侧壁434s的扩散区414执行硅化工艺。作为结果,在扩散区414和栅极导电层408上形成前侧硅化物层416。在该一个或多个浅沟槽隔离开口434中,前侧硅化物层416也形成在侧壁434s处,并且结束于背绝缘层402。

在图4c中,在形成前侧硅化物层416之后,该一个或多个浅沟槽隔离开口434填充有电介质材料(例如,SiO2)以形成浅沟槽隔离区424。一个或多个前侧触点422(例如,包括W、Ti、Cu或Al)被形成以连接至相应的前侧硅化物层416。一个或多个前金属层和通孔442被形成以耦合至前侧触点422。它们一起形成前侧连接系统。

在形成前侧连接系统之后,处置晶片(未示出)被接合到起始SOI晶片。在接合处置晶片(未示出)之后,移除牺牲基板462,从而曝露背绝缘层402(其可被进一步减薄)。一个或多个背侧触点412(例如,包括W、Ti、Cu或Al)形成在背绝缘层402中,并且通过侧壁434s直接连接至相应的前侧硅化物层416。由于前侧硅化物层416在侧壁434s处的部分接触背绝缘层302,因此一个或多个背侧触点412不必穿过扩散区314,从而节省了选择性蚀刻的过程。

在形成背侧触点412之后,形成耦合至背侧触点412的一个或多个背金属层和通孔432。它们一起形成背侧连接系统。

如图4c中解说的,并非每个前侧硅化物层都必须耦合至前侧触点。同样,并非每个前侧硅化物层都必须耦合至背侧触点。另外,前侧硅化物层可耦合至前侧触点和背侧触点两者或不耦合至两者。

前侧触点422和背侧触点412两者都可包括任何合适的一种或多种导电材料(诸如W、Ti、Al或Cu)。可以沿着前侧触点和/或背侧触点的侧壁形成导电扩散势垒。例如,可以沿着前侧触点和/或背侧触点的侧壁形成Ti/TiN衬里。

图5解说了根据本公开的某些方面的用于制造示例性单侧硅化物双侧连接系统SOI器件的示例性方法500。在502,提供起始SOI晶片。该起始SOI晶片包括牺牲基板、背绝缘层(例如,背绝缘层302)、在该绝缘层上各自由作为源极或漏极的扩散区(例如,扩散区214)形成的一个或多个MOSFET、作为沟道的主体区(例如,主体区204)、栅极绝缘层(例如,栅极绝缘层206)、在该栅极绝缘层上的栅极导电层(例如,栅极导电层208)、和间隔件(例如,间隔件210)。起始SOI晶片还包括牺牲基板和用于隔离两个或更多个扩散区的浅沟槽隔离区(例如,浅沟槽隔离区224)。在扩散区和栅极绝缘层之中和之上形成前侧硅化物层(例如,前侧硅化物层216)。一个或多个前侧触点(例如,前侧触点222)连接至相应的前侧硅化物层。一个或多个前金属层和通孔(例如,前金属层和通孔242)耦合至前侧触点。前侧触点以及前金属层和通孔一起形成前侧连接系统。

在504,SOI晶片被接合到处置晶片。牺牲基板随后被移除,从而曝露背绝缘层(其可被进一步减薄)。

在506,通过图案化和蚀刻该背绝缘层和扩散区来形成一个或多个触点开口。该一个或多个触点开口形成在扩散区下方。这些开口必须穿过扩散区的一部分并且在前侧硅化物层处停止。这需要选择性地蚀刻在前侧硅化物层下方的扩散硅。可能需要附加的端点感测来进行控制,以避免蚀刻过度或蚀刻不足。

在508,在该一个或多个触点开口中形成一个或多个背侧触点(例如,背侧触点212)。背侧触点通过前侧硅化物层低电阻地连接至扩散区。

在510,一个或多个背金属层和通孔(例如,背金属层和通孔232)被形成以耦合至背侧触点,并且一起形成用于该SOI器件的背侧连接系统。

图6解说了根据本公开的某些方面的用于制造示例性单侧硅化物双侧连接系统SOI器件的另一示例性方法600。在602,提供了起始SOI晶片。该起始SOI晶片包括牺牲基板(例如,牺牲基板362)、在该牺牲基板上的背绝缘层(例如,背绝缘层302)、在该绝缘层上各自由作为源极或漏极的扩散区(例如,扩散区314)形成的一个或多个MOSFET、作为沟道的主体区(例如,主体区304)、栅极绝缘层(例如,栅极绝缘层306)、在该栅极绝缘层上的栅极导电层(例如,栅极导电层308)、和间隔件(例如,间隔件310)。每个扩散区具有前扩散侧和背扩散侧。起始SOI晶片还可包括用于隔离两个或更多个扩散区的浅沟槽隔离区(例如,浅沟槽隔离区324)。

在604,从前扩散侧图案化和蚀刻一个或多个扩散区以在所选凹陷区域处形成凹陷(例如,凹陷334)。在所选凹陷区域处的扩散区被减薄至厚度D。厚度D使得随后的硅化工艺将消耗所选凹陷区域中的所有扩散硅。

在606,从前扩散侧在包括所选凹陷区域的扩散区中执行硅化工艺以形成前侧硅化物层(例如,前侧硅化物层316)。在所选凹陷区域中,因为扩散硅的厚度被减小得足够小,所以前侧硅化物层接触背绝缘层。

在608,形成前金属连接系统,该前金属连接系统包括耦合至前侧硅化物层的前侧触点(例如,前侧触点322)以及耦合至这些前侧触点的一个或多个前金属层和通孔(例如,前金属层和通孔342)。

在610,该起始SOI晶片被接合到处置晶片。牺牲基板随后被移除,从而曝露背绝缘层(其可被进一步减薄)。

在612,通过图案化和蚀刻该背绝缘层来形成一个或多个触点开口。该一个或多个触点开口形成在扩散区的所选凹陷区域下方。该一个或多个触点开口在所选凹陷区域下方接触前侧硅化物层。

在614,在该一个或多个触点开口中形成一个或多个背侧触点(例如,背侧触点312)。背侧触点通过前侧硅化物层低电阻地连接至扩散区。

在616,形成耦合至背侧触点的一个或多个背金属层和通孔(例如,背金属层和通孔332)。它们一起形成用于SOI器件的背侧连接系统。

图7解说了根据本公开的某些方面的用于制造示例性单侧硅化物双侧连接系统SOI器件的又一示例性方法600。在702,提供起始SOI晶片。该起始SOI晶片包括牺牲基板(例如,牺牲基板462)、在该牺牲基板上的背绝缘层(例如,背绝缘层402)、在该绝缘层上各自由作为源极或漏极的扩散区(例如,扩散区414)形成的一个或多个MOSFET、作为沟道的主体区(例如,主体区404)、栅极绝缘层(例如,栅极绝缘层406)、在该栅极绝缘层上的栅极导电层(例如,栅极导电层408)、和间隔件(例如,间隔件410)。每个扩散区具有前扩散侧和背扩散侧。另外,在两个或更多个扩散区之间存在一个或多个浅沟槽隔离开口(例如,浅沟槽隔离开口434)。该一个或多个浅沟槽隔离开口处于适当位置以用于稍后将形成的浅沟槽隔离。扩散区的侧壁(例如,侧壁434s)也是该一个或多个浅沟槽隔离开口的侧壁。

在704,对栅极导电层以及从前扩散侧对包括该一个或多个浅沟槽隔离开口中的侧壁的扩散区执行硅化工艺。作为结果,从前扩散侧和侧壁在扩散区中形成前侧硅化物层(例如,前侧硅化物层416)。通过侧壁形成的前侧硅化物层接触背绝缘层。

在形成前侧硅化物层之后,浅沟槽隔离开口填充有电介质材料。随后在706形成前金属连接系统,该前金属连接系统包括连接至前侧硅化物层的前侧触点(例如,前侧触点422)以及耦合至这些前侧触点的一个或多个前金属层和通孔(例如,前金属层和通孔442)。

在形成前侧连接系统之后,在708,处置晶片在前侧被接合到起始SOI晶片。牺牲基板随后被移除,从而曝露背绝缘层(其可被进一步减薄)。

在710,通过图案化和蚀刻该背绝缘层来形成一个或多个触点开口。该一个或多个触点开口形成在扩散区下方。该一个或多个触点开口通过侧壁接触前侧硅化物层。

在712,在该一个或多个触点开口中形成一个或多个背侧触点(例如,背侧触点412)。背侧触点通过侧壁穿过前侧硅化物层低电阻地连接至扩散区。

在714,耦合至背侧触点的一个或多个背金属层和通孔(例如,背金属层和通孔432)被形成,并且一起形成背侧连接系统。

提供对本公开的先前描述是为使得本领域任何技术人员皆能够制作或使用本公开。对本公开的各种修改对本领域技术人员而言将容易是显而易见的,并且本文中所定义的普适原理可被应用到其他变型而不会脱离本公开的精神或范围。由此,本公开并非旨在被限定于本文中所描述的示例,而是应被授予与本文中所公开的原理和新颖特征相一致的最广范围。

- 绝缘体上覆硅背侧触点

- 具有背侧应变拓扑结构的绝缘体上覆半导体