信道盲检测方法和装置以及通信装置和存储介质

文献发布时间:2023-06-19 09:29:07

技术领域

本发明涉及通信技术领域,尤其涉及一种信道盲检测方法和装置以及通信装置和存储介质。

背景技术

NB-IoT(Narrow Band Internet of Things,窄带物联网)系统具有低速率、低功耗、低成本、高容量、广覆盖、多连接等特点。NB-IoT的NPBCH(Narrowband physicalbroadcast channel,窄带物理广播信道)用于承载系统广播信息的MIB-NB(masterinformation block-Narrow Band,窄带主信息块)。MIB-NB信息包括SIB1(SystemInformation Block,系统信息块)的调度信息和操作模式类型等。

在下行控制信息的发送端确定需要发送的相关数据之后,对MIB-NB信息依次进行CRC(Cyclic Redundancy Check,校循环冗余校验码)校验、信道编码、速率匹配、加绕、调制、映射预处理和资源映射等处理,将进行上述处理后的信息发送。接收端若需要接收MIB-NB信息,则需要对该MIB-NB信息进行盲检测,即在计算得到的搜索空间上搜索该MIB-NB信息所在的位置,对该位置的MIB-NB信息进行译码,并依次对译码后的MIB-NB信息进行解资源映射、解速率匹配、解扰、解信道编码和CRC校验等处理,若经CRC校验后,如校验结果正确,则盲检测成功。

但是,现有技术的盲检测方法需要占用较大的缓存,同时计算量也比较大。

发明内容

有鉴于此,本发明实施例的目的在于提供一种信道盲检测方法和装置以及通信装置和存储介质,可以减小解速率匹配的缓存和计算量,提高盲检测效率。

第一方面,本发明实施例提供了一种信道盲检测方法,所述方法包括:

接收窄带物理广播信道NPBCH在一个子周期内发送的至少一个子帧信号;

获取所述子帧信号在候选天线端口数量和候选子周期帧头索引下对应的第一比特序列;

根据所述候选子周期帧头索引确定所述第一比特序列的起始位置;

根据所述起始位置对所述第一比特序列进行解速率匹配以获取第二比特序列;

对所述第二比特序列进行解码处理以获取对应的第三比特序列;

对所述第三比特序列进行校验以获取校验结果;以及

将校验结果正确的第三比特序列对应的候选天线端口数量和候选子周期帧头索引确定为所述子帧信号对应的天线端口数量和子周期帧头索引,所述子周期帧头索引用于表征所述子帧信号的子周期在NPBCH周期中的位置。

优选地,所述候选天线端口数量包括1和2,所述候选子周期帧头索引包括1、2、3、4、5、6、7和8。

优选地,根据所述候选子周期帧头索引确定所述第一比特序列的起始位置包括:

响应于所述候选子周期帧头索引为1或4或7,所述起始位置为1;

响应于所述候选子周期帧头索引为2或5或8,所述起始位置为65;以及

响应于所述候选子周期帧头索引为3或6,所述起始位置为129。

优选地,根据所述起始位置对所述第一比特序列进行解速率匹配以获取第二比特序列包括:

按照所述起始位置将所述第二比特序列中的数据按序添加到虚拟循环缓冲器中的多个数据位;

将所述虚拟循环缓冲器中的数据进行分流;以及

对分流后的数据进行子块解交织以获取所述第二比特序列。

优选地,响应于接收到NPBCH在一个子周期内发送的多个子帧信号,所述方法还包括:

将接收到的多个子帧信号进行合并。

第二方面,本发明实施例提供了一种信道盲检测装置,所述装置包括:

接收单元,用于接收窄带物理广播信道NPBCH在一个子周期内发送的至少一个子帧信号;

第一比特序列获取单元,用于获取所述子帧信号在候选天线端口数量和候选子周期帧头索引下对应的第一比特序列;

起始位置确定单元,用于根据所述候选子周期帧头索引确定所述第一比特序列的起始位置;

解速率匹配单元,用于根据所述起始位置对所述第一比特序列进行解速率匹配以获取第二比特序列;

解码单元,用于对所述第二比特序列进行解码处理以获取对应的第三比特序列;

检验单元,用于对所述第三比特序列进行校验以获取校验结果;以及

确定单元,用于将校验结果正确的第三比特序列对应的候选天线端口数量和候选子周期帧头索引确定为所述子帧信号对应的天线端口数量和子周期帧头索引,所述子周期帧头索引用于表征所述子帧信号的子周期在NPBCH周期中的位置。

第三方面,本发明实施例提供了一种通信装置,包括存储器和处理器,所述处理器执行所述存储器中的程序指令,用于实现第一方面所述的方法。

第四方面,本发明实施例提供了一种存储介质,所述存储介质用于存储计算机程序,所述计算机程序用于实现第一方面所述的方法。

本发明实施例通过接收窄带物理广播信道NPBCH在一个子周期内发送的子帧信号,获取所述子帧信号在候选天线端口数量和候选子周期帧头索引下对应的第一比特序列,根据所述候选子周期帧头索引确定所述第一比特序列的起始位置,根据所述起始位置对所述第一比特序列进行解速率匹配以获取第二比特序列,对所述第二比特序列进行解码、校验处理以获取校验结果,将校验结果正确的第三比特序列对应的候选天线端口数量和候选子周期帧头索引确定为所述子帧信号对应的天线端口数量和子周期帧头索引。由此,可以减小解速率匹配的缓存和计算量,提高盲检测效率。

附图说明

通过以下参照附图对本发明实施例的描述,本发明的上述以及其它目的、特征和优点将更为清楚,在附图中:

图1是本发明实施例的通信系统的示意图;

图2是本发明实施例的发送设备的NPBCH的数据处理的流程图;

图3是本发明实施例的天线端口数量与对应的扰码序列示意图;

图4是本发明实施例的虚拟循环缓冲器的结构示意图;

图5是本发明实施例的列间置换规则的示意图;

图6是本发明实施例的NPBCH在一个周期上的信道时频域的结构图;

图7是现有技术中的NPBCH盲检测方法的流程图;

图8是现有技术的候选序列的示意图;

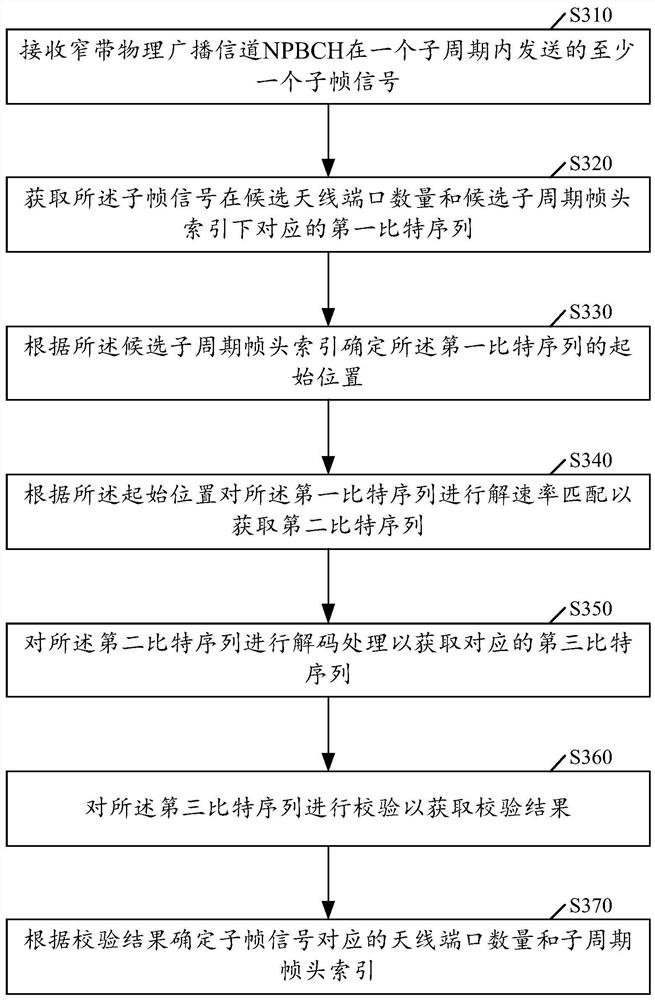

图9是本发明实施例的信道盲检测方法的流程图;

图10是本发明实施例的获取第一比特序列的流程图;

图11是本发明实施例的候选子周期帧头索引与起始位置对应关系的示意图;

图12是本发明实施例的获取第二比特序列的流程图;

图13是本发明实施例的信道盲检测装置的结构示意图;

图14是本发明实施例的通信装置的硬件结构示意图。

具体实施方式

以下基于实施例对本发明进行描述,但是本发明并不仅仅限于这些实施例。在下文对本发明的细节描述中,详尽描述了一些特定的细节部分。对本领域技术人员来说没有这些细节部分的描述也可以完全理解本发明。为了避免混淆本发明的实质,公知的方法、过程、流程、元件和电路并没有详细叙述。

此外,本领域普通技术人员应当理解,在此提供的附图都是为了说明的目的,并且附图不一定是按比例绘制的。

除非上下文明确要求,否则在说明书的“包括”、“包含”等类似词语应当解释为包含的含义而不是排他或穷举的含义;也就是说,是“包括但不限于”的含义。

在本发明的描述中,需要理解的是,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性。此外,在本发明的描述中,除非另有说明,“多个”的含义是两个或两个以上。

图1是本发明实施例的通信系统的示意图。如图1所示,本发明实施例的通信系统包括发送设备11和接收设备12。

在本实施例中,发送设备11为网络设备,接收设备12为终端设备。

进一步地,发送设备11包括编码器,从而发送设备11可以进行编码并输出编码后序列。编码后序列经过加扰、调制、层映射与预编码、RE映射和生成基带信号,传输至接收设备12。接收设备12包括译码器,接收设备12可以接收发送设备101发送的信号,对接收到的信号进行译码。

应理解,图1只是以示例的形式示意一种通信系统的架构图,并非对通信系统的架构图的限定。

在通信过程中,发送端对信息进行编码,得到待发送比特序列,并发送待发送比特序列。接收端对接收到的信号进行解调等处理,得到一组对数似然比(Likelihood Rate,LLR),该组LLR中包括的LLR的个数与待发送比特序列中包括的比特个数相同。接收端根据接收到的一组LLR进行译码。其中,不管发送端发比特1还是比特0,接收端都可能误判。对于信号r,在接收端正确判为0的概率p(r|b=0)与正确判为1的概率p(r|b=1)]的比值就是似然比。为了方便计算处理,对似然比取自然对数,则可以得到对数似然比,也即LLR=ln[p(r|b=0)/p(r|b=1)]。

进一步地,接收设备12包括但不限于移动台(MobileStation,MS)、移动终端(Mobile Terminal,MT)、移动电话(Mobile Telephone,MT)、手机(handset)及便携设备(portable equipment)等,该终端设备可以经无线接入网(RadioAccess Network,RAN)与一个或多个核心网进行通信。例如,终端设备可以是移动电话、具有无线通信功能的计算机等,终端设备还可以是便携式、袖珍式、手持式、计算机内置的或者车载的移动装置或设备。

进一步地,发送设备11可以是NB-IoT基站,或者,包含有NB-IoT的其他多种技术融合的网络的基站等。

进一步地,本发明实施例对NB-IoT网络下行信道的数据进行译码。

进一步地,本发明实施例对NB-IoT网络NPBCH的下行数据进行译码。

可选地,发送设备11的NPBCH的数据处理流程可参照图2,包括如下步骤:

步骤S110、信道编码。

在本实施例中,NPBCH的信道编码过程包括如下步骤:

步骤S111、CRC(Cyclic Redundancy Check,循环冗余校验)校验。

在本实施例中,CRC是一种根据网络数据包产生简短固定位数校验码的一种信道编码技术,主要用来检测或校验数据传输或者保存后可能出现的错误。

进一步地,MIB-NB信息为34bit的数据,校验时添加CRC序列长度为16bit,使得校验后的输出为50bit数据。

进一步地,添加校验比特后,CRC序列按照基站配置的天线端口数量,使用特定的天线端口数量扰码序列加绕,天线端口数量与对应的扰码序列如下图3所示。其中, 步骤S112、TBCC编码。 在本实施例中,TBCC(Tail Biting CC,咬尾卷积码)编码的编码原理:编码器开始工作时要进行特殊的初始化,将输入信息比特的最后m个比特依次输入编码器的寄存器中,当编码结束时,编码器的结束状态与初始状态相同。由于这个编码方法没有出现尾比特,因此称为咬尾编码。TBCC编码对控制信息和广播信道进行信道编码,增强鲁棒性,减少了尾比特的编码开销,克服了码率损失的问题,并且适合迭代译码。 进一步地,信息比特输入到TBCC编码模块后经过TBCC编码后,输出信息的比特数量为输入信息的比特数量的3倍。将输入比特表示为A 进一步地,k=50。 在本实施例中,咬尾卷积编码的编码速率为1/3。也即,TBCC编码器的输入信息为50bit,输出信息为3*50bit。 步骤S113、速率匹配。 在本实施例中,通过速率匹配将TBCC编码模块的输出信息转换为预定长度的数据。 进一步地,通过速率匹配将TBCC编码模块的输出的3*50bit的数据转换为1600bit的数据。具体地,速率匹配通过一个虚拟循环缓冲器实现,虚拟循环缓冲器的结构可参照图4,包括三个子块交织器41、42和43、比特收集单元44和比特选择单元45。 在本实施例中,将上述步骤S112通过编码得到的数据d 在本实施例中,子块交织器41的工作流程包括如下步骤: 步骤S1131、确定矩阵列数。 在本实施例中,确定矩阵列数C为32,各列的序号从左至右记为序号1,2,3,……,32。 步骤S1132、确定矩阵行数。 在本实施例中,子块交织器根据上述确定的矩阵列数获取矩阵行数。具体地,可根据如下公式获取: D≤(R*C) 其中,D为子块交织器的输入信息的比特数目,R为矩阵行数,C为矩阵列数。 进一步地,R为满足上述公式的最小整数。 进一步地,可以确定D=k=50,C=32,由此可计算得到,R=2。 进一步地,将矩阵的各行从左上到下记为序号1,2。 由此,可以得到一个2*32的矩阵。 步骤S1133、将输入信息添加到矩阵中。 在本实施例中,2*32的矩阵共有64个数据位,而输入比特数量为50,由此,需要在头部添加14个虚比特,之后将输入信息的比特数量添加到矩阵的其它位置。 具体地,从矩阵的第0行第0列开始逐行添加,首先添加14个虚比特,之后将输入信息的50bit数据依次添加到矩阵中。 步骤S1134、列间置换。 在本实施例中,按照预定的规则对上述得到的矩阵进行列间置换。具体地,置换规则如图5所示。将置换后矩阵的各列从左到右依次记为P 由此,子块交织器41可以得到一个2*32的第一置换矩阵。 进一步地,子块交织器42和43根据上述同样步骤可以得到一个2*32的第二置换矩阵和第三置换矩阵。 在本实施例中,比特收集单元44根据上述的第一置换矩阵、第二置换矩阵和第三置换矩阵进行数据收集。 具体地,按照从左到右的顺序逐列从第一置换矩阵读出比特序列,记为v

也即,将从第一置换矩阵读出的m个比特序列按序分别添加到虚拟循环缓冲器的第1个至第m个位置,将从第二置换矩阵读出的m个比特序列按序分别添加到虚拟循环缓冲器的第m+1个至第2*m个位置,将从第三置换矩阵读出的m个比特序列按序分别添加到虚拟循环缓冲器的第2*m+1个至第3*m个位置。 进一步地,由于m=64,由此,虚拟循环缓冲器共有3*m=192bit的数据。 在本实施例中,比特选择单元45用于生成预定长度n的比特序列e。 进一步地,比特选择单元45用于生成n=1600bit的序列。 进一步地,NPBCH的发送周期长度为640ms,分为8个80ms的子周期,子周期内NPBCH以重复空口信号形式发送,因此每个子周期内承载的NPBCH信息bit为100个RE在QPSK调制条件下承载的信息量,即200bit,8个子周期共计1600bit。因此要求速率匹配输出序列长度为1600bit。 具体地,比特选择单元45从虚拟循环缓冲器中按照预定顺序选择一个数据,判断该数据是否为虚比特,如果不是虚比特,则将该数据添加到1600bit中,如果是虚比特,则跳过该数据选择下一个数据继续处理直到填满1600bit。 进一步地,根据上述原理可知虚拟循环缓冲器中共有3*64bit的数据,每个64bit的数据中包括50bit的有效数据,因此,每填满一个200bit(4*50bit),共需要读取虚拟循环缓冲器中4*64bit的数据。由此可知,在虚拟循环缓冲器中的192bit的数据中: 第一个200bit,起始位置k0为1; 第二个200bit,起始位置k0为65; 第三个200bit,起始位置k0为129; 第四个200bit,起始位置k0为1; 第五个200bit,起始位置k0为65; 第六个200bit,起始位置k0为129; 第七个200bit,起始位置k0为1; 第八个200bit,起始位置k0为65。 也即,第1、4、7个200bit的数据的起始位置为1,第2、5、8个200bit的数据的起始位置为65,第3、6个200bit的数据的起始位置为129。 由此,通过速率匹配可以生成1600bit的数据e 步骤S120、加扰。 在本实施例中,加扰是通过一个随机码序列对扩频码进行相乘,对信号进行加密,下行链路加扰可以用于区分小区和信道。 进一步地,加扰公式如下:

其中, 具体地,由于e(h)和c(h)为0或1,因此,加扰实际上是根据随机序列中的c(h)确定 当e(h)=0,c(h)=0时, 当e(h)=0,c(h)=1时, 当e(h)=1,c(h)=0时, 当e(h)=1,c(h)=1时, 步骤S130、QPSK调制。 在本实施例中,NPDSCH采用QPSK(Quadrature Phase Shift Keying,四相移位键控)调制方式。QPSK是利用载波的四种不同相位差来表征输入的数字信息,是四进制移相键控。QPSK是在M=4时的调相技术,它规定了四种载波相位,分别为45°,135°,225°,315°,调制器输入的数据是二进制数字序列,为了能和四进制的载波相位配合起来,则需要把二进制数据变换为四进制数据。 具体地,将上述通过加扰得到的1600bit数据分为8个200bit。对于每一个200bit,把二进制数字序列中每两个比特分成一组,共有四种组合,即00,01,10,11,其中每一组称为双比特码元。每一个双比特码元是由两位二进制信息比特组成,它们分别代表四进制四个符号中的一个符号(symbol)。QPSK中每次调制可传输2个信息比特,这些信息比特是通过载波的四种相位来传递的。解调器根据接收到的载波信号的相位来判断发送端发送的信息比特。 步骤S140、层映射与预编码。 在本实施例中,由于码字数量与发送天线端口的数量不同,需要将码字映射到不同的天线端口上。层数是通过RI(Rank Indication,RANK指示),RANK为MIMO(multipleinput multiple output,多入多出)方案中天线矩阵中的秩,即能够独立并行传输的数据流。RANK由终端告诉网络侧能够有效支持的层数。如果接收端最多支持两天线端口,那么秩的最大值只能为2。NPBCH由层映射和预编码共同完成了MIMO的功能。其过程是首先通过层映射把要传输的码字复值调制符号映射到一个或者多个层中,完成串并转换并且控制空间复用的复用率,然后对层映射后的数据进行预编码,也就是实现了MIMO的编码。其中,预编码用于将层数据匹配到天线端口上,同时降低或者控制空间复用数据流之间的干扰,降低接收机实现的复杂度,减少系统开销,从而提升MIMO技术的性能。 步骤S150、RE映射。 在本实施例中,RE(Resource Element,资源元素)映射将预编码的输出,经过随机相位偏移处理,再映射到分配的RB(Resource Block,资源块)资源上去,映射过程遵从先频域再时域的原则,即先填满一个OFDM(Orthogonal Frequency Division Multiplexing,正交频分复用)symbol(符号)的所有RE,在填下一个OFDM symbol。 步骤S160、基带信号生成。 在本实施例中,基带信号为信源(发射端)发出的的原始电信号。具体地,基带信号的生成方法可以采用现有的各种技术,在此不再赘述。由此,即可生成发送信号。 具体地,NPBCH在一个周期上的信道时频域的结构图可参照图6。如图6所示,NPBCH的一个周期为640ms,分为8个子周期,每个子周期80ms。每个子周期发送一段200bit的数据,因此,1600bit的数据通过8个周期正好发送完毕。同时,每个子周期分为8个10ms,每个10ms的第1ms内发送MIB-NB信号,因此,每个子周期内会将每段200bit的数据重复发送8次。 应理解,上述NPBCH的信号处理仅为本发明实施例的一种实现方式,本发明实施例对此不作限定,可以通过现有的各种方式实现。 进一步地,接收设备12为了获取MIB-NB信息,需要对该MIB-NB信息进行盲检测,即在计算得到的搜索空间上搜索该MIB-NB信息所在的位置,对该位置的MIB-NB信息进行译码。 图7是现有技术中的NPBCH盲检测方法的流程图。如图7所示,现有技术的NPBCH盲检测方法包括如下步骤: 步骤S210、获取软比特LLR。 在本实施例中,接收设备通过小区搜索可以获得接收信号在时域上80ms的帧头,即在一个640ms周期中的某一80ms起始位置。获取接收到的子帧信号的软比特LLR。 具体地,以预定速率进行采样,去除循环前缀,提取第一个子帧上的基带数据,获取时域上完整的MIB-NB数据及相关导频数据;进行傅里叶变换,生成该子帧的频域数据;对天线端口的数量进行盲检,天线端口数量为1,则对应端口号p=2000,天线端口数量为2,则对应端口号p=2000和p=2001;计算天线端口号对应的NRS映射位置,提取NRS(Narrow-band reference signal,窄带参考信号),利用本地生成的NRS序列与接收数据中的NRS信号做信道估计,恢复发送端信号;进行解资源映射,剔除参考信号LTE-CRS(Cell-SpecificReference Signal,小区特定参考信号)和NRS占用的资源格,从资源格的位置依次取出复值符号;根据天线端口数量进行解层映射和预编码;解QPSK调制,将每个复值符号解调为两个比特数据;由此,即可得到子帧信号在天线端口数量为1和2时分别对应的200bit的软比特LLR。 进一步地,如果接收到同一子周期内的多个子帧信号,获取每个子帧信号对应的200bit的软比特LLR,并将每个子帧信号对应的200bit的软比特LLR进行合并。软比特LLR的合并方法可以采用现有的各种合并方法,本发明实施例对此不作限制。例如,合并方法可以是等比例合并,饱和加等。 步骤S220、解扰。 在本实施例中,获取发送设备加扰时各个子周期的随机序列,根据所述随机序列对上述得到的200bit的数据进行解扰。 进一步地,根据上述步骤S120可知,发送设备在进行加扰时会通过一个随机序列,发送的每一比特数据对应随机序列中的一个数据,由此,每200bit的发送数据对应一个200bit的随机序列,根据加扰时的随机序列对接收到的数据进行解扰以恢复发送设备在加扰前的数据。 进一步地,根据上述步骤S210可以得到子帧信号在天线端口数量为1和2时分别对应的200bit的软比特LLR。获取发送设备在加扰时各个子周期的随机序列,根据各个子周期的随机序列对得到的200bit的软比特LLR分别进行解扰,以获取天线端口数量为1时8个子周期分别对应的解扰序列,和天线端口数量为2时8个子周期分别对应的解扰序列。也即,根据天线端口数量和子周期的不同通过解扰后得到16个200bit的数据。 步骤S230、解速率匹配。 在本实施例中,解速率匹配为上述步骤S113的逆过程,具体包括如下步骤: 步骤S231、确定候选序列。 在本实施例中,在解速率匹配时,确定需要进行解速率匹配的候选序列。 具体地,通过解扰得到16个200bit数据,根据每一个200bit数据对应的天线端口数量和子周期确定对应的候选序列。将上述得到的200bit的数据放入该子周期内,其它子周期内的数据填0,由此,可以得到一个1600bit的数据,由此,在天线端口数量为1时,共有8种情况,对应得到8个1600bit的数据。同理,在天线端口数量为2时,也有8种情况,对应也得到8个1600bit的数据。 图8示出了一种天线端口数量的候选序列,其中,X为子周期帧头索引。具体地,X=i(i=1,2,3,4,5,6,7,8)时,将上述得到的200bit的数据第i个子周期内,其它子周期内的数据填0。 应理解,图8仅示出了一种天线端口数量的候选序列,由于,天线端口数量可能有两种情况,因此,共有16种候选序列,每个候选序列为1600bit。 步骤S232、解速率匹配。 在本实施例中,接收设备通过控制信息获取发送设备发送的原始序列的长度D,该原始序列为通过CRC校验后得到的序列,也即D=50bit。进而根据原始序列长度构件虚拟循环缓冲器,具体可参照上述图4和图5,包括如下步骤: 步骤S2321、确定矩阵列数。 在本实施例中,确定矩阵列数C为32,各列的序号从左至右记为序号1,2,3,……,32。 步骤S2322、确定矩阵行数。 在本实施例中,子块交织器根据上述确定的矩阵列数获取矩阵行数。具体地,可根据如下公式获取: D≤(R*C) 其中,D为子块交织器的输入信息的比特数目,R为矩阵行数,C为矩阵列数。 进一步地,R为满足上述公式的最小整数。 进一步地,可以确定D=50,C=32,由此可计算得到,R=2。 进一步地,将矩阵的各行从左上到下记为序号1,2。 由此,可以得到一个2*32的矩阵。 步骤S2323、将信息添加到矩阵中。 在本实施例中,2*32的矩阵共有64个数据位,而原始序列的比特数量为50,由此,需要在头部添加14个虚比特,之后将有效信息添加到矩阵的其它位置。 具体地,从矩阵的第0行第0列开始逐行添加,首先添加14个虚比特,之后将50bit数据依次添加到矩阵中。 步骤S2324、列间置换。 在本实施例中,按照预定的规则对上述得到的矩阵进行列间置换。具体地,置换规则如图5所示。将置换后矩阵的各列从左到右依次记为P 由此,子块交织器41可以得到一个32*2的第一置换矩阵。 进一步地,子块交织器42和43根据上述同样步骤可以得到一个32*2的第二置换矩阵和第三置换矩阵。 在本实施例中,比特收集单元44根据上述的第一置换矩阵、第二置换矩阵和第三置换矩阵进行数据收集。 具体地,按照从左到右的顺序逐列从第一置换矩阵读出比特序列,记为v

也即,将从第一置换矩阵读出的m个比特序列按序分别添加到虚拟循环缓冲器的第1个至第m个位置,将从第二置换矩阵读出的m个比特序列按序分别添加到虚拟循环缓冲器的第m+1个至第2*m个位置,将从第三置换矩阵读出的m个比特序列按序分别添加到虚拟循环缓冲器的第2*m+1个至第3*m个位置。 进一步地,由于m=64,由此,虚拟循环缓冲器共有3*m=192bit的数据。 由此,即可得到虚拟循环缓冲器。 步骤S2325、将候选序列添加到虚拟循环缓冲器。 在本实施例中,将上述得到的候选序列添加到虚拟循环缓冲器。 进一步地,对于每一个候选序列,将1600bit数据添加到虚拟循环缓冲器中的192个数据位。 具体地,根据上述构建虚拟循环缓冲器的步骤可以得知192个数据位中有150个有效位和42个虚拟比特位置。首先,选择候选序列中的第一个比特,选择虚拟循环缓冲器中的第一个数据位,判断该数据位是否为有效位,如果该数据位是有效位,则将选择比特填到该数据位,如果该数据位不是有效位,选择虚拟循环缓冲器中的下一个数据位,继续判断。如果,当前处理的数据位是192bit中的最后一个数据位,在下一次处理时,返回第一个数据位。重复上述步骤,直至将1600比特数据全部添加到192个数据位。 进一步地,对于每一个数据位,都接收到了多个比特的数据,将多个比特的数据进行合并。由此,可以得到192bit的数据。 步骤S2326、比特分流。 在本实施例中,将上述得到的192bit的数据进行比特分流以获取3*64bit数据。 具体地,将192bit的数据中的1-64比特数据取出生成一个64bit的序列,记为v 步骤S2327、子块解交织。 在本实施例中,对于上述得到的每一个64bit的数据,添加到2*32的矩阵。通过上述步骤S2324的过程以及步骤S2323的逆过程即可得到3*50bit的数据。 进一步地,通过上述同样的方法可以获取16种候选序列的3*50bit数据。 步骤S240、解编码。 在本实施例中,将上述得到的16种3*50bit的数据分别进行解TBCC编码以获取16个50bit的数据。 进一步地,解TBCC编码可采用现有的各种方法,在此不作限制。 步骤S250、解CRC。 在本实施例中,通过对上述16个50bit的数据分别进行解CRC以获取16个校验结果。 进一步地,获取校验结果正确的情况对应的天线端口数量和子周期帧头索引作为译码结果。 但是,现有技术在解速率匹配时缓存和计算量比较大,如上所述,在解速率匹配之前需要占用的缓存为16*1600bit,计算量为16*1600bit。 进一步地,根据发送设备的及速率匹配过程可知:第1、4、7个200bit的数据的起始位k0置为1,第2、5、8个200bit的数据的起始位置k0为65,第3、6个200bit的数据的起始位置k0为129。由此,本发明实施例提供一种信道盲检测方法,以减小解速率匹配的缓存和计算量,提高盲检测效率。具体如图9所示,包括如下步骤: 步骤S310、接收窄带物理广播信道NPBCH在一个子周期内发送的至少一个子帧信号。 在本实施例中,接收设备通过小区搜索可以获得接收信号在时域上80ms的帧头,即在一个640ms周期中的某一80ms起始位置。接收窄带物理广播信道NPBCH在一个子周期内发送的至少一个子帧信号。 进一步地,如果接收到同一子周期内的多个子帧信号,将每个子帧信号进行合并。合并方法可以采用现有的各种合并方法,本发明实施例对此不作限制。例如,合并方法可以是等比例合并,饱和加等。 步骤S320、获取所述子帧信号在候选天线端口数量和候选子周期帧头索引下对应的第一比特序列。 在本实施例中,获取接收到的子帧信号的软比特LLR,具体如图10所示,包括如下步骤: 步骤S321、提取采样后的NPBCH基带数据,进行傅里叶变换得到频域数据。 在本实施例中,以预定频率进行采样,去除循环前缀,提取第一个子帧上的基带数据,获取时域上完整的MIB-NB数据及相关导频数据。进行傅里叶变换,生成该子帧的频域数据。 步骤S322、通过NRS进行信道估计,恢复发送端信号。 在本实施例中,对天线端口的数量进行盲检,天线端口数量为1,则对应端口号p=2000,天线端口数量为2,则对应端口号p=2000和p=2001,计算天线端口号对应的NRS(Narrow-band reference signal,窄带参考信号)映射位置,提取NRS信号,利用本地生成的NRS序列与接收数据中的NRS信号做信道估计;进行最小均方误差估计,用得到的估计矩阵来恢复发送端信号。 步骤S323、进行解资源映射。 在本实施例中,剔除参考信号LTE-CRS Cell-Specific Reference Signal,小区特定参考信号)和NRS占用的资源格,并且去掉前三个OFDM(Orthogonal FrequencyDivision Multiplexing,正交频分复用技术)符号和参考信号占用的资源格,其中计算参考信号的位置时,假设CRS的天线端口p=0-3都存在,假设NB-IoT的天线端口号p=2000和p=2001都存在,按照预定顺序从第4个符号开始依次取出复值符号。 进一步地,MIB-NB信息在NPBCH信道传输,NPBCH信道数据传输周期为8个子周期,共64帧。因此需要对该帧位于NPBCH周期哪一个子周期进行盲检,令子周期帧头索引X依次取值1到8,再除以假设的子周期内的8个10ms帧头索引对应的系数θf(i),得到100个复值符号。 其中,θf(i)为发送设备在进行RE映射前加入的随机相位偏移。具体地,发送设备在进行RE映射前,对每个子周期内的8个10ms帧头索引对应子帧0的所有参与RE映射的100个symbol进行随机相位偏移处理,更具体地,是将symbol乘以随机相位偏移θf(i)。 其中,θf(i)的计算公式如下:

其中,cf(2i)和cf(2i+1)为随机序列,θf(i)为随机相位偏移。 也即,当cf(2i)=0,cf(2i+1)=0时,θf(i)=1; 当cf(2i)=0,cf(2i+1)=1时,θf(i)=-1; 当cf(2i)=1,cf(2i+1)=0时,θf(i)=j; 当cf(2i)=1,cf(2i+1)=1时,θf(i)=-j。 步骤S324、解层映射和预编码。 在本实施例中,NPBCH最多使用2个天线端口。当采用1个天线端口时,使用天线端口号p=2000,可以看作信号直接传输。当采用2个天线端口时,使用天线端口号p=2000和p=2001,采用传输分集方式。 步骤S325、解QPSK调制。 在本实施例中,将每两个复值符号调节为一对比特数据。由此,可以得到200bit数据。 由此,通过上述步骤S321-S325即可得到子帧信号在候选天线端口数量和候选子周期帧头索引下的200bit数据。 进一步地,由于候选天线端口数量为有两种,候选子周期帧头索引有8种,因此,共得到16个200bit数据。 步骤S326、解扰码。 在本实施例中,对于上述得到的每一个200bit数据,接收设备产生1600bit(8*200bit)的随机序列,根据步骤S323假设的该子帧信号位于NPBCH周期中的第几个子周期,选取其中的第几个200bit进行解扰。 在本实施例中,发送设备在进行加扰时会通过一个随机序列,发送的每一比特数据对应随机序列中的一个数据,每一个子周期对应一个扰码序列,由此,可以根据加扰时的随机序列对接收到的数据进行解扰以恢复发送设备在加扰前的数据。 进一步地,对于候选子周期帧头索引X=i(i=1,2,3,4,5,6,7,8)的映射,根据第i个子周期的随机序列进行解扰以获取对应的第一比特序列。 具体地,解扰公式如下: y=LLR*(1-2c) 其中,LLR为解调制得到的比特序列,c为随机序列,y为解扰后的序列。 由上述公式可知,当c=0时,y=LLR;当c=1时,y=-LLR。 也即,如果随机序列为0,则不改变解调制得到的比特序列;如果扰码序列为1,则将解调制得到的比特序列进行0/1变换。 由此,即可得到在候选天线端口数量和候选子周期帧头索引下对应的第一比特序列。 步骤S330、根据所述候选子周期帧头索引确定所述第一比特序列在虚拟循环缓冲器中的起始位置(下称起始位置k0)。 在本实施例中,根据发送设备速率匹配过程可知,第1、4、7个200bit的数据在虚拟循环缓冲器中的起始位置k0为1,第2、5、8个200bit的数据在虚拟循环缓冲器中的起始位置k0为65,第3、6个200bit的数据在虚拟循环缓冲器中的起始位置k0为129。由此,可以根据候选子周期帧头索引X确定第一比特序列在虚拟循环缓冲器中的起始位置。 进一步地,候选子周期帧头索引X与第一比特序列在虚拟循环缓冲器中的起始位置k0的关系如图11所示。根据所述候选子周期帧头索引确定所述第一比特序列在虚拟循环缓冲器中的起始位置包括: 响应于所述候选子周期帧头索引为1或4或7,所述起始位置为1。 响应于所述候选子周期帧头索引为2或5或8,所述起始位置为65。 响应于所述候选子周期帧头索引为3或6,所述起始位置为129。 步骤S340、根据所述起始位置对所述第一比特序列进行解速率匹配以获取第二比特序列。 在本实施例中,对于每一个200bit,根据上述确定的起始位置进行解速率匹配以获取第二比特序列。具体如图12所示,包括如下步骤: 步骤S341、按照所述起始位置将所述第二比特序列中的数据按序添加到虚拟循环缓冲器中的多个数据位。 在本实施例中,发送设备获取虚拟循环缓冲器,将所述第二比特序列中的数据按序添加到虚拟循环缓冲器中的多个数据位。具体地,获取虚拟缓冲器的步骤可参照上述步骤S232,在此不再赘述。 进一步地,确定的起始位置为k0,将上述得到的第二比特序列(200bit)从虚拟循环缓冲器中192个数据位的第k0个数据位开始填入。 具体地,选择第二比特序列中的第一个比特,选择虚拟循环缓冲器中的第k0(k0=1,65,129)个数据位,判断该数据位是否为有效位,如果该数据位是有效位,则将选择比特填到该数据位,如果该数据位不是有效位,选择虚拟循环缓冲器中的下一个数据位,继续判断。如果当前处理的数据位是192中的最后一个数据位,在下一次处理时,返回第一个数据位。重复上述步骤,直至将200bit比特数据全部添加到192个数据位。 进一步地,对于每一个数据位,如果接收到了多个比特的数据,将多个比特的数据进行合并。由此,可以得到192bit的数据。 步骤S342、将所述虚拟循环缓冲器中的数据进行分流。 在本实施例中,将上述得到的192bit的数据进行比特分流以获取3*64bit数据。 具体地,将192bit的数据中的1-64比特数据取出生成一个64bit的序列,记为v11,v12,v13,……,v1m,其中,m=64。将65-128比特数据取出生成一个64bit的序列,记为v21,v22,v23,……,v2m,其中,m=64。将129-192比特数据取出生成一个64bit的序列,记为v31,v32,v33,……,v3m,其中,m=64。由此,可以得到3*64bit数据。 步骤S343、对分流后的数据进行子块解交织以获取所述第二比特序列。 在本实施例中,通过子块解交织根据上述得到的3*64bit数据获取对应的第二比特序列。 进一步地,对于上述得到的每一个64bit数据,按照从左到右的顺序逐列添加到2*32的矩阵中。通过上述步骤S1134逆过程进行列间反置换得到原始矩阵,将原始矩阵中的数据从矩阵的第0行第0列开始逐行读出,去除前14个虚比特,可生成50bit的数据。由此,对于3*64bit的数据,通过子块解交织得到的第二比特序列为3*50bit。 进一步地,对于上述步骤S330解扰后得到的16种200bit,通过解速率匹配后得到16个3*50bit。 本发明实施例通过将解扰后的数据直接进行解速率匹配,解速率匹配的缓存为16*3*50bit,相比现有技术在解速率匹配之前缓存的16*1600bit数据,占用的缓存为现有技术的9/32。 步骤S350、对所述第二比特序列进行解码处理以获取对应的第三比特序列。 在本实施例中,对上述得到的16个3*50bit分别进行解码处理以获取对应的第三比特序列。 进一步地,对每一个3*50bit的数据通过解码算法得到约束长度为7,码率1/3的咬尾卷积编码前的50bit数据,也即第三比特序列。解码思想是找到基于接收序列的最大似然译码。对状态寄存器、状态转移寄存器、路径寄存器进行初始化,针对初始状态后的每一个状态进行循环,计算该状态与之前的两个可能状态的汉明距离,比较选出汉明距离更小一条路径,直到找出一条概率值最大的路径,最后对此路径转移进行回溯,生成解码数据。 步骤S360、对所述第三比特序列进行校验以获取校验结果。 在本实施例中,对上述得到的16个第三比特序列分别进行校验以获取校验结果。 进一步地,第三比特序列的50bit数据中含34bit的MIB-NB数据和16bit的CRC校验数据,并且16位校验bit被不同扰码序列加扰。首先根据之前假定的天线端口的数量,选择不同的扰码,对CRC校验bit进行去扰码操作。具体地,对于假设的天线端口的数量为1的8种情况,选择图3中全0的扰码序列进行解扰码处理;对于假设的天线端口的数量为2的8种情况,选择图3中全1的扰码序列进行解扰码处理。然后用解扰后的16位CRC数据来判断数据是否解码正确。 步骤S370、根据校验结果确定所述子帧信号对应的天线端口数量和子周期帧头索引。 在本实施例中,将校验结果正确的第三比特序列对应的候选天线端口数量和候选子周期帧头索引确定为所述子帧信号对应的天线端口数量和子周期帧头索引,所述子周期帧头索引用于表征所述子帧信号的子周期在NPBCH周期中的位置。 由此,即可确定接收到的子帧信号是第几个80ms的帧头。 进一步地,由校验结果正确的第三比特序列解CRC得到发送设备发送的MIB-NB信息(34bits)。 进一步地,有上述步骤可知,本发明实施例对接收到的200bit数据直接进行解速率匹配,只需要缓存解速率匹配输出的16*3*150bit数据,计算量为16*200bit。相比现有技术需要的缓存16*1600bit,计算量16*1600bit,本发明实施例需要的缓存为现有技术的9/32,计算量为现有技术的1/8。 图13是本发明实施例的信道盲检测装置的结构示意图。如图13所示,本发明实施例的信道盲检测装置包括:接收单元131、第一比特序列获取单元132、起始位置确定单元133、解速率匹配单元134、解码单元135、检验单元136和确定单元137。其中,接收单元131用于接收窄带物理广播信道NPBCH在一个子周期内发送的至少一个子帧信号。第一比特序列获取单元132用于获取所述子帧信号在候选天线端口数量和候选子周期帧头索引下对应的第一比特序列。起始位置确定单元133用于根据所述候选子周期帧头索引确定所述第一比特序列的起始位置。解速率匹配单元134用于根据所述起始位置对所述第一比特序列进行解速率匹配以获取第二比特序列。解码单元135用于对所述第二比特序列进行解码处理以获取对应的第三比特序列。检验单元136用于对所述第三比特序列进行校验以获取校验结果。确定单元137用于将校验结果正确的第三比特序列对应的候选天线端口数量和候选子周期帧头索引确定为所述子帧信号对应的天线端口数量和子周期帧头索引,所述子周期帧头索引用于表征所述子帧信号的子周期在NPBCH周期中的位置。 进一步地,所述候选天线端口数量包括1和2,所述候选子周期帧头索引包括1、2、3、4、5、6、7和8。 进一步地,所述起始位置确定单元133包括: 第一位置确定子单元,用于响应于所述候选子周期帧头索引为1或4或7,所述起始位置为1; 第二位置确定子单元,用于响应于所述候选子周期帧头索引为2或5或8,所述起始位置为65;以及 第三位置确定子单元,用于响应于所述候选子周期帧头索引为3或6,所述起始位置为129。 进一步地,所述解速率匹配单元134包括: 数据添加子单元,用于按照所述起始位置将所述第二比特序列中的数据按序添加到虚拟循环缓冲器中的多个数据位; 分流子单元,用于将所述虚拟循环缓冲器中的数据进行分流;以及 解交织子单元,用于对分流后的数据进行子块解交织以获取所述第二比特序列。 进一步地,响应于接收到NPBCH在一个子周期内发送的多个子帧信号,所述装置还包括: 合并单元,用于将接收到的多个子帧信号进行合并。 通过接收窄带物理广播信道NPBCH在一个子周期内发送的子帧信号,获取所述子帧信号在候选天线端口数量和候选子周期帧头索引下对应的第一比特序列,根据所述候选子周期帧头索引确定所述第一比特序列的起始位置,根据所述起始位置对所述第一比特序列进行解速率匹配以获取第二比特序列,对所述第二比特序列进行解码、校验处理以获取校验结果,将校验结果正确的第三比特序列对应的候选天线端口数量和候选子周期帧头索引确定为所述子帧信号对应的天线端口数量和子周期帧头索引。由此,可以减小解速率匹配的缓存和计算量,提高盲检测效率。 图14为本发明实施例的通信装置的硬件结构示意图。如图14所示,该通信装置包括:存储器141和处理器142,其中,存储器141和处理器142通信;示例性的,存储器141和处理器142通过通信总线143通信,所述存储器141用于存储计算机程序,所述处理器142执行所述计算机程序实现上述实施例所示的方法。 可选地,通信装置还可以包括发送器和/或接收器。 可选地,上述处理器可以是中央处理单元(Central Processing Unit,CPU),还可以是其他通用处理器、PLC(Programmable Logic Controller,可编程逻辑控制器)、FPGA(Field-Programmable Gate Array,现场可编程门阵列)、DSP(Digital SignalProcessor,数字信号处理器)或ASIC(Application Specific Integrated Circuit,专用集成电路)来实现。通用处理器可以是微处理器或者该处理器也可以是任何常规的处理器等。结合本发明所公开的方法的步骤可以直接体现为硬件处理器执行完成,或者用处理器中的硬件及软件模块组合执行完成。 本发明实施例提供一种存储介质,所述存储介质用于存储计算机程序,所述计算机程序用于实现上述任意方法实施例所述的信道盲检测方法。 本发明实施例提供一种芯片,该芯片用于支持接收设备(例如终端设备、网络设备等)实现本发明实施例所示的功能,该芯片具体用于芯片系统,该芯片系统可以由芯片构成,也可以包括芯片和其他分立器件。当实现上述方法的为接收设备内的芯片时,芯片包括处理单元,进一步的,芯片还可以包括通信单元,所述处理单元例如可以是处理器,当芯片包括通信单元时,所述通信单元例如可以是输入/输出接口、管脚或电路等。处理单元执行本发明实施例中各个处理模块所执行的全部或部分动作,通信单元可执行相应的接收或发送动作。在另一个具体的实施例中,本发明实施例中的接收设备的处理模块可以是芯片的处理单元,控制设备的接收模块或发送模块是芯片的通信单元。 实现上述各方法实施例的全部或部分步骤可以通过程序指令相关的硬件来完成。前述的程序可以存储于一可读取存储器中。该程序在执行时,执行包括上述各方法实施例的步骤;而前述的存储器(存储介质)包括:只读存储器(英文:read-only memory,缩写:ROM)、RAM、快闪存储器、硬盘、固态硬盘、磁带(英文:magnetic tape)、软盘(英文:floppydisk)、光盘(英文:optical disc)及其任意组合。 本发明实施例是参照根据本发明实施例的方法、装置和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理单元以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理单元执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。 这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。 这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。 显然,本领域的技术人员可以对本发明实施例进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明实施例的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。 以上所述仅为本发明的优选实施例,并不用于限制本发明,对于本领域技术人员而言,本发明可以有各种改动和变化。凡在本发明的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 信道盲检测方法和装置以及通信装置和存储介质

- 一种控制信道的检测方法、装置、通信设备和存储介质