包括穿通电极的半导体器件

文献发布时间:2023-06-19 09:30:39

相关申请的交叉引用

本申请要求于2019年7月9日提交的申请号为10-2019-0082903的韩国专利申请的优先权,其全部内容通过引用合并于此。

技术领域

本公开的实施例涉及半导体器件和穿通电极。

背景技术

近来,已经开发了三维半导体器件以增加其集成密度。每个三维半导体器件可以通过垂直层叠多个半导体芯片以在有限的面积上实现最大的集成密度。

每个三维半导体芯片可以利用穿通硅通孔(TSV)技术来实现,该技术是利用垂直贯穿半导体芯片的硅通孔来将垂直层叠的所有半导体芯片彼此电连接。因此,与使用接合线制造的三维半导体器件相比,使用TSV制造的三维半导体器件可以有效地减小其封装面积。

另外,半导体器件或包括半导体器件的半导体封装体可以在该半导体封装体被提供给用户或顾客之前进行测试,以验证其特性和可靠性。因此,已经提出了测试半导体器件或半导体封装体的各种方法,以减少测试时间并提高测试效率。

发明内容

根据一个实施例,一种半导体器件可以包括:第一半导体芯片;以及第二半导体芯片,其层叠在第一半导体芯片上,并且通过第一穿通电极和第二穿通电极而电连接至第一半导体芯片。在第二测试操作期间,第一半导体芯片可以将第一穿通电极电连接至第三测试电阻器。在第二测试操作期间,第一半导体芯片可以检测第一内部节点的电压电平,以测试第一穿通电极与第二穿通电极之间的短路故障,所述第一内部节点的电压电平由第三测试电阻器以及第一穿通电极和第二穿通电极的电阻值来确定。

根据一个实施例,一种半导体器件可以包括:第一半导体芯片;以及第二半导体芯片,其层叠在第一半导体芯片上。第二半导体芯片可以通过第一穿通电极和第二穿通电极而电连接至第一半导体芯片。在第一测试操作期间,第一半导体芯片可以将第一穿通电极和第二穿通电极电连接至第一测试电阻器和第二测试电阻器。在第一测试操作期间,第一半导体芯片可以检测第一内部节点和第二内部节点的电压电平,以测试第一穿通电极和第二穿通电极的开路故障。第一内部节点和第二内部节点的电压电平可以由第一测试电阻器和第二测试电阻器以及第一穿通电极和第二穿通电极的电阻值确定。

根据另一个实施例,一种半导体器件可以包括:第一半导体芯片;以及第二半导体芯片,其层叠在第一半导体芯片上。第二半导体芯片可以通过第一穿通电极和第二穿通电极而电连接至第一半导体芯片。在第一测试操作期间,第一半导体芯片可以被配置为将第一穿通电极和第二穿通电极电连接至第一测试电阻器和第二测试电阻器,以及被配置为检测第一内部节点和第二内部节点的电压电平,以测试第一穿通电极和第二穿通电极的开路故障。在这种情况下,第一内部节点和第二内部节点的电压电平可以由第一测试电阻器和第二测试电阻器以及第一穿通电极和第二穿通电极的电阻值来确定。在第二测试操作期间,第一半导体芯片可以被配置为将第一穿通电极电连接至第三测试电阻器,以及被配置为检测第一内部节点的电压电平,以测试第一穿通电极与第二穿通电极之间的短路故障。在这种情况下,第一内部节点的电压电平可以由第三测试电阻器以及第一穿通电极和第二穿通电极的电阻值来确定。

附图说明

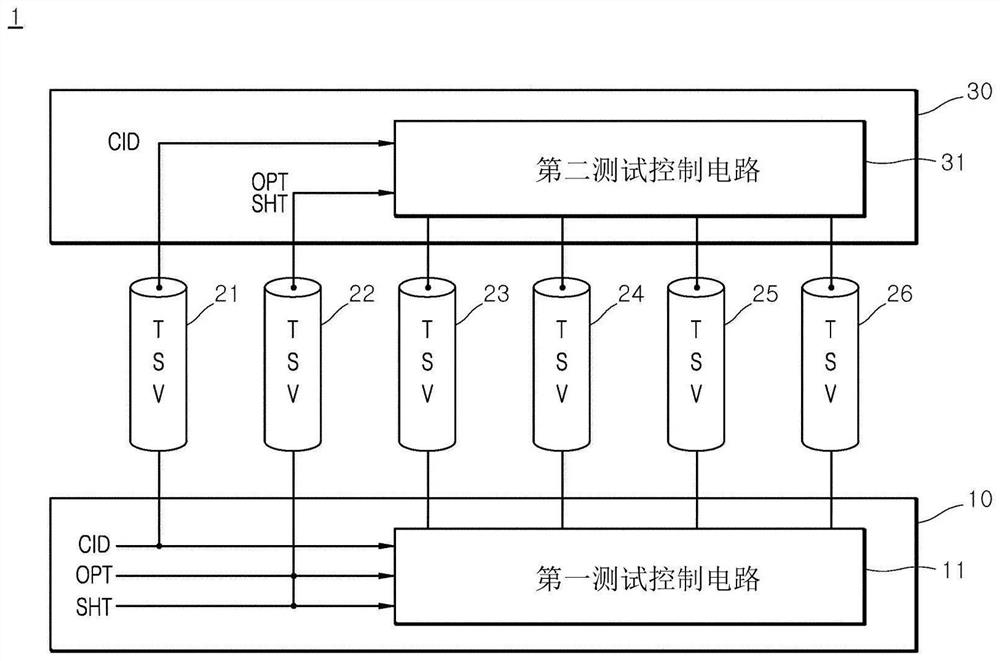

图1是示出根据本公开的实施例的半导体器件的配置的框图。

图2是示出图1的半导体器件中所包括的第一测试控制电路的配置的框图。

图3示出图2的第一测试控制电路中所包括的第一控制电路的配置。

图4示出图2的第一测试控制电路中所包括的第一测试电路的配置,连同图1所示的第一穿通电极一起。

图5是示出图4的第一测试电路中所包括的第一发送器的配置的电路图。

图6是示出图4的第一测试电路中所包括的第一接收器的配置的电路图。

图7是示出图4的第一测试电路中所包括的第一输出电路的配置的电路图。

图8示出图2的第一测试控制电路中所包括的感测电路的配置。

图9是示出图1的半导体器件中所包括的第二测试控制电路的配置的框图。

图10是示出图9的第二测试控制电路中所包括的第二控制电路的配置的电路图。

图11示出图9的第二测试控制电路中所包括的第一连接电路的配置,连同图1所示的第一穿通电极一起。

图12是示出图11的第一连接电路中所包括的第二发送器的配置的电路图。

图13和图14示出根据本公开的实施例的半导体器件的第一测试操作。

图15和图16示出根据本公开的实施例的半导体器件的第二测试操作。

图17和图18是示出根据本公开的实施例的半导体器件的第一测试操作和第二测试操作的时序图。

具体实施方式

以下将参考附图描述本公开的各种实施例。然而,本文描述的实施例仅用于说明性目的,并不旨在限制本公开的范围。

如图1所示,根据实施例的半导体器件1可以包括第一半导体芯片10、第一传输穿通电极21和第二传输穿通电极22、第一至第四穿通电极23、24、25和26、以及第二半导体芯片30。

第一半导体芯片10可以包括第一测试控制电路11。

当芯片识别信号CID和开路测试信号OPT被使能时,第一测试控制电路11可以电连接并物理连接至第一至第四穿通电极23~26。当芯片识别信号CID和开路测试信号OPT被使能时,第一测试控制电路11可以顺序地测试第一至第四穿通电极23~26的开路故障。当芯片识别信号CID和短路测试信号SHT被使能时,第一测试控制电路11可以连接至第一至第四穿通电极23~26。当芯片识别信号CID和短路测试信号SHT被使能时,第一测试控制电路11可以测试第一穿通电极23与第二穿通电极24之间的故障、以及第三穿通电极25与第四穿通电极26之间的故障。例如,当芯片识别信号CID和短路测试信号SHT被使能时,第一测试控制电路11可以测试由于第一穿通电极23与第二穿通电极24之间发生的短路而引起的第一穿通电极23与第二穿通电极24之间的故障。例如,当芯片识别信号CID和短路测试信号SHT被使能时,第一测试控制电路11可以测试由于第三穿通电极25与第四穿通电极26之间发生短路而导致的第三穿通电极25与第四穿通电极25之间的故障。芯片识别信号CID可以被设置为用于激活第一半导体芯片10和第二半导体芯片30的信号。尽管图1以单条线示出了芯片识别信号CID,但是芯片识别信号CID可以是包括多个比特位的信号,其用于选择性地激活多个半导体芯片。开路测试信号OPT可以被使能以激活第一测试操作。短路测试信号SHT可以被使能以激活第二测试操作。第一测试操作可以是用于测试第一至第四穿通电极23~26的开路故障的操作。在一个实施例中,开路故障是指第一至第四穿通电极23~26中的至少一个与第一半导体芯片10和第二半导体芯片30中的至少一个电断开。第二测试操作可以是用于测试第一至第四穿通电极23~26之间的短路故障的操作。在一个实施例中,短路故障是指第一至第四穿通电极23~26中的至少两个相邻的电极彼此电连接。芯片识别信号CID可以经由第一传输穿通电极21从第一半导体芯片10传输到第二半导体芯片30。开路测试信号OPT和短路测试信号SHT可以经由第二传输电极22从第一半导体芯片10传输到第二半导体芯片30。

第一半导体芯片10可以在第一测试操作期间顺序地测试第一至第四穿通电极23~26的开路故障。第一半导体芯片10可以在第二测试操作期间测试第一穿通电极23与第二穿通电极24之间的短路故障。第一半导体芯片10可以在第二测试操作期间测试第三穿通电极25与第四穿通电极26之间的短路故障。第一半导体芯片10可以在第二测试操作期间测试第二穿通电极24与第三穿通电极25之间的短路故障。

第二半导体芯片30可以包括第二测试控制电路31。

当芯片识别信号CID和开路测试信号OPT被使能时,第二测试控制电路31可以电连接并物理连接至第一至第四穿通电极23~26。当芯片识别信号CID和短路测试信号SHT被使能时,第二测试控制电路31可以连接至第一至第四穿通电极23至26。

如上所述,第二半导体芯片30可以在第一测试操作和第二测试操作期间连接至第一至第四穿通电极23~26。

可以通过使用垂直贯穿半导体芯片的一般的穿通硅通孔(TSV)来实现第一传输穿通电极21和第二传输穿通电极22以及第一至第四穿通电极23~26。尽管图1示出的是六个穿通电极(即,第一传输穿通电极21和第二传输穿通电极22、以及第一至第四穿通电极23~26),但是可以根据实施例而将穿通电极的数量设置为小于或大于六个。另外,尽管图1示出的是半导体器件1包括两个半导体芯片(即,第一半导体芯片10和第二半导体芯片30)的示例,其中这两个半导体芯片通过第一传输穿通电极21和第二传输穿通电极22以及第一至第四穿通电极23~26来层叠和连接,但是可以根据实施例而将半导体器件1中所包括的半导体芯片的数量设置为大于两个。

参见图2,第一测试控制电路11可以包括第一控制电路110、第一测试电路120、第二测试电路130、第三测试电路140、第四测试电路150和感测电路160。

当芯片识别信号CID和开路测试信号OPT(或短路测试信号SHT)被使能时,第一控制电路110可以产生第一使能信号EN_TSV<1>和第一测试数据TD<1>。当芯片识别信号CID被使能为具有逻辑“高”电平、并且开路测试信号OPT和短路测试信号SHT中的任何一个被使能为具有逻辑“高”电平时,第一控制电路110可以产生被使能为具有逻辑“高”电平的第一使能信号EN_TSV<1>。当芯片识别信号CID被使能为具有逻辑“高”电平、并且开路测试信号OPT和短路测试信号SHT中的任何一个被使能为具有逻辑“高”电平时,第一控制电路110可以产生被使能为具有逻辑“低”电平的第一测试数据TD<1>。

第一控制电路110可以产生第一至第四开路开关信号OP_SW<1:4>,其在芯片识别信号CID和开路测试信号OPT被使能时而被顺序地使能。第一控制电路110可以产生第一和第二短路开关信号SH_SW<1:2>,其在芯片识别信号CID和短路测试信号SHT被使能时而被使能。

第一测试电路120可以基于第一使能信号EN_TSV<1>和第一测试数据TD<1>而将图1所示的第一穿通电极23驱动到预定逻辑电平。例如,第一测试电路120可以基于第一使能信号EN_TSV<1>和第一测试数据TD<1>而向第一穿通电极23施加电压以在第一穿通电极23上提供预定逻辑电平。第一测试电路120可以接收第一开路开关信号OP_SW<1>和第一短路开关信号SH_SW<1>以产生第一标志信号FLAG<1>。第一测试电路120可以连接至第一穿通电极23。所述预定逻辑电平可以根据实施例而被设置为逻辑“高”电平或逻辑“低”电平。如本文中关于参数所使用的词“预定”(诸如预定逻辑电平)是指参数用在过程或算法中之前参数的值被确定。对于一些实施例,参数的值在过程或算法开始之前被确定。在其他实施例中,在过程或算法期间但在参数被使用在过程或算法中之前参数的值被确定。

第二测试电路130可以基于第一使能信号EN_TSV<1>和第一测试数据TD<1>来将图1所示的第二穿通电极24驱动到预定逻辑电平。第二测试电路130可以连接至第二穿通电极24。第二测试电路130可以接收第二开路开关信号OP_SW<2>和第二短路开关信号SH_SW<2>以产生第二标志信号FLAG<2>。

第三测试电路140可以基于第一使能信号EN_TSV<1>和第一测试数据TD<1>来将图1所示的第三穿通电极25驱动到预定逻辑电平。第三测试电路140可以连接至第三穿通电极25。第三测试电路140可以接收第三开路开关信号OP_SW<3>和第三短路开关信号SH_SW<3>以产生第三标记信号FLAG<3>。

第四测试电路150可以基于第一使能信号EN_TSV<1>和第一测试数据TD<1>来将图1所示的第四穿通电极26驱动到预定逻辑电平。第四测试电路150可以连接至第四穿通电极26。第四测试电路150可以接收第四开路开关信号OP_SW<4>和第四短路开关信号SH_SW<4>以产生第四标志信号FLAG<4>。

当开路测试信号OPT或短路测试信号SHT被使能时,感测电路160可以合成第一至第四标志信号FLAG<1:4>以产生检测信号TSV_DET。当第一至第四穿通电极23~26中的至少一个具有开路故障或发生短路故障时,检测信号TSV_DET可以被使能。

参见图3,第一控制电路110可以包括第一选择信号发生电路111、逻辑电路112和第一开关信号发生电路113。

第一选择信号发生电路111可以在芯片识别信号CID和开路测试信号OPT被使能时产生被顺序地使能的第一至第四选择信号SEL<1:4>。第一选择信号发生电路111可以在芯片识别信号CID和短路测试信号SHT被使能时产生被使能的第一和第三选择信号SEL<1>和SEL<3>。

逻辑电路112可以被配置为执行或逻辑操作以及或非逻辑操作,并且可以包括或门OR11以及或非门NOR11。逻辑电路112可以产生第一使能信号EN_TSV<1>,其在开路测试信号OPT和短路测试信号SHT中的任何一个被使能为具有逻辑“高”电平时被使能为具有逻辑“高”电平。逻辑电路112可以对开路测试信号OPT和短路测试信号SHT执行或逻辑操作,以产生第一使能信号EN_TSV<1>。逻辑电路112可以产生第一测试数据TD<1>,其在开路测试信号OPT和短路测试信号SHT中的任何一个被使能为具有逻辑“高”电平时被使能为具有逻辑“低”电平。逻辑电路112可以对开路测试信号OPT和短路测试信号SHT执行逻辑或非操作,以产生第一测试数据TD<1>。

第一开关信号发生电路113可以被配置为执行与非操作,并且可以使用与非门NAND11和NAND12来实现。当开路测试信号OPT被使能为具有逻辑“高”时,第一开关信号发生电路113可以反相缓冲第一至第四选择信号SEL<1:4>以产生第一至第四开路开关信号OP_SW<1:4>。当短路测试信号SHT被使能为具有逻辑“高”时,第一开关信号发生电路113可以反相缓冲第一至第三选择信号SEL<1:3>以产生第一和第二短路开关信号SH_SW<1:2>。

图4示出图2的第一测试控制电路11中所包括的第一测试电路120的配置,连同图1所示的第一穿通电极23一起。

参见图4,第一测试电路120可以包括第一电阻器连接电路121、第一发送器122、第一接收器123和第一输出电路124。

第一电阻器连接电路121可以耦接在电源电压VDD端子与第一内部节点nd11之间,该第一内部节点nd11连接至第一穿通电极23。当第一开路开关信号OP_SW<1>被使能为具有逻辑“低”电平时,第一电阻器连接电路121可以将第一穿通电极23电连接至第一测试电阻器R21。当第一短路开关信号SH_SW<1>被使能为具有逻辑“低”电平时,第一电阻器连接电路121可以将第一穿通电极23电连接至第三测试电阻器R22。

例如,第一电阻器连接电路121可以包括第一测试电阻器R21和第一开关P21,第一测试电阻器R21和第一开关P21串联耦接在电源电压VDD端子与连接至第一穿通电极23的第一内部节点nd11之间。当第一开路开关信号OP_SW<1>被使能为具有逻辑“低”电平时,第一开关P21可以被接通以将第一测试电阻器R21电连接至第一穿通电极23。第一电阻器连接电路121还可以包括第三测试电阻器R22和第二开关P22,第三测试电阻器R22和第二开关P22串联耦接在电源电压VDD端子与连接至第一穿通电极23的第一内部节点nd11之间。当第一短路开关信号SH_SW<1>被使能为具有逻辑“低”电平时,第二开关P22可以被接通以将第三测试电阻器R22电连接至第一穿通电极23。第一测试电阻器R21可以被设置为具有如下电阻值的复制电阻器,该电阻值与被视为是没有开路故障的正常穿通电极的第一穿通电极23的电阻值相对应。在一个实施例中,如果在第一穿通电极23具有100欧姆的电阻值时不发生第一穿通电极23的开路故障,则第一测试电阻器R21的电阻值可以被设置为100欧姆。可以根据实施例而将第一测试电阻器R21的电阻值设置得不同。第三测试电阻器R22可以被设置为具有如下电阻值的复制电阻器,该电阻值与第一穿通电极23和第二穿通电极24之间不发生短路故障时第一穿通电极23和第二穿通电极24之间的电阻值相对应。在一个实施例中,如果在第一穿通电极23与第二穿通电极24之间的电阻值被设置为100KΩ时第一穿通电极23与第二穿通电极24之间不发生短路故障,则第三测试电阻器R22的电阻值可以被设置为100KΩ。可以根据实施例而将第三测试电阻器R22的电阻值设置得不同。

第一发送器122可以基于第一使能信号EN_TSV<1>和第一测试数据TD<1>而将第一穿通电极23的电平驱动到预定逻辑电平。当第一使能信号EN_TSV<1>被使能并且第一测试数据TD<1>被使能时,第一发送器122可以将第一穿通电极23的电平驱动到所述预定逻辑电平。所述预定逻辑电平可以被设置为逻辑“低”电平。

第一接收器123可以检测第一内部节点nd11的电压电平以产生第一内部检测信号IDET。第一接收器123可以缓冲第一内部节点nd11的电压信号以产生第一内部检测信号IDET。

当开路测试信号OPT和短路测试信号SHT中的任何一个被使能时,第一输出电路124可以从第一内部检测信号IDET产生第一标志信号FLAG<1>。

图2中所示的第二至第四测试电路130、140和150中的每一个可以被实现为具有与参考图4描述的第一测试电路120基本相同的电路,除了其输入和输出信号之外。因此,在下文中将省略对第二至第四测试电路130、140和150的描述。另外,尽管在图4中未示出第二穿通电极24,但是第二穿通电极24可以布置成与第一穿通电极23相邻,如图1所示。

参见图5,第一发送器122可以包括第一上拉/下拉信号发生电路1221和第一驱动电路1222。

第一上拉/下拉信号发生电路1221可以被配置为执行反相、与非、以及或非操作,并且可以被实现为包括反相器IV31、与非门NAND31、以及或非门NOR31。当第一使能信号EN_TSV<1>被使能为具有逻辑“高”电平时,第一上拉/下拉信号发生电路1221可以反相缓冲第一测试数据TD<1>以产生第一上拉信号PU<1>。当第一使能信号EN_TSV<1>被使能为具有逻辑“高”电平时,第一上拉/下拉信号发生电路1221可以反相缓冲第一测试数据TD<1>以产生第一下拉信号PD<1>。当第一使能信号EN_TSV<1>被使能为具有逻辑“高”电平并且第一测试数据TD<1>被使能为具有逻辑“低”电平时,第一上拉/下拉信号发生电路1221可以产生具有逻辑“高”电平的第一上拉信号PU<1>和具有逻辑“高”电平的第一下拉信号PD<1>。

第一驱动电路1222可以被实现为包括:PMOS晶体管P31,其耦接在电源电压VDD端子与连接至第一穿通电极23的第一内部节点nd11之间;以及NMOS晶体管N31,其耦接在第一内部节点nd11与接地电压VSS端子之间。当第一上拉信号PU<1>具有逻辑“低”电平时,第一驱动电路1222可以将第一内部节点nd11的电平上拉至电源电压VDD。当第一下拉信号PD<1>具有逻辑“高”电平时,第一驱动电路1222可以将第一内部节点nd11的电平下拉至接地电压VSS。

参见图6,第一接收器123可以被配置为执行反相操作,并且可以被实现为包括串联连接的反相器IV41和IV42。

第一接收器123可以缓冲第一内部节点nd11的电压信号以产生第一内部检测信号IDET。

参见图7,第一输出电路124可以被实现为包括反相器IV51和多路复用器MUX51。

当开路测试信号OPT被使能时,第一输出电路124可以反相缓冲第一内部检测信号IDET,以输出第一内部检测信号IDET的反相缓冲信号作为第一标志信号FLAG<1>。当短路测试信号SHT被使能时,第一输出电路124可以缓冲第一内部检测信号IDET,以输出第一内部检测信号IDET的缓冲信号作为第一标志信号FLAG<1>。

参见图8,感测电路160可以包括合成信号发生电路161、输出控制信号发生电路162和检测信号发生电路163。

合成信号发生电路161可以被配置为执行与非操作以及或非操作,并且可以被实现为包括与非门NAND61和NAND62、以及或非门NOR61。当所有的第一至第四标志信号FLAG<1:4>都具有逻辑“高”电平时,合成信号发生电路161可以产生具有逻辑“高”电平的合成信号SUM。当第一至第四标志信号FLAG<1:4>中的至少一个具有逻辑“低”电平时,合成信号发生电路161可以产生具有逻辑“低”电平的合成信号SUM。

输出控制信号发生电路162可以被配置为执行或非操作,并且可以使用或非门NOR62来实现。当开路测试信号OPT和短路测试信号SHT二者均被禁止为逻辑“低”电平时,输出控制信号发生电路162可以产生具有逻辑“高”电平的输出控制信号OUT_CON。当开路测试信号OPT和短路测试信号SHT中的任何一个被使能为逻辑“高”电平时,输出控制信号发生电路162可以产生具有逻辑“低”电平的输出控制信号OUT_CON。

检测信号发生电路163可以使用触发器FF61来实现。当输出控制信号OUT_CON被使能为具有逻辑“高”电平时,检测信号发生电路163可以输出合成信号SUM作为检测信号TSV_DET。

参见图9,第二测试控制电路31可以包括第二控制电路310、第一连接电路320、第二连接电路330、第三连接电路340和第四连接电路350。

当芯片识别信号CID被使能、并且开路测试信号OPT和短路测试信号SHT中的任何一个被使能时,第二控制电路310可以产生第二使能信号EN_TSV<2>和第二测试数据TD<2>。

第一连接电路320可以基于第二使能信号EN_TSV<2>和第二测试数据TD<2>而将图1所示的第一穿通电极23的电平驱动到预定逻辑电平。

第二连接电路330可以基于第二使能信号EN_TSV<2>和第二测试数据TD<2>而将图1所示的第二穿通电极24的电平驱动到预定逻辑电平。

第三连接电路340可以基于第二使能信号EN_TSV<2>和第二测试数据TD<2>而将图1所示的第三穿通电极25的电平驱动到预定逻辑电平。

第四连接电路350可以基于第二使能信号EN_TSV<2>和第二测试数据TD<2>而将图1所示的第四穿通电极26的电平驱动到预定逻辑电平。

参见图10,第二控制电路310可以被配置为执行反相以及或非操作,并且可以被实现为包括反相器IV71和IV72、以及或非门NOR71和NOR72。

第二控制电路310可基于芯片识别信号CID、开路测试信号OPT和短路测试信号SHT来产生第二使能信号EN_TSV<2>和第二测试数据TD<2>。当芯片识别信号CID被使能为具有逻辑“高”电平、并且开路测试信号OPT和短路测试信号SHT中的任何一个被使能为具有逻辑“高”电平时,第二控制电路310可以产生被使能为具有逻辑“高”电平的第二使能信号EN_TSV<2>。当芯片识别信号CID被使能为具有逻辑“高”电平、并且开路测试信号OPT和短路测试信号SHT中的任何一个被使能为具有逻辑“高”电平时,第二控制电路310可以产生被使能为具有逻辑“低”电平的第二测试数据TD<2>。

图11示出图9的第二测试控制电路31中所包括的第一连接电路320的配置,连同图1所示的第一穿通电极23一起。

参见图11,第一连接电路320可以包括第二发送器321和第二接收器322。

第二发送器321可以基于第二使能信号EN_TSV<2>和第二测试数据TD<2>而将第三内部节点nd31驱动到预定逻辑电平,该第三内部节点nd31连接至第一穿通电极23。

第二接收器322可以接收并输出第三内部节点nd31的信号。第二接收器322可以经由第一穿通电极23接收信号并且可以输出信号。第二接收器322可以使用一般的接收器来实现。

图9中所示的第二至第四连接电路330、340和350中的每一个可以被实现为具有与参考图11所述的第一连接电路320基本相同的电路,除了其输入和输出信号之外。因此,在下文中将省略对第二至第四连接电路330、340和350的描述。

参见图12,第二发送器321可以包括第二上拉/下拉信号发生电路3211和第二驱动电路3212。

第二上拉/下拉信号发生电路3211可以被配置为执行反相、与非、以及或非操作,并且可以被实现为包括反相器IV81、与非门NAND81、以及或非门NOR81。当第二使能信号EN_TSV<2>被使能为具有逻辑“高”电平时,第二上拉/下拉信号发生电路3211可以反相缓冲第二测试数据TD<2>以产生第二上拉信号PU<2>。当第二使能信号EN_TSV<2>被使能为具有逻辑“高”电平时,第二上拉/下拉信号发生电路3211可以反相缓冲第二测试数据TD<2>以产生第二下拉信号PD<2>。当第二使能信号EN_TSV<2>被使能为具有逻辑“高”电平并且第二测试数据TD<2>被使能为具有逻辑“低”电平时,第二上拉/下拉信号发生电路3211可以产生具有逻辑“高”电平的第二上拉信号PU<2>和具有逻辑“高”电平的第二下拉信号PD<2>。

第二驱动电路3212可以被实现为包括:PMOS晶体管P81,其耦接在电源电压VDD端子与连接至第一穿通电极23的第三内部节点nd31之间;以及NMOS晶体管N81,其耦接在第三内部节点nd31与接地电压VSS端子之间。当第二上拉信号PU<2>具有逻辑“低”电平时,第二驱动电路3212可以将第三内部节点nd31的电平上拉至电源电压VDD。当第二下拉信号PD<2>具有逻辑“高”电平时,第二驱动电路3212可以将第三内部节点nd31的电平下拉至接地电压VSS。

图13和图14示出根据本公开的实施例的半导体器件的第一测试操作。

在下文中,将参照图13描述在第一测试操作期间、与第一穿通电极23连接的第一测试电路120和第一连接电路320的操作。

如参考图2所描述的,当芯片识别信号CID和开路测试信号OPT被使能时,第一控制电路110可以产生具有逻辑“高”电平的第一使能信号EN_TSV<1>和具有逻辑“低”电平的第一测试数据TD<1>。当芯片识别信号CID和开路测试信号OPT被使能时,第一控制电路110可以产生被使能为具有逻辑“低”电平的第一开路开关信号OP_SW<1>。

如参考图9所描述的,当芯片识别信号CID和开路测试信号OPT被使能时,第二控制电路310可以产生具有逻辑“高”电平的第二使能信号EN_TSV<2>和具有逻辑“低”电平的第二测试数据TD<2>。

在第一电阻器连接电路121中,当第一开路开关信号OP_SW<1>被使能为具有逻辑“低”电平时,第一开关P21可以被接通以将第一测试电阻器R21电连接至与第一穿通电极23连接的第一内部节点nd11。

第一发送器122可以基于具有逻辑“高”电平的第一使能信号EN_TSV<1>和具有逻辑“低”电平的第一测试数据TD<1>,将第一穿通电极23的电平驱动到逻辑“低”电平。

第二发送器321可以基于具有逻辑“高”电平的第二使能信号EN_TSV<2>和具有逻辑“低”电平的第二测试数据TD<2>,将与第一穿通电极23连接的第三内部节点nd31电连接至接地电压VSS端子。在这种情况下,可以在电源电压VDD端子与接地电压VSS端子之间提供第一电流路径I1,并且可以通过第一电流路径I1将电源电压VDD分压,以使得确定第一内部节点nd11的电压电平。尽管在图13中未示出接地电压VSS端子,但是第二发送器321的接地电压VSS端子可以对应于图12所示的接地电压VSS端子。

第一接收器123可以检测第一内部节点nd11的电压电平以产生第一内部检测信号IDET。

因为开路测试信号OPT被使能,第一输出电路124可以从第一内部检测信号IDET产生第一标志信号FLAG<1>。

在下文中,将参考图14的图来描述用于在第一测试操作期间测试第一穿通电极23的开路故障的第一内部节点nd11的电压电平。在图14的图中,横坐标表示第一穿通电极23的电阻值R,纵坐标表示第一内部节点nd11的电压电平。

如上所述,当由电源电压VDD端子与接地电压VSS端子之间的第一电流路径I1所确定的第一内部节点nd11的电压电平“V(nd11)”低于电源电压VDD的一半时,第一穿通电极23可以被视为是没有开路故障的正常穿通电极(PASS)。

在一个实施例中,如果第一穿通电极23被视为是没有开路故障的正常穿通电极(PASS),当第一测试电阻器R21具有100欧姆的电阻值时,第一穿通电极23可以具有小于100欧姆的电阻值。因此,第一内部节点nd11的电压电平“V(nd11)”可以低于电源电压VDD的一半。在一个实施例中,可以将第一测试电阻器R21的电阻值设置为与被视为是没有开路故障的正常穿通电极的第一穿通电极23的电阻值相对应。

相反,当由电源电压VDD端子与接地电压VSS端子之间的第一电流路径I1所确定的第一内部节点nd11的电压电平“V(nd11)”高于电源电压VDD的一半时,第一穿通电极23可以被视为是具有开路故障的异常穿通电极(FAIL)。

在一个实施例中,如果第一穿通电极23被视为是具有开路故障的异常穿通电极(PASS),当第一测试电阻器R21具有100欧姆的电阻值时,第一穿通电极23可以具有大于100欧姆的电阻值。因此,第一内部节点nd11的电压电平“V(nd11)”可以高于电源电压VDD的一半。

在下文中,将参照图15描述在第二测试操作期间与第一穿通电极23和第二穿通电极24中的相应穿通电极连接的第一测试电路120和第二连接电路330的操作。

如参考图2所述的,当芯片识别信号CID和短路测试信号SHT被使能时,第一控制电路110可以产生具有逻辑“高”电平的第一使能信号EN_TSV<1>和具有逻辑“低”电平的第一测试数据TD<1>。当芯片识别信号CID和短路测试信号SHT被使能时,第一控制电路110可以产生被使能为具有逻辑“低”电平的第一短路开关信号SH_SW<1>。

如参考图9所述的,当芯片识别信号CID和短路测试信号SHT被使能时,第二控制电路310可以产生具有逻辑“高”电平的第二使能信号EN_TSV<2>和具有逻辑“低”电平的第二测试数据TD<2>。

在第一电阻器连接电路121中,当第一短路开关信号SH_SW<1>被使能为具有逻辑“低”电平时,第二开关P22可以被接通以将第三测试电阻器R22电连接至与第一穿通电极23连接的第一内部节点nd11。

第一发送器122可以基于具有逻辑“高”电平的第一使能信号EN_TSV<1>和具有逻辑“低”电平的第一测试数据TD<1>,将第一穿通电极23的电平驱动到逻辑“低”电平。

第二连接电路330的第三发送器331可以基于具有逻辑“高”电平的第二使能信号EN_TSV<2>和具有逻辑“低”电平的第二测试数据TD<2>,将与第二穿通电极24连接的第四内部节点nd32电连接至接地电压VSS端子。在这种情况下,可以在电源电压VDD端子与接地电压VSS端子之间提供第二电流路径I2,并且可以通过第二电流路径I2将电源电压VDD分压,以使得确定内部节点nd11的电压电平。尽管在图15中未示出接地电压VSS端子,但是第三发送器331的接地电压VSS端子可以对应于图12所示的接地电压VSS端子。

第一接收器123可以检测第一内部节点nd11的电压电平以产生第一内部检测信号IDET。

因为短路测试信号SHT被使能,所以第一输出电路124可以从第一内部检测信号IDET产生第一标志信号FLAG<1>。

在下文中,将参考图16的图来描述用于在第二测试操作期间测试第一穿通电极23与第二穿通电极24之间的短路故障的第一内部节点nd11的电压电平。在图16的图中,横坐标表示第一穿通电极23与第二穿通电极24之间的电阻值R,纵坐标表示第一内部节点nd11的电压电平。

如上所述,当由电源电压VDD端子与接地电压VSS端子之间的第一电流路径I2所确定的第一内部节点nd11的电压电平“V(nd11)”低于电源电压VDD的一半时,第二电流路径I2可以被视为是具有短路故障的异常电流路径(FAIL),该短路故障是由于第一穿通电极23与第二穿通电极24之间的泄漏电流路径引起的。

在一个实施例中,如果第二电流路径I2被视为是具有短路故障的异常电流路径(FAIL),当第三测试电阻器R22具有100欧姆的电阻值时,第一穿通电极23与第二穿通电极24之间的电阻值可以等于或小于100欧姆。因此,第一内部节点nd11的电压电平“V(nd11)”可以低于电源电压VDD的一半。在一个实施例中,第三测试电阻器R22的电阻值可以被设置为与第一穿通电极23和第二通电极24之间没有短路故障时第一穿通电极23和第二穿通电极24之间的电阻值相对应。在一些实施例中,第三测试电阻器R22具有大于第一测试电阻器R21的电阻值。

相反,当由电源电压VDD端子与接地电压VSS端子之间的第二电流路径I2所确定的第一内部节点nd11的电压电平“V(nd11)”高于电源电压VDD的一半时,第二电流路径I2可以被视为是在第一穿通电极23与第二穿通电极24之间没有短路故障的正常电流路径(PASS)。

在一个实施例中,如果第二电流路径I2被视为是没有短路故障的正常电流路径(PASS),当第三测试电阻器R22具有100欧姆的电阻值时,第一穿通电极23与第二穿通电极24之间的电阻值可以大于100欧姆。因此,第一内部节点nd11的电压电平“V(nd11)”可以高于电源电压VDD的一半。

在下文中将参考图17,结合第一至第四穿通电极23~26全部都没有开路故障的示例以及第二穿通电极24具有开路故障的示例,来描述根据实施例的第一测试操作。

首先,在下文中将描述第一至第四穿通电极23~26全部都没有开路故障的示例。

在时间点“T1”,开路测试信号OPT可以被使能为具有逻辑“高”电平,以用于执行第一测试操作。

第一控制电路110可以接收芯片识别信号CID和开路测试信号OPT,以产生被使能为具有逻辑“高”电平的第一选择信号SEL<1>、被使能为具有逻辑“高”电平的第一使能信号EN_TSV<1>、以及具有逻辑“低”电平的第一测试数据TD<1>。第一控制电路110可以接收芯片识别信号CID和开路测试信号OPT以产生被使能为具有逻辑“低”电平的第一开路开关信号OP_SW<1>。

第二控制电路310可以接收芯片识别信号CID和开路测试信号OPT,以产生被使能为具有逻辑“高”电平的第二使能信号EN_TSV<2>和具有逻辑“低”电平的第二测试数据TD<2>。

第一测试电路120可以基于第一使能信号EN_TSV<1>和第一测试数据TD<1>,将第一穿通电极23的电平驱动为逻辑“低”电平。第一测试电路120可以响应于第一开路开关信号OP_SW<1>而将第一测试电阻器R21电连接至第一穿通电极23。

第一连接电路320可以基于第二使能信号EN_TSV<2>和第二测试数据TD<2>而将第一穿通电极23电连接至接地电压VSS端子。

第一测试电路120可以检测第一内部节点nd11的电压电平以产生具有逻辑“高”电平的第一标志信号FLAG<1>。

在时间点“T2”,第一控制电路110可以接收芯片识别信号CID和开路测试信号OPT,以产生被使能为逻辑“高”电平的第二选择信号SEL<2>、被使能为逻辑“高”电平的第一使能信号EN_TSV<1>、以及具有逻辑“低”电平的第一测试数据TD<1>。第一控制电路110可以接收芯片识别信号CID和开路测试信号OPT以产生被使能为具有逻辑“低”电平的第二开路开关信号OP_SW<2>。

第二测试电路130可以基于第一使能信号EN_TSV<1>和第一测试数据TD<1>,将第二穿通电极24的电平驱动到逻辑“低”电平。第二测试电路130可以响应于第二开路开关信号OP_SW<2>而将第二测试电阻器(未示出)电连接至第二穿通电极24。

第二连接电路330可以基于第二使能信号EN_TSV<2>和第二测试数据TD<2>而将第二穿通电极24电连接至接地电压VSS端子。

第二测试电路130可以检测第二内部节点(未示出)的电压电平,以产生具有逻辑“高”电平的第二标志信号FLAG<2>。

针对第三穿通电极25的第一测试操作可以与在第一时间点“T1”执行的上述操作相同,并且针对第四穿通电极26的第一测试操作可以与在第二时间点“T2”执行的上述操作相同。因此,以下将省略针对第三穿通电极25和第四穿通电极26的第一测试操作。

在时间点“T3”,合成信号发生电路161可以合成第一至第四标志信号FLAG<1:4>以产生具有逻辑“高”电平的合成信号SUM。

在时间点“T4”,因为开路测试信号OPT被禁止为具有逻辑“低”电平,输出控制信号发生电路162可以产生具有逻辑“高”电平的输出控制信号OUT_CON。

因为输出控制信号OUT_CON被使能为具有逻辑“高”电平,检测信号发生电路163可以从合成信号SUM产生具有逻辑“高”电平的检测信号TSV_DET。

根据以上描述,当第一至第四穿通电极23~26全部都没有开路故障时,检测信号TSV_DET可以被产生为具有逻辑“高”电平。因此,半导体器件1可以将第一至第四穿通电极23~26视为是没有任何开路故障的正常穿通电极。

接下来,将在下文中描述第二穿通电极24具有开路故障的示例。

在时间点“T1”,开路测试信号OPT可以被使能为具有逻辑“高”电平,以用于执行第一测试操作。

第一控制电路110可以接收芯片识别信号CID和开路测试信号OPT,以产生被使能为具有逻辑“高”电平的第一选择信号SEL<1>、被使能为具有逻辑“高”电平的第一使能信号EN_TSV<1>、具有逻辑“低”电平的第一测试数据TD<1>。第一控制电路110可以接收芯片识别信号CID和开路测试信号OPT以产生被使能为具有逻辑“低”电平的第一开路开关信号OP_SW<1>。

第二控制电路310可以接收芯片识别信号CID和开路测试信号OPT,以产生被使能为具有逻辑“高”电平的第二使能信号EN_TSV<2>、以及具有逻辑“低”电平的第二测试数据TD<2>。

第一测试电路120可以基于第一使能信号EN_TSV<1>和第一测试数据TD<1>而将第一穿通电极23的电平驱动到逻辑“低”电平。第一测试电路120可以响应于第一开路开关信号OP_SW<1>而将第一测试电阻器R21电连接至第一穿通电极23。

第一连接电路320可以基于第二使能信号EN_TSV<2>和第二测试数据TD<2>而将第一穿通电极23电连接至接地电压VSS端子。

第一测试电路120可以检测第一内部节点nd11的电压电平以产生具有逻辑“高”电平的第一标志信号FLAG<1>。

在时间点“T2”,第一控制电路110可以接收芯片识别信号CID和开路测试信号OPT,以产生被使能为具有逻辑“低”电平的第二开路开关信号OP_SW<2>。

第二测试电路130可以基于第一使能信号EN_TSV<1>和第一测试数据TD<1>而将第二穿通电极24的电平驱动到逻辑“低”电平。第二测试电路130可以响应于第二开路开关信号OP_SW<2>而将第二测试电阻器(未示出)电连接至第二穿通电极24。

第二连接电路330可以基于第二使能信号EN_TSV<2>和第二测试数据TD<2>而将第二穿通电极24电连接至接地电压VSS端子。

第二测试电路130可以检测第二内部节点(未示出)的电压电平,以产生具有逻辑“低”电平的第二标志信号FLAG<2>。

针对第三穿通电极25的第一测试操作可以与在第一时间点“T1”执行的上述操作相同,并且针对第四穿通电极26的第一测试操作可以与在第二时间点“T2”执行的上述操作相同。因此,以下将省略针对第三穿通电极25和第四穿通电极26的第一测试操作。

在时间点“T3”,合成信号发生电路161可以合成第一至第四标志信号FLAG<1:4>以产生具有逻辑“低”电平的合成信号SUM。

在时间点“T4”,因为开路测试信号OPT被禁止为具有逻辑“低”电平,输出控制信号发生电路162可以产生具有逻辑“高”电平的输出控制信号OUT_CON。

因为输出控制信号OUT_CON被使能为具有逻辑“高”电平,检测信号发生电路163可以从合成信号SUM产生具有逻辑“低”电平的检测信号TSV_DET。

根据以上描述,当第一至第四穿通电极23~26之中的第二穿通电极24具有开路故障时,检测信号TSV_DET可以被产生为具有逻辑“低”电平。因此,半导体器件1可以识别出第一至第四穿通电极23~26中的至少一个具有开路故障。

在下文中将参考图18,结合在第一穿通电极23与第二穿通电极24之间不存在短路故障的示例以及在第一穿通电极23与第二穿通电极24之间存在短路故障的示例,来描述根据实施例的第二测试操作。

首先,在下文中将描述在第一穿通电极23与第二穿通电极24之间不存在短路故障的示例。

在时间点“T11”,短路测试信号SHT可以被使能为具有逻辑“高”电平,以用于执行第二测试操作。

第一控制电路110可以接收芯片识别信号CID和短路测试信号SHT,以产生被使能为具有逻辑“高”电平的第一选择信号SEL<1>、被使能为具有逻辑“高”电平的第一使能信号EN_TSV<1>、具有逻辑“低”电平的第一测试数据TD<1>。第一控制电路110可以接收芯片识别信号CID和短路测试信号SHT,以产生被使能为具有逻辑“低”电平的第一短路开关信号SH_SW<1>。

第二控制电路310可以接收芯片识别信号CID和短路测试信号SHT,以产生被使能为具有逻辑“高”电平的第二使能信号EN_TSV<2>和具有逻辑“低”电平的第二测试数据TD<2>。

第一测试电路120可以基于第一使能信号EN_TSV<1>和第一测试数据TD<1>,将第一穿通电极23的电平驱动到逻辑“低”电平。第一测试电路120可以响应于第一短路开关信号SH_SW<1>而将第三测试电阻器R22电连接至第一穿通电极23。

第二连接电路330可以基于第二使能信号EN_TSV<2>和第二测试数据TD<2>而将第二穿通电极24电连接至接地电压VSS端子。

第一测试电路120可以检测第一内部节点nd11的电压电平以产生具有逻辑“高”电平的第一标志信号FLAG<1>。在这种情况下,第二至第四标志信号FLAG<2:4>可以被产生为具有逻辑“高”电平。

合成信号发生电路161可以合成第一至第四标志信号FLAG<1:4>以产生具有逻辑“高”电平的合成信号SUM。

在时间点“T12”,因为短路测试信号SHT被禁止为具有逻辑“低”电平,输出控制信号发生电路162可以产生具有逻辑“高”电平的输出控制信号OUT_CON。

因为输出控制信号OUT_CON被使能为具有逻辑“高”电平,检测信号发生电路163可以从合成信号SUM产生具有逻辑“高”电平的检测信号TSV_DET。

根据以上描述,当在第一穿通电极23与第二穿通电极24之间不存在短路故障时,检测信号TSV_DET可以被产生为具有逻辑“高”电平。因此,半导体器件1可以识别出在第一至第四穿通电极23~26之间不存在短路故障。

接下来,在下文中将描述在第一穿通电极23与第二穿通电极24之间存在短路故障的示例。

在时间点“T11”,短路测试信号SHT可以被使能为具有逻辑“高”电平,以用于执行第二测试操作。

第一控制电路110可以接收芯片识别信号CID和短路测试信号SHT,以产生被使能为具有逻辑“高”电平的第一选择信号SEL<1>、被使能为具有逻辑“高”电平的第一使能信号EN_TSV<1>、以及具有逻辑“低”电平的第一测试数据TD<1>。第一控制电路110可以接收芯片识别信号CID和短路测试信号SHT,以产生被使能为具有逻辑“低电平”的第一短路开关信号SH_SW<1>。

第二控制电路310可以接收芯片识别信号CID和短路测试信号SHT,以产生被使能为具有逻辑“高”电平的第二使能信号EN_TSV<2>和具有逻辑“低”电平的第二测试数据TD<2>。

第一测试电路120可以基于第一使能信号EN_TSV<1>和第一测试数据TD<1>,将第一穿通电极23的电平驱动到逻辑“低”电平。第一测试电路120可以响应于第一短路开关信号SH_SW<1>而将第三测试电阻器R22电连接至第一穿通电极23。

第二连接电路330可以基于第二使能信号EN_TSV<2>和第二测试数据TD<2>而将第二穿通电极24电连接至接地电压VSS端子。

第一测试电路120可以检测第一内部节点nd11的电压电平,以产生具有逻辑“低”电平的第一标志信号FLAG<1>。在这种情况下,第二至第四标志信号FLAG<2:4>可以被产生为具有逻辑“高”电平。

合成信号发生电路161可以合成第一至第四标志信号FLAG<1:4>以产生具有逻辑“低”电平的合成信号SUM。

在时间点“T12”,因为短路测试信号SHT被禁止为具有逻辑“低”电平,输出控制信号发生电路162可以产生具有逻辑“高”电平的输出控制信号OUT_CON。

因为输出控制信号OUT_CON被使能为具有逻辑“高”电平,检测信号发生电路163可以从合成信号SUM产生具有逻辑“低”电平的检测信号TSV_DET。

根据以上描述,当在第一穿通电极23与第二穿通电极24之间存在短路故障时,检测信号TSV_DET可以被产生为具有逻辑“低”电平。因此,半导体器件1可以识别出在第一至第四穿通电极23~26之间存在短路故障。

如上所述,根据实施例的半导体器件可以将多个穿通电极电连接至具有与开路故障或短路故障相对应的电阻值的测试电阻器,并且可以检测与所述多个穿通电极连接的内部节点的电压电平以测试所述多个穿通电极的开路故障或短路故障。

- 包括穿通电极的半导体芯片以及测试该穿通电极的方法

- 包括带电荷穿通阻止层以降低穿通的半导体器件及其制造方法