IC芯片电磁兼容性测试方法、装置和可读存储介质

文献发布时间:2023-06-19 09:32:16

技术领域

本发明涉及电力设备异常检测技术领域,具体涉及一种IC芯片电磁兼容性测试方法、装置和可读存储介质。

背景技术

世界范围内电子产品正在以无线、便携、多功能与专业化得趋势快速发展,纯粹的模拟电子系统越来越难以进入人们的视线,取而代之的集成电路在数字电子产品与电子系统中扮演了“超级明星”的角色,而这个主角被接纳的程度也在随着集成电路产业的发展不断加深,从1965年Gordon Moore提出摩尔定律至今,集成电路一直保持着每18-24个月集成度翻番、价格减半的发展趋势,这为集成电路的大范围、多层次应用奠定了基础。同时,这种快速发展也造成了电子系统电磁兼容性问题的日益突出,更高的集成度和使用密度,是片内和片外耦合的发生几率大大提高。在电子产品和电子系统中,通常集成电路是最根本的骚扰信号源,它把直流供电转换成高频的电流、电压,造成了无意发射和耦合。而当其输入或供电受到干扰时,误动作的可能性将大大增加,甚至造成硬件损坏。这种情况下,如何衡量集成电路电磁兼容性的问题日渐凸显起来。因此,亟需提供一种快速,且准确测量IC(Integrated Circuit,集成电路)芯片电磁兼容性的方法。

发明内容

基于上述现状,本发明主要目的在于提供一种IC芯片电磁兼容性测试方法、装置和可读存储介质,以提高IC芯片电磁兼容性的测试效率和测试准确率。

为实现上述目的,本发明采用的技术方案如下:

一种IC芯片电磁兼容性测试方法,所述IC芯片电磁兼容性测试方法应用于测试装置,所述测试装置包括测试探头和阻抗匹配网络;所述测试探头连接IC芯片的待测试引脚,所述测试探头连接校准实验电路,所述阻抗匹配网络连接实验接收机,所述阻抗匹配网络中设置有16.8nF电容;所述IC芯片电磁兼容性测试方法包括以下步骤:

S100,通过所述校准实验电路测量所述测试探头的探头电压和插入损耗;

S200,计算所述探头电压和所述插入损耗之间的差值,并在所述差值大于预设的去耦限值时,执行步骤S300;

S300,判定与所述测试探头连接的阻抗匹配网络处于正常状态,所述测试探头的校准操作成功;

S400,获取所述实验接收机的输出电压,并获取所述输出电压对应的测试频率;

S500,基于测试频率与电压阈值之间的映射关系获取所述测试频率对应的电压阈值,并判断所述输出电压是否大于所述电压阈值;若所述输出电压大于所述电压阈值,则执行步骤S600;若所述输出电压小于或者等于所述电压阈值,则执行步骤S700;

S600,判定所述待测试引脚不符合电磁兼容性要求;

S700,判定所述待测试引脚符合电磁兼容性要求。

优选地,所述测试探头安装在探针针套上,所述探针针套通过插头连接器与所述阻抗匹配网络的PCB板连接。

优选地,在所述步骤S200中,若所述差值小于或者等于所述去耦限值,则执行步骤S800;

S800,判定所述测试探头的校准操作失败,并提示用户更换所述阻抗匹配网络中元器件。

优选地,所述校准实验电路的输入端口与射频发生器连接,所述校准实验电路的输出端口与所述测试探头连接;在所述步骤S100中,所述通过所述校准实验电路测量所述测试探头的探头电压和插入损耗的步骤包括:

当所述射频发生器与所述测试探头之间的跳线处于断开状态时,通过所述射频发生器在预设频率范围内进行扫频操作,以测量得到所述测试探头的探头电压;

当所述射频发生器与所述测试探头之间的跳线处于连接状态时,通过所述射频发生器在预设频率范围内进行扫频操作,以测量得到所述测试探头的插入损耗。

优选地,所述IC芯片电磁兼容性测试方法还包括步骤:

计算所述阻抗匹配网络的输入阻抗、插入损耗和输出电压与输入电压之间的电压比值;

计算所述输入阻抗的计算公式为:

其中,Z

计算所述插入损耗IL

计算电压比值VR的计算公式为:

判断所述输入阻抗、插入耗损和电压比值是否符合对应的预设条件;

若所述输入阻抗、插入损耗和电压比值均符合对应的预设条件,则判定当前的阻抗匹配网络符合阻抗匹配网络的特性;

若所述输入阻抗、插入损耗和电压比值至少一个未符合对应的预设条件,则判定当前的阻抗匹配网络不符合阻抗匹配网络的特性,并提示用户更换所述阻抗匹配网络中元器件。

优选地,R1=120Ω,R2=50Ω,R

所述输入阻抗对应的预设条件是输入阻抗大小为145Ω±20Ω;

所述插入损耗对应的预设条件是插入损耗大小为-11.75dB±2dB;

所述电压比值对应的预设条件是电压比值大小为-15.2dB±2dB。

本发明还提供一种IC芯片电磁兼容性测试系统,所述测试系统包括测试装置、校准实验电路和实验接收机,所述测试装置包括测试探头和阻抗匹配网络;所述测试探头连接校准实验电路,所述测试探头连接IC芯片的待测试引脚,所述阻抗匹配网络连接实验接收机,所述阻抗匹配网络中设置有16.8nF电容;

所述测试装置包括:

测量模块,用于通过所述校准实验电路测量所述测试探头的探头电压和插入损耗;

计算模块,用于计算所述探头电压和所述插入损耗之间的差值;

第一判断模块,用于判断所述差值是否大于预设的去耦限值;

第一判定模块,用于在所述第一判断模块的判断结果为是时,判定与所述测试探头连接的阻抗匹配网络处于正常状态,所述测试探头的校准操作成功;

获取模块,用于获取所述实验接收机的输出电压,并获取所述输出电压对应的测试频率;基于测试频率与电压阈值之间的映射关系获取所述测试频率对应的电压阈值;

第二判断模块,用于判断所述输出电压是否大于所述电压阈值;

第二判定模块,用于在所述第二判断模块的判断结果为是时,判定所述待测试引脚不符合电磁兼容性要求;在所述第二判断模块的判断结果为否时,判定所述待测试引脚符合电磁兼容性要求。

优选地,所述测试探头安装在探针针套上,所述探针针套通过插头连接器与所述阻抗匹配网络的PCB板连接。

优选地,所述第一判定模块还用于在所述第一判断模块的判断结果为否时,判定所述测试探头的校准操作失败,并提示用户更换所述阻抗匹配网络中元器件。

本发明还提供一种计算机可读存储介质,所述计算机可读存储介质上存储有检测程序,所述检测程序被处理器执行时实现如所述的IC芯片电磁兼容性测试方法的步骤。

【有益效果】

先校准实验电路校准测试探头,再通过设置有16.8nF电容的阻抗匹配网络来连接实验接收机,然后通过测试探头连接IC芯片的待测试引脚,获取实验接收机的输出电压,并获取输出电压对应的测试频率;基于测试频率与电压阈值之间的映射关系获取测试频率对应的电压阈值,若输出电压大于电压阈值,则判定待测试引脚不符合电磁兼容性要求;若输出电压小于或者等于电压阈值,则判定待测试引脚符合电磁兼容性要求。实现了校准测试探头后,再通过测试探头来测试IC芯片的电磁兼容性,提高了IC芯片电磁兼容性的测试准确率,以及通过电压来测试IC芯片电磁兼容性,提高了IC芯片电磁兼容性的测试效率。

本发明的其他有益效果,将在具体实施方式中通过具体技术特征和技术方案的介绍来阐述,本领域技术人员通过这些技术特征和技术方案的介绍,应能理解所述技术特征和技术方案带来的有益技术效果。

附图说明

以下将参照附图对根据本发明的优选实施方式进行描述。图中:

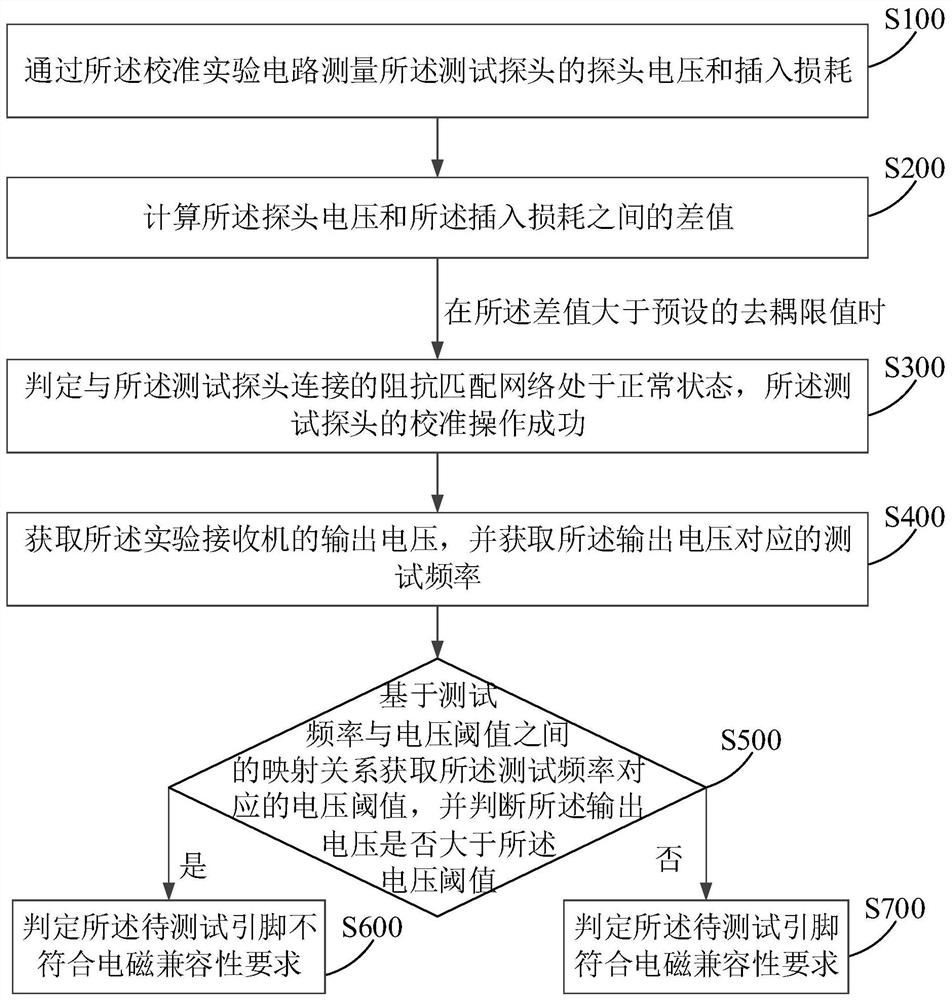

图1是本发明一实施例的IC芯片电磁兼容性测试方法流程框图。

图2本是发明实施例中测试装置、实验接收机和IC芯片之间的连接关系示意图;

图3A是本发明实施例中C1=6.8nF时,阻抗匹配网络中输入阻抗的变化示意图;

图3B是本发明实施例中C1=16.8nF时,阻抗匹配网络中输入阻抗的变化示意图;

图3C是本发明实施例中C1=4.6nF时,阻抗匹配网络中输入阻抗的变化示意图;

图3D是本发明实施例中C1=12.4nF时,阻抗匹配网络中输入阻抗的变化示意图;

图4A是本发明实施例中C1=6.8nF时,阻抗匹配网络中插入损耗的变化示意图;

图4B是本发明实施例中C1=16.8nF时,阻抗匹配网络中插入损耗的变化示意图;

图4C是本发明实施例中C1=4.6nF时,阻抗匹配网络中插入损耗的变化示意图;

图4D是本发明实施例中C1=12.4nF时,阻抗匹配网络中插入损耗的变化示意图;

图5A是本发明实施例中C1=6.8nF时,阻抗匹配网络中电压比值的变化示意图;

图5B是本发明实施例中C1=16.8nF时,阻抗匹配网络中电压比值的变化示意图;

图5C是本发明实施例中C1=4.6nF时,阻抗匹配网络中电压比值的变化示意图;

图5D是本发明实施例中C1=12.4nF时,阻抗匹配网络中电压比值的变化示意图;

图6是本发明实施例中测试探头和校准实验电路连接的一种示意图;

图7是本发明实施例中测试频率与去耦限值之间的一个对应关系图;

图8是本发明实施例中测量测试探头的探头电压的一种电路示意图;

图9是本发明实施例中测量测试探头的插入损耗的一种电路示意图;

图10是本发明IC芯片电磁兼容性测试系统的结构示意图。

具体实施方式

现结合附图,对本发明的较佳实施例作详细说明。需要说明的是,本发明中采用步骤编号(字母或数字编号)来指代某些具体的方法步骤,仅仅是出于描述方便和简洁的目的,而绝不是用字母或数字来限制这些方法步骤的顺序。本领域的技术人员能够明了,相关方法步骤的顺序,应由技术本身决定,不应因步骤编号的存在而被不适当地限制。

如图1所示,是本发明一实施例的IC芯片电磁兼容性测试方法流程框图。

步骤S100,通过所述校准实验电路测量所述测试探头的探头电压和插入损耗。

在本实施例中,采用测试装置测试IC芯片的电磁兼容性。测试装置包括测试探头和阻抗匹配网络;测试探头连接IC芯片的待测试引脚,阻抗匹配网络连接实验接收机,CI芯片中的其他I/O引脚按照规定连接负载。阻抗匹配网络中设置有16.8nF(纳法)电容。阻抗匹配网络的阻抗、连接IC芯片的信号线的阻抗和实验接收机的阻抗是相匹配的。具体地,在测试过程中,测试探头的探针是和IC芯片的待测试引脚连接的,IC芯片中每个引脚的测试方法都相同。具体地,参照图2,图2中的IC芯片就是待测试的IC芯片,测试探头并没有在图2中画出。由图2可知,阻抗匹配网络是由两个电阻R1、R2,和一个电容C1组成,其中,C1=16.8nF。探针针套通过插头连接器与阻抗匹配网络的PCB(Printed Circuit Board,印制线路板)板连接,即插头连接器焊接在阻抗匹配网络的PCB板上,测试探头安装在探针针套上。本实施例中所用的测试探头是用铜制成的,相对于其他材质,采用铜制成测试探头,能减少测试过程中的电流耗损和电磁干扰。本实施例通过探针针套可避免将测试探头焊接在阻抗匹配网络的PCB板上,通过探针针套来弥补阻抗匹配网络PCB板钻孔的直径差异,避免PCB板上的钻孔过小或者过大,无法将测试探头较好的固定在PCB板上,通过将探针针套来固定测试探头,避免测试探头发生倾斜,引导并固定测试探头。进一步地,本实施例通过探针针套,在更换测试探头时,不需要进行布线操作,提高了在维护测试装置时,更换测试探头的更换效率。进一步地,为了提高电磁兼容性测试的准确率,在安装测试探头时,要考虑测试探头的安装角度。测试探头可传输的连续电流取决于测试探头的大小,测试探头的弹簧力和测试探头所用的材料。

由图6可知,在校准测试探头过程中,测试探头与校准实验电路连接,具体地,测试探头通过第一插座与校准实验电路连接,该第一插座可为4mm(毫米)的同轴插座,也可以为其他类型的插座。校准实验电路通过第二插座和连接器连接射频(RF,Radio Frequency)发生器,该第二插座可为N型插座或者其他类型的插座。为了使连接器和插座可以成功连接,连接器的类型要和第二插座相同,如当第二插座为N型插座时,连接器也应该为N型连接器。具体地,校准实验电路PCB板上的输入端口连接射频发生器,输出端口连接到需要校准的测试探头,测试探头的输出端口连接到实验接收机。在本实施例中,校准实验电路和实验接收机的阻抗都为50Ω,即本实施例是在阻抗为50Ω的系统中测量测试探头的探头电压和插入损耗。

步骤S200,计算所述探头电压和所述插入损耗之间的差值,并在所述差值大于预设的去耦限值时,执行步骤S300。

步骤S300,判定与所述测试探头连接的阻抗匹配网络处于正常状态,所述测试探头的校准操作成功。

进一步地,所述IC芯片电磁兼容性测试方法包括以下步骤:

步骤S800,判定所述测试探头的校准操作失败,并提示用户更换所述阻抗匹配网络中元器件。

当测量得到测试探头的探头电压和插入损耗后,计算探头电压和插入损耗之间的差值,并判断差值是否大于预设的去耦限值。需要说明的是,在计算探头电压和插入损耗之间差值过程中,需要先将探头电压的单位转换成分贝,然后再计算探头电压和插入损耗之间的差值。该预设的去耦限值是在当前测试频率下的最小去耦限值。具体地,参照图7,图7是测试频率与去耦限值之间的一个对应关系图。由图7可知,不同的测试频率对应的去耦限值可能相同,也可能不相同。若确定计算所得的差值大于去耦限值,则判定与测试探头连接的阻抗匹配网络处于正常状态,测试探头的校准操作成功;若确定计算所得的差值小于或者等于去耦限值,判定测试探头的校准操作失败,并提示用户更换阻抗匹配网络中的元器件,具体地,可更换阻抗匹配网络中的电阻和/或电容,在更换阻抗匹配网络中的电阻和/或电容时,只能更换阻抗匹配网络中电阻和/或电容的生产厂家或者型号,不能更换电阻和/或电容的大小。

需要说明的是,计算所得的差值为“去耦”,去耦反映了与信号源相关的测量动态,即去耦与测试探头的品质特性、灵敏度和屏蔽特性有关。

进一步地,所述校准实验电路的输入端口与射频发生器连接,所述校准实验电路的输出端口与所述测试探头连接;在所述步骤S100中,所述通过所述校准实验电路测量所述测试探头的探头电压和插入损耗的步骤包括:

步骤f,当所述射频发生器与所述测试探头之间的跳线处于断开状态时,通过所述射频发生器在预设频率范围内进行扫频操作,以测量得到所述测试探头的探头电压。

步骤g,当所述射频发生器与所述测试探头之间的跳线处于连接状态时,通过所述射频发生器在预设频率范围内进行扫频操作,以测量得到所述测试探头的插入损耗。

具体地,校准实验电路的输入端口与射频发生器连接,校准实验电路的输出端口与测试探头连接。在测量测试探头的探头电压和插入损耗时,需要进行两次的测量,一次测量探头电压,一次测量插入损耗。具体地,在测量测试探头的探头电压时,射频发生器和测试探头之间的跳线处于断开状态,此时,通过射频发生器在预设频率范围内进行扫频操作,从而测量得到测试探头的探头电压。在本实施例中,不限制预设频率范围的大小,用户可根据具体需要设置预设频率的大小。扫频操作就是指信号在一个频段内,频率由高到低(或由低到高)连续变化的过程。具体地,参照图8,图8是本发明实施例中测量测试探头的探头电压的一种电路示意图。图8中的“1”和“2”表示开关,由图8可知,在测量探头电压时,跳线A是断开连接的。

当测量测试探头的插入损耗时,射频发生器与测试探头之间的跳线处于连接状态,即在射频发生器与测试探头之间的跳线处于连接状态时,通过射频发生器在预设频率范围内进行扫频操作,以测量得到测试探头的插入损耗。具体地,参照图9,图9是本发明实施例中测量测试探头的插入损耗的一种电路示意图。图9中的“1”和“2”表示开关,由图9可知,在测量插入损耗时,跳线A是处于连接状态的。需要说明的是通过插入耗损可以确定测试探头的测试灵敏度,插入耗损是一个负值,插入耗损的绝对值越小,对应的测试灵敏度越高。

本实施例在通过阻抗匹配网络进行IC芯片的电磁兼容性测量时,先校准阻抗匹配网络,以提高通过阻抗匹配网络进行IC芯片的电磁兼容性测量的准确率。

需要说明的,本实施例中的IC芯片电磁兼容性测试方法可用于测量不同IC芯片的电磁兼容性,从而比较不同IC芯片的电磁发射特性;且本发明实施例中通过阻抗匹配网络来实现电磁兼容性测试,而阻抗匹配网络是由电阻和电容组成,具有恒定的频率响应线性转换功能;通过插入耗损来校准测试探头,简化了测试探头的校准操作流程,从而实现了可以采用该测试装置重复测量不同IC芯片的电磁兼容性,即具有高可重复性测量IC芯片的EME(electromagnetic emission,电磁发射)性能的效果。

步骤S400,获取所述实验接收机的输出电压,并获取所述输出电压对应的测试频率。

在测试时,IC芯片作为信号发射器,生成测试信号,测试信号经过阻抗匹配网络到达实验接收机。获取实验接收机的输出电压,并获取输出电压对应的测试频率。在测试过程中,可采用不同的测试频率进行测试,以提高电磁兼容性测试的准确率。进一步地,本实施例中所选用的测试探头宽带要保证一定的高度,以准确快速捕捉电流波形,且要保证测试探头的测试精度,以满足不同测试领域的需求。

步骤S500,基于测试频率与电压阈值之间的映射关系获取所述测试频率对应的电压阈值,并判断所述输出电压是否大于所述电压阈值;若所述输出电压大于所述电压阈值,则执行步骤S600;若所述输出电压小于或者等于所述电压阈值,则执行步骤S700;

步骤S600,判定所述待测试引脚不符合电磁兼容性要求。

步骤S700,判定所述待测试引脚符合电磁兼容性要求。

当得到测试频率后,获取预先存储的测试频率与电压阈值之间的映射关系。测试频率和电压阈值之间的映射关系是预先设置好的,在该映射关系中,可以是一个测试频率对应一个电压阈值,也可以是多个测试频率对应一个电压阈值。因此,当得到测试频率,且获取到映射关系时,即可基于该映射关系获取测试频率对应的电压阈值。当得到电压阈值后,判断输出电压是否大于电压阈值。若输出电压大于电压阈值,则判定待测试引脚处于异常状态,即判定待测试引脚不符合电磁兼容性的要求;若输出电压小于或者等于电压阈值,则判定待测试引脚处于正常状态,即判定待测试引脚符合电磁兼容性的要求。需要说明的是,本实施例中的输出电压是一个射频电压,比正常的220V(伏)电压要高。

进一步地,IC芯片电磁兼容性测试方法还包括:

步骤a,计算所述阻抗匹配网络的输入阻抗、插入损耗和输出电压与输入电压之间的电压比值。

需要说明的是,在测试IC芯片电磁兼容性的测试过程中,为了提高电磁兼容性测试的准确性,要保证阻抗匹配网络的输入阻抗、插入损耗和电压比值满足阻抗匹配网络的特性要求,因此需要计算阻抗匹配网络的输入阻抗、插入损耗和电压比值,电压比值为阻抗匹配网络输出电压和输入电压之间的比值。插入损耗是指IC芯片(信号发生器)与实验接收机之间,插入电缆或元件产生的信号损耗,通常指衰减,插入损耗以接收信号电平的对应分贝(dB)来表示。

计算所述输入阻抗的计算公式为:

其中,Z

计算所述插入损耗IL

计算电压比值VR的计算公式为:

需要说明的是,在计算插入损耗和电压比值过程中,计算公式中都添加了“20log10”,从而使插入损耗和电压比值的单位为dB(decibel,分贝)。

步骤b,判断所述输入阻抗、插入耗损和电压比值是否符合对应的预设条件。

步骤c,若所述输入阻抗、插入损耗和电压比值均符合对应的预设条件,则判定当前的阻抗匹配网络符合阻抗匹配网络的特性。

步骤d,若所述输入阻抗、插入损耗和电压比值至少一个未符合对应的预设条件,则判定当前的阻抗匹配网络不符合阻抗匹配网络的特性,并提示用户更换所述阻抗匹配网络中元器件。

当计算得到阻抗匹配网络的输入阻抗、插入损耗和电压比值后,判断输入阻抗、插入损耗和电压比值是否符合对应的预设条件,需要说明的是,输入阻抗、插入耗损和电压比值都存在各自对应的预设条件,该预设条件由阻抗匹配网络的特性决定。具体地,在本实施例中,输入阻抗对应的预设条件是输入阻抗大小应为145Ω±20Ω;插入损耗对应的预设条件是插入损耗大小应为-11.75dB±2dB;电压比值对应的预设条件是电压比值大小应为-15.2dB±2dB。

若判定阻抗匹配网络的输入阻抗、插入损耗和电压比值均符合对应的预设条件,则判定当前的阻抗匹配网络符合阻抗匹配网络的特性;若判定阻抗匹配网络的输入阻抗、插入损耗和电压比值至少一个未符合对应的预设条件,则判定当前的阻抗匹配网络不符合阻抗匹配网络的特性,此时提示用户更换阻抗匹配网络中的元器件。具体地,可在阻抗匹配网络中设置一个LED(Light Emitting Diode,发光二极管)灯,通过该LED灯提示用户更换阻抗匹配网络中的元器件,如可控制该LED灯显示特定的颜色或者进入闪烁状态来提示用户更换阻抗匹配网络中的元器件。具体地,在更换阻抗匹配网络中的元器件时,可只更换R1、R2或者C1中的一个,或者更换R1、R2和C1中的多个,在更换过程中,要保证R1=120Ω,R2=50Ω,C1=16.8nF,但是可以更换电阻和电容对应的生产厂家和元器件型号。需要说明的是,阻抗匹配网络中各个元器件的大小是不可以改变,是由相关标准规定的。IC芯片与其他设备,如与测试装置之间连接所用的线缆作为辐射天线时,该辐射天线的阻抗为150Ω,此时,阻抗匹配网络的阻抗也应该为150Ω。

如当计算得到的阻抗匹配网络的输入阻抗大小在125Ω~165Ω(145Ω±20Ω)之间时,表明阻抗匹配网络的输入阻抗符合对应的预设条件;当计算得到的阻抗匹配网络的插入损耗大小在-13.75dB~-9.75dB范围内时,表明阻抗匹配网络的输入阻抗符合对应的预设条件;当计算得到的阻抗匹配网络的电压比值在-17.2dB~-13.2dB范围内时,表明该电压比值符合对应的预设条件。

在本实施例中,阻抗匹配网络的特性参数如下表所示:

需要说明的是,输入阻抗是指阻抗匹配网络生成的,要输入到实验接收机中的阻抗,在本实施例中,实验接收机自己的内部阻抗为50Ω,插入损耗为由测试装置、实验接收和IC芯片组成的输入阻抗和输出阻抗都为50Ω的系统。

具体地,参照图3A、图4A、图5A、图3B、图4B、图5B、图3C、图4C、图5C、图3D、图4D和图5D,图3A、图4A和图5A中是阻抗匹配网络内部串联6.8nF电容时,即C1=6.8nF所得的示意图;图3B、图4B和图5B中是阻抗匹配网络内部串联16.8nF电容时,即C1=16.8nF所得的示意图;图3C、图4C和图5C中是阻抗匹配网络内部串联4.6nF电容时,即C1=4.6nF所得的示意图;图3D、图4D和图5D中是阻抗匹配网络内部串联12.4nF电容时,即C1=12.4nF所得的示意图。在图3A、图3B、图3C和图3D中,横轴表示测试频率,单位为Hz,纵轴表示输入阻抗,单位为Ω;在图4A、图4B、图4C和图4D中,横轴表示测试频率,单位为Hz,纵轴表示插入损耗,单位为dB;在图5A、图5B、图5C和图5D中,横轴表示测试频率,单位为Hz,纵轴表示电压比值,单位为dB。

由图3A可知,C1=6.8nF时,阻抗匹配网络的输入阻抗的变化范围为140Ω—220Ω,由图3B可知,C1=16.8nF时,阻抗匹配网络的输入阻抗的变化范围为145Ω—160Ω,由图3C可知,C1=4.6nF时,阻抗匹配网络的输入阻抗的变化范围为140Ω—280Ω,由图3D可知,C1=12.4nF时,阻抗匹配网络的输入阻抗的变化范围为145Ω—170Ω,根据阻抗匹配网络特性要求,阻抗匹配网络对应的输入阻抗需满足145Ω±20Ω,故相对于6.8nF、4.6nF和12.4nF的电容,16.8nF的电容对应阻抗匹配网络的输入阻抗更准确,更能满足阻抗匹配网络的特性要求。

由图4A可知,C1=6.8nF时,阻抗匹配网络的插入损耗范围为-14dB—11.5dB,由图4B可知,C1=16.8nF时,阻抗匹配网络的插入损耗范围为-12.2dB—-11.7dB,由图4C可知,C1=4.6nF时,阻抗匹配网络的插入损耗范围为-21dB—-15dB,由图4D可知,C1=12.4nF时,阻抗匹配网络的插入损耗范围为-16.5dB—-15.3dB,根据阻抗匹配网络特性要求,阻抗匹配网络的插入损耗需满足-11.75dB±2dB,故相对于6.8nF、4.6nF和12.4nF的电容,16.8nF的电容对应阻抗匹配网络的插入损耗更小,更能满足阻抗匹配网络的特性要求。

由图5A可知,C1=6.8nF时,阻抗匹配网络的电压比值范围为-19bB—15dB,由图5B可知,C1=16.8nF时,阻抗匹配网络的电压比值范围为-16dB—-15.2dB,由图5C可知,C1=4.6nF时,阻抗匹配网络的电压比值范围为-16dB—-12.2dB,由图5D可知,C1=12.4nF时,阻抗匹配网络的电压比值范围为-12.6dB—-11.8dB,根据阻抗匹配网络特性要求,阻抗匹配网络的电压比值需满足-15.2dB±2dB,故相对于6.8nF、4.6nF和12.4nF的电容,16.8nF的电容对应阻抗匹配网络的电压比值更能满足阻抗匹配网络的特性要求。由此可知,本实施例中采用16.8nF电容的阻抗匹配网络来测量IC芯片的电磁兼容性,比采用6.8nF电容的阻抗匹配网络来测量IC芯片的电磁兼容性准确性更高。

需要特别强调的是,上述电容值的具体数值选取,不仅需要发明人具有远远超出本领域普通技术人员水平的理论基础,还需要根据预期目标设计结果,进行创造性尝试和选择,并辅以若干次艰辛试验,最终才能得到预期的目标结果。本申请技术方案最终确定的阻抗匹配网络中设置的电容值16.8nF,正是本申请多个发明人,首先根据远超常人的理论技术上确定了可能的数值范围,然后进行创造性尝试和选择,并辅以若干次艰辛试验,最终才能得到目标结果,而这个数值经过验证实现了最好的效果。这个数值的确定,本领域普通技术人员不付出创造性劳动永远无法获得。

需要说明的是,可以在步骤S300和步骤S400之间执行步骤a、步骤b、步骤c和步骤d,也可以再步骤S100之前执行步骤a、步骤b、步骤c和步骤d,或者根据需要确定何时执行步骤a、步骤b、步骤c和步骤d。本实施例不限制步骤a、步骤b、步骤c和步骤d执行顺序。

进一步地,为了提高通过测试探头测量IC芯片电磁兼容性的准确性,可以在不同的温度下测量测试探针,以获知测试探针随着温度变化的变化情况,以避免温度变化对测试探针测试准确度的影响。

本实施例先校准实验电路校准测试探头,再通过设置有16.8nF电容的阻抗匹配网络来连接实验接收机,然后通过测试探头连接IC芯片的待测试引脚,获取实验接收机的输出电压,并获取输出电压对应的测试频率;基于测试频率与电压阈值之间的映射关系获取测试频率对应的电压阈值,若输出电压大于电压阈值,则判定待测试引脚不符合电磁兼容性要求;若输出电压小于或者等于电压阈值,则判定待测试引脚符合电磁兼容性要求。实现了校准测试探头后,再通过测试探头来测试IC芯片的电磁兼容性,提高了IC芯片电磁兼容性的测试准确率,以及通过电压来测试IC芯片电磁兼容性,提高了IC芯片电磁兼容性的测试效率。

本发明还提供一种IC芯片电磁兼容性测试系统,参照图10,所述测试系统包括测试装置、校准实验电路和实验接收机,所述测试装置包括测试探头和阻抗匹配网络;所述测试探头连接校准实验电路,所述测试探头连接IC芯片的待测试引脚,所述阻抗匹配网络连接实验接收机,所述阻抗匹配网络中设置有16.8nF电容;

所述测试装置包括:

测量模块10,用于通过所述校准实验电路测量所述测试探头的探头电压和插入损耗;

计算模块20,用于计算所述探头电压和所述插入损耗之间的差值;

第一判断模块30,用于判断所述差值是否大于预设的去耦限值;

第一判定模块40,用于在所述第一判断模块的判断结果为是时,判定与所述测试探头连接的阻抗匹配网络处于正常状态,所述测试探头的校准操作成功;

获取模块50,用于获取所述实验接收机的输出电压,并获取所述输出电压对应的测试频率;基于测试频率与电压阈值之间的映射关系获取所述测试频率对应的电压阈值;

第二判断模块60,用于判断所述输出电压是否大于所述电压阈值;

第二判定模块70,用于在所述第二判断模块的判断结果为是时,判定所述待测试引脚不符合电磁兼容性要求;在所述第二判断模块的判断结果为否时,判定所述待测试引脚符合电磁兼容性要求。

需要说明的是,校准实验电路可以只在校准测试探头时,与测试装置连接,而实验接收机也可以只在测试IC芯片的电磁兼容性时,才与测试装置连接,即在测试IC芯片的电磁兼容性时,校准实验电路不与测试装置连接。

进一步地,所述测试探头安装在探针针套上,所述探针针套通过插头连接器与所述阻抗匹配网络的PCB板连接。

进一步地,所述第一判定模块40还用于在所述第一判断模块的判断结果为否时,判定所述测试探头的校准操作失败,并提示用户更换所述阻抗匹配网络中元器件。

进一步地,所述校准实验电路的输入端口与射频发生器连接,所述校准实验电路的输出端口与所述测试探头连接;所述测试装置还包括:

扫频模块,用于当所述射频发生器与所述测试探头之间的跳线处于断开状态时,通过所述射频发生器在预设频率范围内进行扫频操作,以测量得到所述测试探头的探头电压;当所述射频发生器与所述测试探头之间的跳线处于连接状态时,通过所述射频发生器在预设频率范围内进行扫频操作,以测量得到所述测试探头的插入损耗。

进一步地,所述测试装置还包括:

特性计算模块,用于计算所述阻抗匹配网络的输入阻抗、插入损耗和输出电压与输入电压之间的电压比值;

计算所述输入阻抗的计算公式为:

其中,Z

计算所述插入损耗IL

计算电压比值VR的计算公式为:

第三判断模块,用于判断所述输入阻抗、插入耗损和电压比值是否符合对应的预设条件;

第三判定模块,用于在所述第三判断模块的判断结果为是时,判定当前的阻抗匹配网络符合阻抗匹配网络的特性;在所述第三判断模块的判断结果为否时,判定当前的阻抗匹配网络不符合阻抗匹配网络的特性,并提示用户更换所述阻抗匹配网络中元器件。

进一步地,R1=120Ω,R2=50Ω,R

所述输入阻抗对应的预设条件是输入阻抗大小为145Ω±20Ω;

所述插入损耗对应的预设条件是插入损耗大小为-11.75dB±2dB;

所述电压比值对应的预设条件是电压比值大小为-15.2dB±2dB。

进一步地,本发明IC芯片电磁兼容性测试装置的具体实施方式与上述IC芯片电磁兼容性测试方法各实施例基本相同,在此不再重复赘述。

本发明还提出一种计算机可读存储介质,所述计算机可读存储介质上存储有检测程序,所述检测程序被处理器执行时实现如上所述IC芯片电磁兼容性测试方法的步骤。

本发明计算机可读存储介质的具体实施方式与上述IC芯片电磁兼容性测试方法各实施例基本相同,在此不再重复赘述。

本领域的技术人员能够理解的是,在不冲突的前提下,上述各优选方案可以自由地组合、叠加。

应当理解,上述的实施方式仅是示例性的,而非限制性的,在不偏离本发明的基本原理的情况下,本领域的技术人员可以针对上述细节做出的各种明显的或等同的修改或替换,都将包含于本发明的权利要求范围内。

- IC芯片电磁兼容性测试方法、装置和可读存储介质

- 浏览器兼容性测试方法、装置、系统及可读存储介质