存储器装置及其制造方法

文献发布时间:2023-06-19 09:36:59

技术领域

本发明是关于一种存储器装置及其制造方法,且特别适用于非易失性存储器,例如导电桥接随机存取存储器(conductive-bridging random access memory,CBRAM)。

背景技术

随着半导体装置尺寸的微缩,制造半导体装置的难度也大幅提升,半导体装置的制造工艺期间可能产生不想要的缺陷,这些缺陷可能会造成装置的效能降低或损坏。因此,必须持续改善半导体装置,以提升成品率并改善制造工艺宽裕度。

发明内容

根据本发明的一些实施例,提供存储器装置的制造方法。此方法包含形成第一电极;在第一电极上方形成电阻转态层(resistive switching layer);在电阻转态层上方形成介电层(dielectric layer);在介电层中形成第一开口,其中第一开口穿过介电层且露出(exposes)电阻转态层;在介电层中形成第一沟槽,其中第一沟槽位于第一开口正上方;以及在第一开口和第一沟槽中形成具有阶梯状的第二电极。

根据本发明的一些实施例,提供存储器装置。此存储器装置包含第一电极;电阻转态层,设置于第一电极上方;以及第二电极,设置于电阻转态层上方且具有阶梯状,其中第二电极的底表面小于电阻转态层的顶表面。

为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附图式作详细说明如下。

附图说明

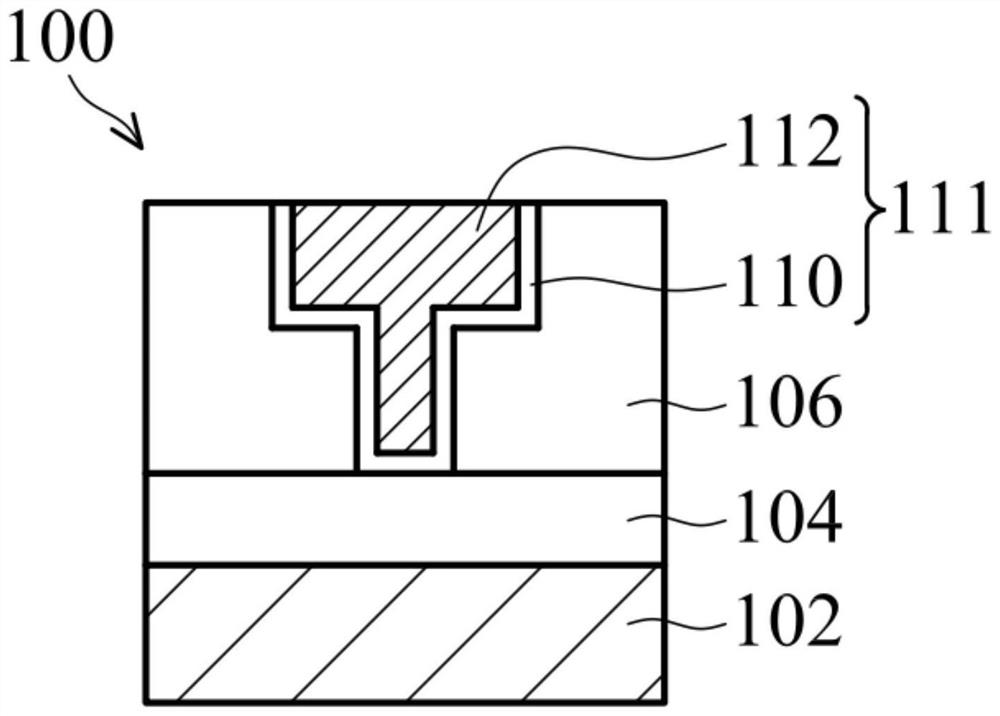

图1A~图1D是根据一些实施例绘示在制造存储器装置的各个阶段的剖面示意图;

图2A和图2B是根据一些实施例绘示存储器装置的剖面示意图;

图3是根据一些实施例绘示存储器装置的透视示意图;

图4A~图4D是根据一些实施例绘示在制造存储器装置的各个阶段的剖面示意图。

符号说明

100、300、400~存储器装置;112、112A、112B~块体层;

102~第一电极;114~漏极;

104~电阻转态层;116~源极;

106~介电层;118~栅极;

108、108A、108B~开口;120~接触件;

109、109A、109B~沟槽;122~导电丝;

110、110A、110B~阻挡层;400A~存储器单元区;

111、111A、111B~第二电极;400B~周边区。

具体实施方式

图1A~图1D是根据一些实施例绘示在制造存储器装置100的各个阶段的剖面示意图。在一些实施例中,如图1A所示,存储器装置100包含第一电极102。在一些实施例中,第一电极102的材料可以包含铜、银、类似的材料或前述的组合,且第一电极102可以包含单层结构或多层结构。

首先,如图1A所示,在第一电极102上依序形成电阻转态层104及介电层106。在一些实施例中,形成电阻转态层104及介电层106的方式例如包括物理气相沉积制造工艺、化学气相沉积制造工艺、原子层沉积制造工艺、蒸发、类似的制造工艺或前述的组合。在一些实施例中,电阻转态层104的厚度在约1纳米至约100纳米的范围,例如约5纳米至约15纳米。

在一些实施例中,电阻转态层104的材料包含氮化物、氮碳化物、类似的材料或前述的组合。举例来说,电阻转态层104的材料可以包含氮化硅、氮碳化硅、类似的材料或前述的组合。在一些实施例中,介电层106的材料包含氧化物、低介电常数介电材料、类似的材料或前述的组合。举例来说,介电层106的材料可以包含氧化硅、氮氧化硅、磷硅酸盐玻璃、硼硅酸盐玻璃、硼磷硅酸盐玻璃、未掺杂的硅酸盐玻璃、氟硅酸盐玻璃、类似的材料或前述的组合。

然后,如图1B所示,在介电层106上设置遮罩层(未绘示),接着使用上述遮罩层作为刻蚀遮罩进行刻蚀制造工艺,以在介电层106形成开口108。根据一些实施例,如图1B所示,开口108穿过介电层106且露出电阻转态层104。举例而言,遮罩层可以包含光刻胶,例如正型光刻胶或负型光刻胶。在一些实施例中,遮罩层可以包含硬遮罩,且可由氧化硅、氮化硅、氮氧化硅、碳化硅、氮碳化硅、类似的材料或前述的组合形成。遮罩层可以是单层或多层结构。遮罩层的形成可以包含沉积制造工艺、光刻制造工艺、其他适当的制造工艺或前述的组合。在一些实施例中,沉积制造工艺包含旋转涂布、化学气相沉积、原子层沉积、类似的制造工艺或前述的组合。举例来说,光刻制造工艺可以包含光刻胶涂布、软烘烤、掩膜对准、曝光、曝光后烘烤、显影、清洗、干燥(例如硬烘烤)、其他合适的制造工艺或前述的组合。

在一些实施例中,上述刻蚀制造工艺可以包含干式刻蚀制造工艺、湿法腐蚀制造工艺或前述的组合。举例来说,干式刻蚀制造工艺可以包含反应性离子刻蚀、感应耦合式等离子体刻蚀、中子束刻蚀、电子回旋共振式刻蚀、类似的刻蚀制造工艺或前述的组合。举例来说,湿法腐蚀制造工艺可以使用例如氢氟酸、氢氧化铵或任何合适的刻蚀剂。

然后,如图1C所示,移除介电层106的一部分,形成沟槽109,其中沟槽109位于开口108的正上方。沟槽109的形成方式类似于开口108的形成方式,故不再赘述。根据一些实施例,如图1C所示,且沟槽109的宽度大于开口108的宽度。换言之,开口108及沟槽109共同形成一阶梯状的开口。

值得一提的是,本实施例是先形成开口108后再于其上半部形成沟槽109以形成阶梯状的开口。但本发明不限于此,在另一实施例中,也可先形成沟槽109后再于其中形成开口108以形成阶梯状的开口。

接着,如图1D所示,在开口108和沟槽109中顺应性地形成阻挡层110。在一些实施例中,阻挡层110的形成方式包含物理气相沉积制造工艺、化学气相沉积制造工艺、原子层沉积制造工艺、蒸发、类似的制造工艺或前述的组合。在一些实施例中,阻挡层110的材料包含钽、氮化钽、类似的材料或前述的组合。

然后,在开口108和沟槽109的剩余部分形成块体层112。块体层112的材料可以包含铜、银、类似的材料或前述的组合。在一些实施例中,块体层112的形成方式包含物理气相沉积制造工艺、化学气相沉积制造工艺、原子层沉积制造工艺、蒸发、电镀、类似的制造工艺或前述的组合。

之后,进行一平坦化制造工艺,以形成第二电极111。在一些实施例中,前述平坦化制造工艺包括回刻蚀制造工艺、化学机械抛光制造工艺、类似的制造工艺或前述的组合。如图1D所示,第二电极111包括阻挡层110和块体层112,且阻挡层110位于块体层112与电阻转态层104之间且延伸至块体层112的侧壁。如图所示,第二电极111具有阶梯状侧壁。

相较于通过沉积及刻蚀制造工艺形成的电阻式存储器,容易受到刻蚀制造工艺的影响而使电极及电阻转换层受到损伤而言。本发明通过镶嵌制造工艺形成第二电极111,可避免第一电极102、电阻转换层104、及第二电极111受到损伤。此外,由于本发明是利用镶嵌制造工艺来形成第二电极111,因此亦可轻易地与周边区的制造工艺进行整合。

另外,本发明在使用铜、银等金属作为电极的电阻式存储器中,形成以氮化物、氮碳化物等材料做为电阻转态层。藉此,当在电阻转态层104中对应于电极处形成导电丝122时,电阻转态层104中未形成导电丝122的区域会同时具有阻挡层的特性,可防止形成导电丝122的铜、银等金属离子因扩散而损失,进而避免导电丝122被切断,提升存储器装置100的可靠度。

如图2A所示,当对存储器装置100施加正向电压时,第一电极102的金属材料氧化,金属离子扩散至电阻转态层104,并在电阻转态层104上方的电极还原,使电阻转态层104中形成金属离子构成的导电丝122,此时电阻转态层104转换为低电阻状态。反之,当对存储器装置100施加反向电压时,导电丝122中的金属离子会回到第一电极102中,导致导电丝122切断,使电阻转态层104转换为高电阻状态(如图2B所示)。存储器装置100通过上述方式转换电阻值以进行资料的储存或读取,达到储存功能。

图3是根据一些实施例绘示1T1R(One-Transistor-1-Resistor)的存储器装置300的透视示意图。如图3所示,存储器装置300包含第一电极102、电阻转态层104、第二电极111、漏极114、源极116和栅极118,且第一电极102经由接触件120与漏极114电性连接。在一些实施例中,漏极114、源极116、栅极118和接触件120可以各自独立地包含导电材料,例如掺杂的多晶硅、金属、类似的材料或前述的组合。在本实施例中,第一电极102、电阻转态层104和第二电极111形成一电阻(Resistor)器件,而漏极114、源极116和栅极118形成用以切换电阻阻值的晶体管(Transistor)器件。

图4A~图4D是根据一些实施例绘示在制造存储器装置400的各个阶段的剖面示意图。图4A~图4D与图1A~图1D以相同符号描述相同器件,并且这些器件的形成方法和材料如前所述,故不再赘述。图4A~图4D的实施例说明通过镶嵌制造工艺整合存储器单元区和周边区的形成。

在一些实施例中,如图4A所示,存储器装置400包含存储器单元区400A和周边区400B。如图所示,存储器装置400包含第一电极102、电阻转态层104及介电层106。第一电极102、电阻转态层104和介电层106的材料和形成方式的范例如前所述,故不再赘述。

然后,在介电层106上设置遮罩层(未绘示),接着使用上述遮罩层作为刻蚀遮罩进行刻蚀制造工艺,以在介电层106形成位于存储器单元区400A的开口108A和位于周边区400B的开口108B。开口108A和开口108B的形成方式的范例如前所述,故不再赘述。

然后,如图4B所示,在介电层106上设置遮罩层(未绘示),接着使用上述遮罩层作为刻蚀遮罩进行刻蚀制造工艺,以刻蚀开口108B露出的电阻转态层104的一部分,使开口108B穿过电阻转态层104并露出第一电极102。

然后,如图4C所示,移除介电层106的一部分,形成沟槽109A和109B,其中沟槽109A位于开口108A的正上方,且沟槽109B位于开口108B的正上方。沟槽109A和109B的形成方式类似于开口108A和开口108B的形成方式,故不再赘述。本实施例是先形成开口108A和108B后再于其上半部分别形成沟槽109A和109B以形成阶梯状的开口。但本发明不限于此,在另一实施例中,也可先形成沟槽109A和109B后再于其中形成开口108A和108B以形成阶梯状的开口。

接着,如图4D所示,在开口108A、108B和沟槽109A、109B中顺应性地形成阻挡层110A和110B。然后,在开口108A、108B和沟槽109A、109B的剩余部分分别形成块体层112A和112B。阻挡层110A、110B和块体层112A、112B的材料和形成方式的范例如前所述,故不再赘述。

之后,进行一平坦化制造工艺,以形成第二电极111A和111B。在一些实施例中,前述平坦化制造工艺包括回刻蚀制造工艺、化学机械抛光制造工艺、类似的制造工艺或前述的组合。如图4D所示,第二电极111A包括阻挡层110A和块体层112A,且阻挡层110A位于块体层112A与电阻转态层104A之间且延伸至块体层112A的侧壁。如图4D所示,第二电极111B包括阻挡层110B和块体层112B,且阻挡层110B位于块体层112B与电阻转态层104B之间且延伸至块体层112B的侧壁。由于第二电极111A和111B同时形成,第二电极111A和111B包含相同的材料。

在上述实施例中,本发明利用镶嵌制造工艺形成存储器单元区400A的第二电极111B和周边区400B的第二电极111B,可轻易地整合存储器单元区400A和周边区400B的制造工艺,减少制造工艺步骤,提升存储器装置400的成品率。

综上所述,本发明通过形成以氮化物、氮碳化物、等类似的材料做为电阻转态层的电阻式存储器,可以使形成导电丝的金属离子不易扩散,避免形成于其中的导电丝因扩散而切断,进而提升存储器装置的可靠度。此外,本发明通过镶嵌制造工艺形成电极,可避免现有技术中使用刻蚀制造工艺形成电极而造成的损伤,可改善存储器装置的可靠度,更可轻易地与周边区的制造工艺进行整合。

虽然本发明实施例已以多个实施例描述如上,但这些实施例并非用于限定本发明实施例。本发明所属技术领域中具有通常知识者应可理解,他们能以本发明实施例为基础,做各式各样的改变、取代和替换,以达到与在此描述的多个实施例相同的目的及/或优点。本发明所属技术领域中技术人员也可理解,此类修改或设计并未悖离本发明实施例的精神和范围。因此,本发明的保护范围当视权利要求所界定者为准。

- 存储器阵列、存储器阵列的制造方法、存储器阵列片材、存储器阵列片材的制造方法及无线通信装置

- 强电介质膜的形成方法、强电介质存储器、强电介质存储器的制造方法、半导体装置及半导体装置制造方法