用于将设计与工艺协同优化的方法和设备以及存储介质

文献发布时间:2023-06-19 09:41:38

技术领域

本公开的实施例一般地涉及半导体技术领域,并且更具体地涉及用于将设计与工艺协同优化的方法和设备以及计算机可读存储介质。

背景技术

当针对一个技术节点进行研发时,要选择的工艺方案和设计方案是相关联的。如果针对设计方案没有设置限制,则有效的工艺方案的实现难度较大。另一方面,如果为了使工艺方案容易实现而针对设计方案设置较多的限制,则很难满足设计方案的规则要求。已提出工艺和设计协同优化(DTCO)的方案,用于将工艺方案和设计方案彼此协作以满足新技术节点的器件的要求。

在DTCO中,工艺工程师从工艺角度出发,制定工艺方案,并且将工艺方案提供给设计工程师。设计工程师从设计角度出发,根据工艺方案和器件性能的要求,制定设计方案,并且与工艺工程师协同工作,保证在制定工艺方案时将设计方案的要求考虑在内,并且优化工艺方案和设计方案。通过设计方案和工艺方案的协同优化,可以平衡器件的可制造性和性能的要求。

DTCO可以减少流程开发时间,缩短先进工艺产品的上市时间,并且降低成本。期望提供DTCO的改进方案,以进一步缩短产品的上市时间。

发明内容

本公开的实施例提供了用于将设计与工艺协同优化的方法和设备以及计算机可读存储介质,其能够进一步缩短产品的上市时间并且降低生产成本。

在第一方面,提供了一种用于将设计与工艺协同优化的方法。该方法包括:针对技术节点,生成工艺方案;基于所述工艺方案,生成设计方案;以及基于所述设计方案来更改所述工艺方案,以用于生成优化方案,其中生成工艺方案包括基于与所述工艺方案的良率相关联的第一良率信息来生成所述工艺方案,以及/或者生成设计方案包括基于与所述设计方案的良率相关联的第二良率信息来生成所述设计方案。

在一些实施例中,生成工艺方案包括:基于良率模型来生成良率估计信息,所述良率模型包括多个工艺方案和与所述多个工艺方案相关联的良率数据;以及基于所述良率估计信息来生成所述工艺方案。

在一些实施例中,生成设计方案包括:通过高良率设计套件来生成良率预测信息,所述高良率设计套件包括设计规则分析工具、关键图案分析工具、坏点分析工具、可靠性分析工具中的至少一个工具,并且被包含在单独的电子设计自动化工具中;以及基于所述良率预测信息来生成所述设计方案。

在一些实施例中,生成设计方案包括:生成关于所述设计方案中包括的设计结构的测试结构;基于所述测试结构,生成关于所述设计结构的良率评价信息;以及基于所述良率评价信息来生成所述设计方案。

在一些实施例中,基于所述设计方案来更改所述工艺方案包括:基于所述良率评价信息来更新良率模型,所述良率模型包括多个工艺方案和与所述多个工艺方案相关联的良率数据;以及基于更新后的良率模型来确定所述工艺方案。

在一些实施例中,生成优化方案包括:基于确定的所述工艺方案来确定所述设计方案。

在一些实施例中,生成工艺方案包括:通过良率模型和坏点模拟来生成层工艺良率估计信息,所述良率模型包括多个工艺方案和相关联的良率数据,所述坏点模拟从与工艺方案相对应的器件架构获得;以及基于所述层工艺良率估计信息来生成所述工艺方案。

在一些实施例中,生成针对所述设计结构的良率评价信息包括:针对所述测试结构进行硅验证和良率分析,以生成所述良率评价信息;或者通过模拟工具针对所述测试结构进行模拟,以生成所述良率评价信息。。

在第二方面,提供了一种电子设备。该电子设备包括:处理单元;存储器,耦合至所述处理单元并且包括存储于其上的程序,所述程序在由所述处理单元执行时使所述电子设备执行如上所述的方法。

在第三方面,提供了一种计算机可读存储介质。该计算机可读存储介质上存储有机器可执行指令,当所述机器可执行指令在被至少一个处理器执行时,使得所述至少一个处理器实现如上所述的方法。

根据本公开的实施例,在用于将设计与工艺协同优化的方法中,基于与其良率相关联的良率信息来制定和生成工艺方案和/或设计方案。以此方式,能够避免良率风险,进一步缩短产品的上市时间,并且降低生产成本。

附图说明

通过结合附图对本公开示例性实施例进行更详细的描述,本公开的上述以及其他目的、特征和优势将变得更加明显。在本公开的示例性实施例中,相同的参考标号通常代表相同部件。在附图中:

图1是示出工艺和设计协同优化(DTCO)流程的示意图;

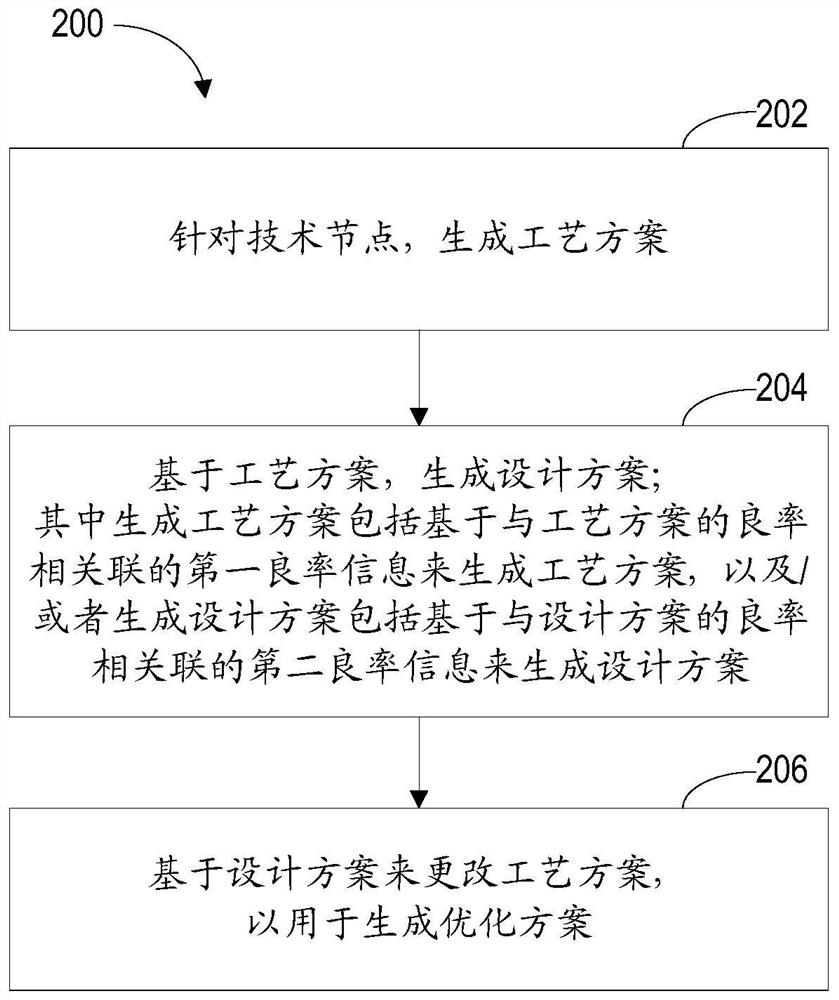

图2是示出根据本公开的实施例的用于将设计与工艺协同优化的方法的流程图;

图3是示出根据本公开的实施例的用于将设计与工艺协同优化的流程的示意图;

图4是示出根据本公开的实施例的用于将设计与工艺协同优化的流程的示意图;以及

图5是示出用于实施本公开的实施例的电子设备的示意性框图。

具体实施方式

下面将参照附图更详细地描述本公开的优选实施例。虽然附图中示出了本公开的优选实施例,然而应该理解,本公开可以以各种形式实现而不应被这里阐述的实施例限制。相反,提供这些实施例是为了使本公开更加透彻和完整,并且能够将本公开的范围完整地传达给本领域的技术人员。

在本文中使用的术语“包括”及其变形表示开放性包括,即“包括但不限于”。除非特别申明,术语“或”表示“和/或”。术语“基于”表示“至少部分地基于”。术语“一个示例实施例”和“一个实施例”表示“至少一个示例实施例”。术语“另一实施例”表示“至少一个另外的实施例”。术语“第一”、“第二”等等可以指代不同的或相同的对象。下文还可能包括其他明确的和隐含的定义。

图1是示出工艺和设计协同优化(Design Technology Co-Optimization,简称DTCO)流程的示意图。

参考图1,在工艺开发阶段,基于TCAD技术、工艺技术、微缩增效FEOL(前道工艺,Front end of line)/MEOL(中端工艺,mid-end-of-the-line)/BEOL(后端工艺,back-end-of-the-line)堆叠、器件架构、新器件/材料开发技术等中的任意已知技术来生成工艺方案。

在晶圆上执行制造过程之前,使用模拟技术开始探索。在设计实施阶段,基于电路寄生/SPICE模型/设计规则、布局和布线工具、多重图案化工具等中的任意已知技术来生成关键工艺设计包(PDK)数据,以启动IC设计的早期试验。

然后,在设计开发阶段,基于IC设计、宏设计、布局提取、性能提升等中的至少一项,评估功率、性能、面积、成本(PPAC)等,以生成设计方案。PPAC是对功率、性能、面积和成本的综合评估。目前半导体技术节点的解决方案依赖于PPAC的优化,而且工艺流程是基于DTCO流程。

随后,在设计开发阶段中生成的设计方案可以被反馈到工艺开发阶段和/或设计实施阶段,以更改工艺方案和/或设计参数。以此方式,执行循环,获得优化方案。DTCO能够降低在先进工艺节点的开发时间和成本。

在这种传统方案中,DTCO没有将诸如良率的生产问题考虑在评估循环中。实际上,产品良率会影响成本。然而,在传统DTCO中,在通常的成本计算中没有计入产品良率。另外,产品良率会影响产量,从而会影响产品的上市时间。

至少为了解决上述问题,本公开的实施例提供了用于将设计与工艺协同优化的改进方案,其中在将设计与工艺协同优化的流程中基于与良率相关联的良率信息来生成工艺方案和/或设计方案。根据本公开的实施例,基于良率的流程可以是DTCO的一个新的子流程。与设计方案中的设计结构相对应的良率评价信息可以是基于良率的流程的重要指标,该良率评价信息可以用于更新设计结构,或者可以用于更新工艺方案。根据本公开的实施例,可以扩展DTCO流程,使之更加完整。新扩展的DTCO流程可以被称为设计-工艺-良率协同优化(DTMCO)流程。这样,在新的DTMCO流程中,新的指标集是功率、性能、面积、成本和良率(PPACY)。以此方式,通过DTMCO流程和PPACY指标集可以避免良率风险,计算出更多的实际成本,并且揭示产品上市时间的重要问题,从而进一步缩短产品的上市时间。

下文中将结合附图参考各种实施例来详细描述本公开的各种示例实施例。

图2是示出根据本公开的实施例的用于将设计与工艺协同优化的方法200的流程图。

在框202,针对技术节点,生成工艺方案。

在一些实施例中,针对半导体技术节点,生成光刻工艺方案。在一些实施例中,针对半导体技术节点,生成层工艺方案。

在框204,基于所生成的工艺方案,生成设计方案。生成工艺方案包括基于与工艺方案的良率相关联的第一良率信息来生成工艺方案。附加地或备选地,生成设计方案包括基于与设计方案的良率相关联的第二良率信息来生成设计方案。在一些实施例中,根据第一良率信息的工艺方案可以具有对应的良率。在一些实施例中,根据第二良率信息的设计方案可以具有对应的良率。

在一些实施例中,基于工艺方案来生成结构图案设计方案。在一些实施例中,基于工艺方案来生成测试结构设计方案。

在一些实施例中,基于第一良率信息来生成工艺方案。这样,在制定工艺方案时考虑良率因素,从而获得经过良率优化的工艺方案。以此方式,可以将考虑到良率因素的限制信息施加到随后设计方案的制定之中,并且避免低良率的风险。

在一些实施例中,基于良率模型来生成良率估计信息,以及基于良率估计信息来生成工艺方案。良率模型包括多个工艺方案和与该多个工艺方案相关联的良率数据,其中多个工艺方案是指已制定的工艺方案,并且良率数据是指与多个工艺方案相关联的良率信息。这样,基于良率模型中包括的已有数据,初步地制定预期具有高良率的工艺方案。

在一些实施例中,基于第二良率信息来生成设计方案。这样,在制定设计方案时考虑良率因素,从而获得经过良率优化的设计方案。以此方式,可以将考虑到良率因素的评估信息反馈到随后工艺方案的更改或确定之中,并且避免低良率的风险。

在一些实施例中,通过高良率设计套件来生成良率预测信息,以及基于良率预测信息来生成设计方案。高良率设计套件包括与高良率设计(DFY)相关联的各种已知工具的集合。良率预测信息可以用作在生成设计方案中包括的设计结构时考虑的重要参数。

需要说明的是,所说的高良率设计,是指根据过往经验来看良率大于一预设值的产品所对应的设计。

在一些实施例中,生成关于设计方案中包括的设计结构的测试结构,基于测试结构来生成针对设计结构的良率评价信息,以及基于良率评价信息来生成设计方案。良率评价信息可以用于更新和优化设计结构,以生成考虑到良率因素的设计方案。

这样,基于通过高良率设计套件模拟得出的良率预测信息和/或通过测试结构获得的良率评价信息,初步地制定预期具有高良率的设计方案。在一些实施例中,基于良率预测信息和良率评价信息两者来生成设计方案。以此方式,可以在设计方案的制定之中充分地并且有效地考虑良率因素,从而获得经过良率优化的设计方案。

在一些实施例中,设计方案的制定或生成可以包括设计实施阶段和设计开发阶段。在一些实施例中,在设计实施阶段,通过高良率设计套件生成良率预测信息。在一些实施例中,在设计开发阶段,通过测试结构生成良率评价信息。

在一些实施例中,基于第一良率信息来生成工艺方案,以及基于该工艺方案和第二良率信息来生成设计方案。这样,在制定工艺方案时以及在制定设计方案时均考虑良率因素。以此方式,在将设计与工艺协同优化的整个流程中获得经过良率优化的工艺方案和经过良率优化的设计方案,从而有效地避免低良率的风险。

在框206,基于设计方案来更改工艺方案,以用于生成优化方案。

在一些实施例中,基于从设计方案中获得的测试结果来更改工艺方案,以用于生成优化方案。在一些实施例中,基于从设计方案中获得的良率评价信息来更改工艺方案,以用于生成优化方案。在一些实施例中,基于良率评价信息来更新良率模型,以及基于更新后的良率模型来确定工艺方案,其中良率模型包括多个工艺方案和相关联的良率数据。在一些实施例中,基于更新后的良率模型针对工艺方案定义风险指标。

在一些实施例中,经更改的工艺方案被用作优化方案。在其他实施例中,基于更改的工艺方案来再次确定设计方案,以作为优化方案。在其他实施例中,更改的工艺方案和更改的设计方案用作优化方案提供给对应的用户。在其他实施例中,针对多个优化方案定义风险指标,以提供给对应的用户做决策。

在一些实施例中,可以重复上述循环来多次更改工艺方案,从而生成多次优化的方案。在每次循环中,基于良率因素来确定和生成工艺方案和设计方案中的至少一个。

根据本公开的实施例提供了基于良率来将设计与工艺协同优化的方法,其中良率是在确定工艺方案和/或设计方案时考虑的重要参数。以此方式,将设计与工艺协同优化的方法能够呈现影响产品成本和产量的良率的优化。因此,根据本公开的实施例的改进方案能够避免良率风险,进一步缩短产品的上市时间,并且降低生产成本。

图3是示出根据本公开的实施例的用于将设计与工艺协同优化的流程的示意图。如图3所示的流程是基于良率的DTCO流程,其中通过良率指标考虑制造能力。如图3所示的流程是如图2所示的方法200的一个示例。然而,如图2所示的方法200不限于图3的示例。

工艺方案的制定和生成可以包括工艺开发阶段。工艺开发阶段可以包括用于良率评价的制造流程,如图3所示。在工艺开发阶段中,首先采用常规工艺开发循环。该工艺开发循环可以包括微缩增效MEOL/BEOL堆叠、器件架构和工艺模拟的循环。这些是本领域已知技术,在此省略其详细描述。此外,通过已知技术可以从器件架构获得坏点预测。

在一些实施例中,基于该坏点预测来确定良率估计信息,并且将良率估计信息反馈到工艺开发循环。在一些实施例中,基于良率模型来确定良率估计信息,该良率模型是通过已有数据利用已知技术建立的模型。这样,生成的工艺方案考虑了良率和制造因素。

设计方案的制定和生成可以包括设计实施阶段和设计开发阶段。在设计方案的制定和生成中,首先进入设计实施阶段,在一些实施例中,在设计实施阶段中采用高良率设计(DFY)设计套件。DFY设计套件可以包括一套软件工具、规则、方法和行会。例如,DFY设计套件可以包括友善制造设计(DFM)/可测试设计(DFT)/高良率设计(DFY)规则、单层和多层的关键图案、缺陷统计预测、良率分割条件、快速良率验证方法等中的至少一项。这些是本领域已知技术并且利用各种已知工具,在此省略其详细描述。DFY设计套件是针对设计实施阶段的整合工具,可以向设计工程师提供失效、缺陷预测和良率预测信息。随后,在设计方案的制定和生成中,进入设计开发阶段。

在设计开发阶段中,基于在工艺开发阶段生成的工艺方案和在设计实施阶段生成的早期设计试验或良率预测信息,生成设计方案。设计开发阶段可以包括用于测试质量控制/良率的设计流程,如图3所示。该设计流程包括测试结构和设计、快速测试和表征、硅验证和良率分析。这些是本领域已知技术,在此省略其详细描述。

在一些实施例中,通过该设计流程生成良率评价信息。在一些实施例中,可以生成功率、性能、面积、成本和良率(PPACY)的评价。PPAC(功率、性能、面积和成本)是传统DTCO的关键综合指标。在这个设计流程中,新的指标集被扩展成PPACY。

在该设计流程中,利用测试结构来进行实测和分析评估。在该设计流程中,生成各种测试结构,并且基于对应的测试结构来生成功率、性能、面积、成本或良率评价信息。由于这样的测试结构一般而言都不会太复杂,这个设计流程执行起来都相对简化并且容易分析。传统的DTCO是通过实际复杂的整体逻辑设计来评估,每个阶段会花费比较多时间。以此方式,该设计流程被简化以评估PPACY的测试设计或质量控制设计基础,与传统的DTCO相比速度更快。

在一些实施例中,该设计流程包括硅验证和良率分析,以用于生成PPACY评价。在其他实施例中,该设计流程包括利用模拟方法通过模拟工具/数据来生成PPACY评价。

从设计开发阶段生成的良率评价信息作为良率验证和估计、良率损害反馈和预测等而被反馈到工艺开发阶段,以更新良率模型。基于更新后的良率模型生成的良率估计信息进而被反馈到工艺开发循环,以更改工艺方案。通过执行一次或多次这样的循环,生成优化的方案。

根据本公开的实施例的基于良率估计信息、良率预测信息和/或良率评价信息来将设计与工艺协同优化的流程中,通过从工艺开发阶段到设计实施阶段和设计开发阶段的正向流程,能够建立快速良率测试和验证平台,加速良率的提升,并且针对生产建立有效的良率诊断和监控系统。另外,通过从设计开发阶段到工艺开发阶段的反馈流程,为了满足PPACY目标的工艺方案更改提供物理基础。以此方式,能够避免优化方案的良率风险,缩短通过优化方案制造的产品的上市时间,并且降低生产成本。

上面描述的基于良率的用于将设计与工艺协同优化的方法可以被实现到传统的DTCO流程中,使之更加完整。新的DTCO流程可以被称为基于制造或良率的DTCO流程或DTMCO流程。下文中将对此进行详细描述。

图4是示出根据本公开的实施例的用于将设计与工艺协同优化的流程的示意图。如图4所示的流程可以被称为基于制造或良率的DTCO流程或DTMCO流程。如图4所示的流程是如图2所示的方法200的一个示例。然而,如图2所示的方法200不限于图4的示例。

如图4所示的流程与如图1所示的流程的不同点在于,图4的工艺开发阶段可以包括通过坏点模拟和良率模型的层工艺良率估计信息,或者图4的设计实施阶段可以包括利用DFM/DFT/DFY设计套件,或者图4的设计开发阶段可以包括评估PPACY。也就是说,如图4所示的流程可以包括各个阶段中的与良率相关联的附加元素中的至少一个。DTMCO流程中的每个新附加元素都不是必要的。如果采用这些元素中的任何一个,就等效地采用基于良率的DTCO流程或DTMCO流程。

在一些实施例中,在工艺开发阶段,通过坏点模拟和良率模型来获得层工艺良率估计信息。坏点模拟可以采用任何已知的模拟技术。另外,良率模型是通过利用先前节点的大数据通过机器学习建立的良率模型。在一些实施例中,基于层工艺良率估计信息来生成工艺方案。在一些实施例中,进一步基于已知的TCAD技术、工艺技术、微缩增效FEOL/MEOL/BEOL堆叠、器件架构、新器件和材料开发技术中的至少一项,生成工艺方案。这样,在基于良率的DTCO流程或DTMCO流程的工艺开发阶段,将良率因素考虑到工艺方案的制定和生成之中。

在一些实施例中,在设计实施阶段,利用DFM/DFT/DFY设计套件,以提供良率预测信息。DFM、DFT、DFY中的每个技术是本领域已知的技术。在一些实施例中,进一步基于已知的电路寄生/SPICE模型/设计规则、布局和布线工具、多重图案化工具中的至少一项,生成PDK以获得针对设计的初步试验。在本实施例中,该设计套件被配置为一组可互相衔接的工具模块,并且可以将设计规则分析工具、关键图案或坏点分析工具、可靠性分析工具等综合在一起来提供更多的良率预测信息。该设计套件需要的功能就会有EDA软件工具的需求。通过将零散的工具整合成一个流畅可衔接的套件,可以形成一种新的软件EDA。设计套件可以被包括在单独的EDA工具中。

在一些实施例中,在设计开发阶段,可以基于工艺方案和良率预测信息,通过设计各种测试结构,评估PPACY,以用于生成设计方案。PPACY包括良率评价信息。在一些实施例中,进一步基于IC设计、宏设计、布局提取和性能提升,生成设计方案。在DTMCO流程中,最重要的评估参数被扩展为PPACY(功率、性能、面积、成本和良率)。

通过设计实施阶段和设计开发阶段,生成工艺方案。在设计开发阶段中生成的PPACY评价可以被反馈到工艺开发阶段和/或设计实施阶段,以更新良率模型和/或良率设计。这样,通过更改的工艺方案和/或良率设计,可以进一步更改设计方案。以此方式,通过将良率考虑到DTCO流程中,通过避免良率风险来获得针对产品的优化方案。

在基于良率的DTCO流程或DTMCO流程中,可以提出很多种设计架构、制程方式和效能分析,然后归结出非常多项可参考的方案。然后可以基于PPACY从这些方案中锁定最有竞争力的方案。由于多考虑了一项良率的因素,可能会选出与传统DTCO不同的最佳方案。由于传统DTCO中的基于PPAC的方案忽略了良率风险的因素,对制造端来说很有可能会存在很大的成本黑洞。相比之下,根据本公开的实施例,由于考虑了良率的因素,可以避免良率风险。以此方式,根据本公开的实施例的改进方案能够缩短产品的上市时间,并且降低制造成本。

图5是示出用于实施本公开的实施例的电子设备500的示意性框图。如图5所示,设备500包括中央处理单元(CPU)501,其可以根据存储在只读存储器(ROM)502中的计算机程序指令或者从存储单元508加载到随机访问存储器(RAM)503中的计算机程序指令,来执行各种适当的动作和处理。在RAM 503中,还可存储有电子设备500操作所需的各种程序和数据。CPU 501、ROM 502以及RAM 503通过总线504彼此相连。输入/输出(I/O)接口505也连接至总线504。

设备500中的多个部件连接至I/O接口505,包括:输入单元506,例如键盘、鼠标等;输出单元507,例如各种类型的显示器、扬声器等;存储单元508,例如磁盘、光盘等;以及通信单元509,例如网卡、调制解调器、无线通信收发机等。通信单元509允许设备500通过诸如因特网的计算机网络和/或各种电信网络与其他设备交换信息/数据。

上文所描述的各个过程和处理,例如方法200,可以由处理单元501执行。例如,在一些实施例中,方法200可以被实现为计算机软件程序,其被有形地包含于机器可读介质,例如存储单元508。在一些实施例中,计算机程序的部分或者全部可以经由ROM 502和/或通信单元509而被载入和/或安装到设备500上。当计算机程序被加载到RAM 503并由CPU 501执行时,可以执行上文描述的方法200中的一个或多个步骤。

根据本公开的实施例的方案可以是方法、装置、系统和/或计算机程序产品。计算机程序产品可以包括计算机可读存储介质,其上载有用于执行本公开的各个方面的计算机可读程序指令。计算机可读存储介质可以是可以保持和存储由指令执行设备使用的指令的有形设备。计算机可读程序指令可以从计算机可读存储介质下载到各个计算/处理设备,或者通过网络、例如因特网、局域网、广域网和/或无线网下载到外部计算机或外部存储设备。

以上已经描述了本公开的各实施例,上述说明是示例性的,并非穷尽性的,并且也不限于所披露的各实施例。在不偏离所说明的各实施例的范围和精神的情况下,对于本技术领域的普通技术人员来说许多修改和变更都是显而易见的。本文中所用术语的选择,旨在最好地解释各实施例的原理、实际应用或对市场中的技术改进,或者使本技术领域的其它普通技术人员能理解本文披露的各实施例。

- 用于将设计与工艺协同优化的方法和设备以及存储介质

- 一种车辆段工艺设计方法、系统、计算机设备及存储介质