晶片封装体及其制造方法

文献发布时间:2023-06-19 09:46:20

技术领域

本发明关于一种晶片封装体及一种晶片封装体的制造方法。

背景技术

传统的晶片封装体将多个晶片相邻放置,通过打线接合方式电性连接至印刷电路板(PCB)的同一侧,而印刷电路板的另一侧再通过导电结构(如锡球)与外部元件连接。然而,当多个晶片要整合至同一个封装体中时,则会使晶片封装体的面积大幅增加,不利于微小化设计。此外,打线接合的封装方式可靠度较低,同时也需占据封装体的体积,如打线顶部的高度。

发明内容

本发明的一技术态样为一种晶片封装体。

根据本发明一实施方式,一种晶片封装体包括第一晶片、第二晶片、封装材料以及重布线层。第一晶片具有第一导电垫。第二晶片设置在第一晶片上,且具有第二导电垫。封装材料覆盖第一晶片与第二晶片,且具有上部、下部与邻接上部与下部的倾斜部。上部位于第二晶片上,下部位于第一晶片上。重布线层沿上部、倾斜部与下部设置,且电性连接第一导电垫与第二导电垫。

在本发明一实施方式中,封装材料的下部与上部分别具有第一通孔与第二通孔,且第一导电垫与第二导电垫分别位在第一通孔与第二通孔中。

在本发明一实施方式中,封装材料的下部的上表面低于上部的上表面。

在本发明一实施方式中,封装材料的倾斜部与下部之间夹钝角。

在本发明一实施方式中,晶片封装体还包括贴合胶,设置于第一晶片第二晶片之间。

在本发明一实施方式中,晶片封装体还包括钝化层,覆盖重布线层及封装材料。

在本发明一实施方式中,钝化层与封装材料由不同材料制造。

在本发明一实施方式中,钝化层包括开口,晶片封装体还包括导电结构,导电结构位于开口中的重布线层上。

本发明的另一技术态样为一种晶片封装体的制造方法。

根据本发明一实施方式,一种晶片封装体的制造方法包括接合第一晶片与第二晶片,其中第一晶片与第二晶片分别具有第一导电垫与第二导电垫;形成封装材料以覆盖第一晶片与第二晶片;移除围绕第二晶片的封装材料的一部分,使得封装材料具有上部、下部与邻接上部与下部的倾斜部,其中上部位于第二晶片上,下部位于第一晶片上;于封装材料的下部与上部分别形成第一通孔与第二通孔,使第一导电垫与第二导电垫分别从第一通孔与第二通孔裸露;以及形成沿封装材料的上部、倾斜部与下部设置的重布线层,其中重布线层延伸至第一通孔中的第一导电垫与第二通孔中的第二导电垫。

在本发明一实施方式中,移除围绕第二晶片的封装材料的部分是以刀具切除的方法执行。

在本发明一实施方式中,于封装材料的下部与上部分别形成第一通孔与第二通孔是以激光钻孔的方法执行。

在本发明一实施方式中,晶片封装体的制造方法还包括形成钝化层以覆盖重布线层及封装材料。

在本发明一实施方式中,晶片封装体的制造方法还包括形成开口于钝化层中以暴露重布线层。

在本发明一实施方式中,形成导电结构于开口中的重布线层上,以电性连接重布线层。

在本发明上述实施方式中,由于晶片封装体的第一晶片与第二晶片是在垂直方向上堆叠,因此不仅可缩减晶片封装体的面积,还可让晶片封装体具有多样化的功能。此外,由于封装材料具有倾斜部及分别位于第一晶片与第二晶片上的下部与上部,因此可有效降低封装材料的通孔的深宽比(Aspect ratio),使其上的重布线层不易断线,提升可靠度。

附图说明

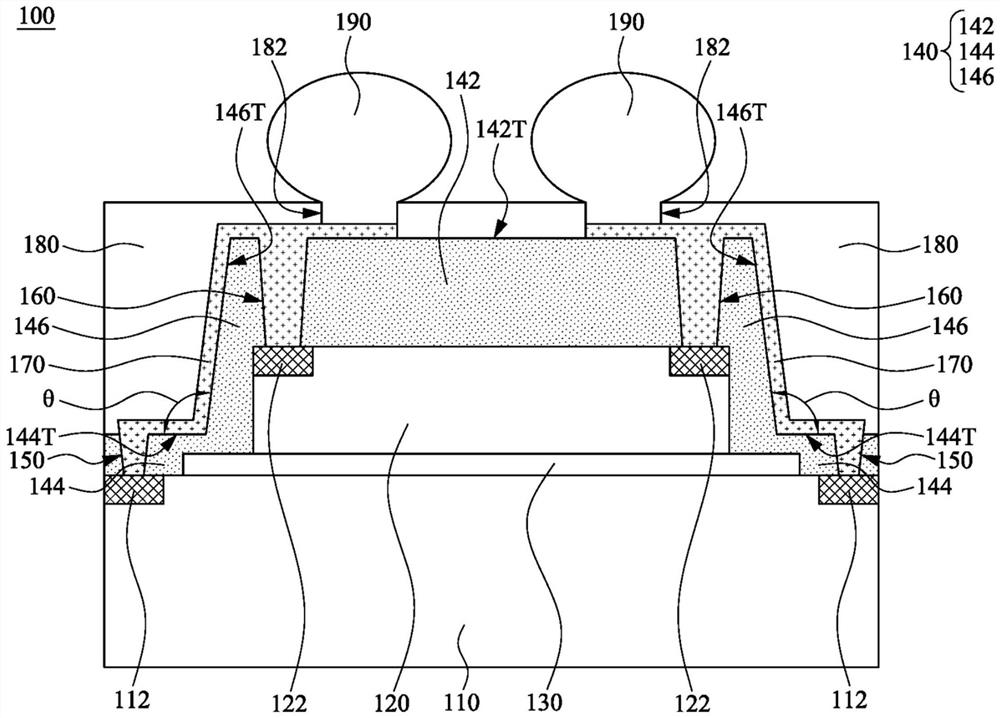

图1绘示根据本发明一实施方式的晶片封装体的剖面图。

图2至图6绘示图1的晶片封装体的制造方法中各阶段的剖面图。

图7绘示根据本发明一实施方式的第二晶片的剖面图。

图8绘示根据本发明另一实施方式的晶片封装体的剖面图。

其中,附图中符号的简单说明如下:

100、200:晶片封装体;110:第一晶片;112:第一导电垫;120、120a:第二晶片;122:第二导电垫;124:本体部;126:盖体部;128:侦测器;130、132:贴合胶;140:封装材料;142:上部;144:下部;146:倾斜部;142T、144T、146T:上表面;150:第一通孔;160:第二通孔;170:重布线层;180:钝化层;182:开口;190:导电结构;θ:钝角;210:第一晶片;212:第一导电垫;220:第二晶片;222:第二导电垫;230:第三晶片;232:第三导电垫;240A、240B:封装材料;250A:第一通孔;260A:第二通孔;250B:第三通孔;260B:第四通孔;270A、270B:重布线层;280A、280B:钝化层;282:开口;290:导电结构。

具体实施方式

以下配合图式说明本发明的多个实施方式,为简化图式,一些已知惯用的结构与元件将以简单示意的方式绘示。

图1绘示根据本发明一实施方式的晶片封装体100的剖面图。晶片封装体100具有第一晶片110、第二晶片120、封装材料140以及重布线层170。第一晶片110具有第一导电垫112,第二晶片120具有第二导电垫122。封装材料140覆盖第一晶片110与第二晶片120。封装材料140具有上部142、下部144与邻接上部142与下部144的倾斜部146。上部142位于第二晶片120上,下部144位于第一晶片110上。在本实施方式中,封装材料140可以为模压树脂(Molding compound)。重布线层170沿上部142、倾斜部146与下部144设置,且电性连接第一导电垫112与第二导电垫122。

此外,晶片封装体100还具有设置于第一晶片110与第二晶片120之间的贴合胶130,用以接合第一晶片110与第二晶片120。本发明的晶片封装体100可以为系统级封装结构(System in Package,SIP)。第一晶片110与第二晶片120可具有不同的功能,使得晶片封装体100可具有多样化的功能。举例来说,第一晶片110可以为主动元件,例如可为专用集成电路(Application Specific Integrated Circuit,ASIC)。第二晶片120可以为被动元件,例如可为微机电系统(Micro-Electro-Mechanical Systems,MEMS)。在一些实施方式中,第一晶片110为计算单元,第二晶片120为加速器。在本实施方式中,由于晶片封装体100的第一晶片110与第二晶片120是在垂直方向上堆叠,因此可缩减晶片封装体100的面积。

如图1所示,第二晶片120的宽度小于第一晶片110的宽度。第一导电垫112与第二晶片120不重叠,第一导电垫112也与贴合胶130不重叠。换句话说,一部分的第一晶片110未被第二晶片120以及贴合胶130覆盖。第一晶片110较第二晶片120靠近晶片封装体100的外侧。封装材料140的下部144位于第一晶片110未被第二晶片120覆盖的部分上,也就是封装材料140的下部144覆盖在第一晶片110的第一导电垫112上。

封装材料140的下部144具有上表面144T,封装材料140的上部142具有上表面142T,且下部144的上表面144T低于上部142的上表面142T。封装材料140的倾斜部146与下部144之间夹钝角θ。钝角θ也有利于重布线层170形成于封装材料140上,可避免重布线层170断线。换句话说,倾斜部146具有连接上部142的上表面142T以及下部144的上表面144T的上表面146T。如图1中所示,上部142的上表面142T、倾斜部146的上表面146T以及下部144的上表面144T共同构成阶梯状的表面。

封装材料140的下部144与上部142还分别具有第一通孔150与第二通孔160。第一导电垫112与第二导电垫122分别位于第一通孔150与第二通孔160中。由于封装材料140的下部144的上表面144T低于上部142的上表面142T,因此第一通孔150的深宽比可有效降低。第一通孔150的深度大致与下部144的厚度相同。换句话说,第一通孔150的深度由封装材料140的下部144的厚度决定,不会受限于第二晶片120的厚度,因此第二晶片120的选用较具弹性。除此之外,由于第二晶片120是堆叠在第一晶片110上,第二通孔160的深度由封装材料140的上部142的厚度决定,因此第二通孔160的深宽比也可降低。

重布线层170与封装材料140的上部142、倾斜部146以及下部144共形,并延伸至第一通孔150与第二通孔160中。在本实施方式中,由于第一通孔150与第二通孔160的深宽比较低,且重布线层170沿封装材料140的阶梯状的表面(即由上部142、倾斜部146以及下部144共同形成的表面)设置,因此不易断线,可有效提升可靠度,此外,还可让第一通孔150与第二通孔160的清洗更加容易。如此一来,第一导电垫112与第二导电垫122的间隔(Pitch)也可缩减,提升晶片封装体100的竞争力。

晶片封装体100还具有钝化层180以及导电结构190。钝化层180覆盖重布线层170及封装材料140,且钝化层180与封装材料140可由不同材料制造。钝化层180还具有开口182。导电结构190位于开口182中的重布线层170上。在一些实施方式中,导电结构190可为球栅阵列封装(Ball Grid Array,BGA)、导电凸块或导电柱。

在本实施方式中,由于晶片封装体100通过重布线层170使第一晶片110及第二晶片120与导电结构190电性连接,因此比传统打线接合的封装方式更为稳定,且能有效缩小晶片封装体100的体积。此外,信号经由重布线层170传输至导电结构190的距离缩短,可使得晶片封装体100的效能提升。

应了解到,已叙述过的元件连接关系、材料与功效将不再重复赘述,合先叙明。在以下叙述中,将说明晶片封装体100的制造方法。

图2至图6绘示图1的晶片封装体100的制造方法中各阶段的剖面图。参阅图2,首先通过贴合胶130接合第一晶片110与第二晶片120。第一晶片110的第一导电垫112未被第二晶片120以及贴合胶130覆盖而露出。

参阅图3,形成封装材料140以覆盖第一晶片110与第二晶片120。具体来说,封装材料140围绕第二晶片120且接触第二晶片120的侧壁,且封装材料140覆盖在第一导电垫112与第二导电垫122上。

参阅图4,移除围绕第二晶片120的封装材料140的一部分,使得封装材料140具有上部142、下部144与邻接上部142与下部144的倾斜部146。此外,也使得下部144的上表面144T低于上部142的上表面142T。移除围绕第二晶片120的封装材料140的部分是以刀具切除的方法执行。举例来说,刀具可具有特定的宽度,且刀具的相对两侧面具有与倾斜部146的上表面146T相近的斜面。如此一来,可通过刀具快速地形成平滑的倾斜部146的上表面146T以及下部144的上表面144T,并形成倾斜部146与下部144之间的钝角θ。在一些实施方式中,刀具的宽度在约1um至约3mm的范围中。

参阅图5,于封装材料140的下部144与上部142分别形成第一通孔150与第二通孔160,使第一导电垫112与第二导电垫122分别从第一通孔150与第二通孔160裸露。第一通孔150与第二通孔160是以激光钻孔的方法执行。如此一来,可精准地使第一通孔150以及第二通孔160分别露出第一导电垫112以及第二导电垫122。

参阅图6,沿封装材料140的上部142、倾斜部146与下部144形成重布线层170,其中重布线层170延伸至第一通孔150中的第一导电垫112与第二通孔160中的第二导电垫122。在本实施方式中,由于倾斜部146的上表面146T为平滑的倾斜表面,有利于重布线层170贴附于倾斜部146上,因此可避免重布线层170断线。此外,由于第一通孔150与第二通孔160的深宽比较低,也可避免延伸至第一通孔150与第二通孔160中的重布线层170产生间隙而断线。

回到图1,形成重布线层170后,可形成钝化层180以覆盖重布线层170及封装材料140。接着,形成开口182于钝化层180中,以暴露重布线层170。之后,可形成导电结构190于开口182中的重布线层170上,以电性连接重布线层170。

在以下叙述中,将说明其他形式的第二晶片与晶片封装体。

图7绘示根据本发明一实施方式的第二晶片120a的剖面图。第二晶片120a具有本体部124、盖体部126以及侦测器128。本体部124具有第二导电垫122。第二晶片120a还具有贴合胶132,设置以将盖体部126以及侦测器128接合至本体部124上。在一些实施方式中,本体部124可为微机电系统(MEMS)。侦测器128例如可为悬臂阀。在一些实施方式中,第二晶片120a的第二导电垫122也可设置在盖体部126上。

图8绘示根据本发明另一实施方式的晶片封装体200的剖面图。晶片封装体200具有第一晶片210、第二晶片220、封装材料240A、重布线层270A以及钝化层280A。第一晶片210与第二晶片220分别具有第一导电垫212与第二导电垫222。上述结构与前述晶片封装体100的结构与制造方法相似,于此不再赘述。

与图1的晶片封装体100不同的地方在于,晶片封装体200还具有第三晶片230、封装材料240B、重布线层270B以及钝化层280B。第三晶片230位于重布线层270A以及钝化层280A上,并具有第三导电垫232。封装材料240B覆盖第三晶片230、重布线层270A以及钝化层280A上。封装材料240B具有第三通孔250B以及第四通孔260B,且第三导电垫232位于第四通孔260B中。重布线层270B电性连接第三导电垫232与第二导电垫222。具体来说,第二通孔260A电性连接第三通孔250B,而重布线层270B通过第二通孔260A与第三通孔250B电性连接至第二导电垫222。第三通孔250B以及第四通孔260B具有与第一通孔250A以及第二通孔260A相似的结构。封装材料240B、重布线层270B以及钝化层280B也分别具有与封装材料240A、重布线层270A以及钝化层280A相似的结构。换句话说,第三晶片230堆叠至第二晶片220上的方式与第二晶片220堆叠至第一晶片210上的方式相同。晶片封装体200还具有开口282以及导电结构290。开口282位于钝化层280B与重布线层270B重叠的部分上。导电结构290位于开口282中的重布线层270B上。

在本实施方式中,第一晶片210、第二晶片220以及第三晶片230可具有不同功能。晶片封装体200通过将第一晶片210、第二晶片220以及第三晶片230在垂直方向上堆叠,可缩减晶片封装体200的面积,并结合多种不同功能至晶片封装体200。此外,封装材料240A与封装材料240B皆具有与图1的封装材料140相似的阶梯状表面,可有效避免重布线层270A与重布线层270B断线。

以上所述仅为本发明较佳实施例,然其并非用以限定本发明的范围,任何熟悉本项技术的人员,在不脱离本发明的精神和范围内,可在此基础上做进一步的改进和变化,因此本发明的保护范围当以本申请的权利要求书所界定的范围为准。

- 晶片封装体的制造方法及晶片封装体

- 晶片封装体、晶片封装体的形成方法以及封装晶圆