一种基于FPGA的近眼显示图像预畸变系统

文献发布时间:2023-06-19 09:46:20

技术领域

本发明涉及图像畸变校正系统领域,特别是涉及一种基于FPGA的近眼显示图像预畸变系统。

背景技术

近眼显示(Near-to-eye Display)也称为头戴式显示或头盔显示,它的工作原理是利用微显示器作为图像源,通过光学系统的光学放大后投射到人眼,使人产生沉浸或虚拟现实的感觉。其中微显示器和近眼光学系统组成显示模组,再与软硬件驱动电路、机械构架等组成近眼显示器。由于近眼显示技术和传统的显示技术(CRT、液晶显示、LED显示等)相比具有体积小、功耗低、画质清晰并且携带方便、解放双手等一系列优点,其应用领域愈加广泛。

近眼显示器最初应用于军用飞机,目前涉及的应用范围广泛,具备智能操作系统的头盔显示器((HelmetMountedDisplay,HMD)开始商业化,比如谷歌眼镜;许多民用航空飞机上已经配备了平视显示器(Head-up display,HUD),同时,装配在汽车、火车或者地铁列车上可以更加方便地给驾驶员供路况、导航等信息,避免注意力中断以及丧失对状态意识的掌握,提高驾驶的安全性。

但是,近眼显示器的光学系统一般采用离轴设计,离轴光学系统存在复杂的畸变问题,除了传统径向畸变以外,还有共轴光学系统不存在的弓形畸变和梯形畸变。投影图像的畸变不仅会影响观察的舒适感,甚至会造成观察者对重要信息的误判,导致不必要的损失。因此,如何消除近眼显示器投影图像的畸变是函待解决的问题。

FPGA器件有强大的并行处理能力,可以实现视频图像的实时预畸变过程。但是求取图像预畸变映射坐标涉及繁琐的坐标变换和浮点数的多阶矩阵乘法,因此有研究团队采用CPU软核+DSP计算的方式实现预畸变,但是这种方式处理速度低,很难实现高分辨率、高帧率视频图像实时预畸变过程。后来,有研究人员提出将需要计算的坐标值事先储存在查找表(Look-Up-Table,LUT)内,借助坐标LUT的方法可省去复杂的运算,因而不仅显著提高处理速度而且节省大量FPGA中的DSP资源,此外在FPGA系统内也易于控制和实现。

但是通常在FPGA的硬件平台上内存资源较为紧缺,只能缓存较少的图像数据,所以基于FPGA的视频图像实时预畸变系统只能处理较低分辨率的视频图像。同时,现有的预畸变系统图像灰度校正模块为了保证系统实时性要求通常采用低阶插值算法,导致输出图像边缘锯齿感严重,影响视觉感受。

因此,现有的图像预畸变系统目前仍存在图像处理分辨率较低、校正图像锯齿感严重、FPGA存储资源利用率较低、系统输出延时较大等问题。

发明内容

本发明的目的是提供一种基于FPGA的近眼显示图像预畸变系统,对近眼微显示器光学系统投影图像具有良好的校正效果,减少FPGA资源消耗,提高处理的实时性,进而满足近眼显示领域对微显示器显示效果的要求。

为实现上述目的,本发明提供了如下方案:

一种基于FPGA的近眼显示图像预畸变系统,包括:

HDMI视频接收器,用于接收PC端发送的视频图像数据;

SD卡存储器,用于存储预畸变系数映射表数据;

DDR3存储器,用于将所述SD卡存储器中的所述预畸变系数映射表数据进行写入和读取;

近眼显示图像预畸变系统,用于将所述视频图像数据缓存到Block RAM中,并根据所述预畸变系数映射表数据中的坐标位置信息从所述Block RAM的相应位置读取图像灰度值,并根据所述坐标位置信息得到插值系数数据,以及根据所述插值系数数据和所述图像灰度值重建灰度后得到预畸变后的图像灰度信息,进而得到预畸变后的视频图像数据;

HDMI视频发送器,用于将所述预畸变后的视频图像数据发送到近眼显示器。

可选的,所述近眼显示图像预畸变系统包括:

HDMI数据收发模块,用于接收PC端的视频图像数据以及发送所述预畸变后的视频图像数据;

预畸变系数存取模块,用于接收所述SD卡存储器中的预畸变系数映射表数据;还用于将所述预畸变系数映射表数据写入所述DDR3存储器,根据坐标预畸变模块发出的读请求信号从所述DDR3存储器读取所述预畸变系数映射表数据;

图像数据缓存模块,用于将所述视频图像数据缓存到所述Block RAM中,然后根据所述预畸变系数映射表数据中的坐标位置信息从所述Block RAM的相应位置取出图像灰度值;

坐标预畸变模块,用于将所述DDR3存储器中的所述预畸变系数映射表数据中的坐标位置信息适配为64bit索引格式的行列坐标数据和插值系数数据,并将所述坐标位置信息中的行列坐标数据作为Block RAM的读写地址;

灰度预畸变模块,用于将所述插值系数数据以及所述图像灰度值进行双线性插值运算,得到预畸变后的图像灰度信息,进而得到所述预畸变后的视频图像数据。

可选的,所述HDMI数据收发模块包括:

HDMI视频接收器接口,用于接收所述PC端的视频图像数据;

HDMI视频发送器接口,用于将所述预畸变后的视频图像数据输出到所述近眼显示器;

HDMI寄存器配置单元,用于通过IIC总线与FPGA的IO接口相连,并通过所述FPGA对所述HDMI视频接收器和所述HDMI视频发送器进行初始化和控制操作。

可选的,所述预畸变系数存取模块包括:

SD卡存储器接口,用于通过SPI总线通信接口进行所述FPGA与所述SD卡存储器的通信;

SD卡存储器读取单元,用于通过SPI总线配置SD卡初始化和命令;还用于读取所述SD卡存储器中的所述预畸变系数映射表数据;

DDR3存储器接口,用于通过AXI总线通信接口进行所述FPGA与所述DDR3存储器的通信;

DDR3存储器存取单元,用于接收所述SD卡存储器读取单元发送的写请求信号并应答,并通过AXI总线将所述SD卡存储器读取单元中的写数据写入所述DDR3存储器中进行缓存;还用于接收所述坐标预畸变模块发送的读请求信号并应答,并通过AXI总线读取所述DDR3存储器中缓存的预畸变系数映射表数据。

可选的,所述图像数据缓存模块包括:

BRAM写地址控制单元,用于生成BRAM的写地址;

BRAM存储单元,用于将接收的所述HDMI视频接收器接口的视频图像数据进行缓存。

可选的,所述坐标预畸变模块包括:

BRAM读地址控制单元,用于接收所述DDR3存储器存取单元中的所述行列坐标数据,并将所述行列坐标数据作为BRAM的读地址;

插值系数缓冲单元,用于接收所述DDR3存储器存取单元中的所述插值系数数据,并将所述插值系数数据进行缓冲后,输出到所述灰度预畸变模块。

可选的,所述灰度预畸变模块包括:

双线性插值单元,用于接收所述BRAM存储单元的相邻两行的4个像素值,并与所述插值系数缓冲单元中的2个插值系数进行双线性插值运算,得到预畸变后的图像灰度值。

根据本发明提供的具体实施例,本发明公开了以下技术效果:

本发明所提供的一种基于FPGA的近眼显示图像预畸变系统,是将近眼显示图像预畸变系统结合SD卡存储器、DDR3存储器、HDMI视频接收器及HDMI视频发送器,用SD卡存储器代替了FPGA片内Flash存储器来存放坐标映射查找表,SD卡存储器可以存储高分辨率图像的坐标映射查找表并且方便修改。本发明对近眼微显示器光学系统投影图像具有良好的校正效果,减少了FPGA资源消耗,处理的实时性得到了保证。对于不同光学系统的图像畸变,只需要改变片外SD卡存储的映射查找表。本发明能够很好地满足近眼显示领域对微显示器显示效果的要求。

附图说明

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

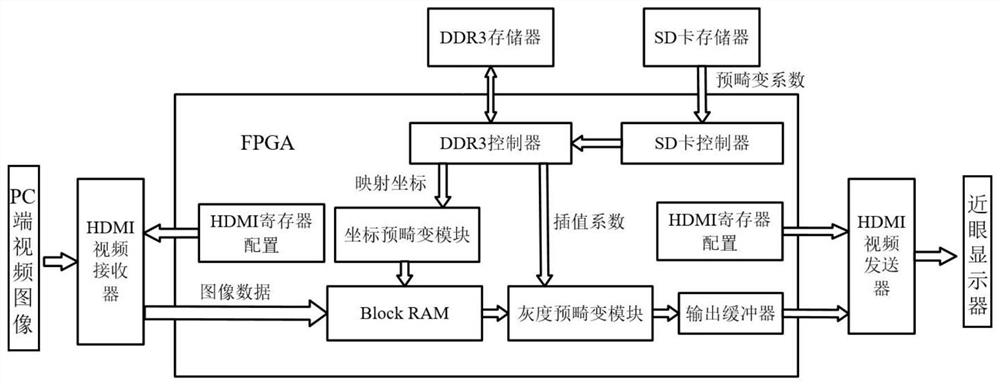

图1为本发明所提供的一种基于FPGA的近眼显示图像预畸变系统的结构示意图;

图2为本发明所提供的所述预畸变系数存取模块的结构示意图;

图3为本发明所提供的所述图像数据缓存模块的结构示意图;

图4为本发明所提供的所述双线性插值子模块的结构示意图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

本发明的目的是提供一种基于FPGA的近眼显示图像预畸变系统,对近眼微显示器光学系统投影图像具有良好的校正效果,减少FPGA资源消耗,提高处理的实时性,进而满足近眼显示领域对微显示器显示效果的要求。

为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

图1为本发明所提供的一种基于FPGA的近眼显示图像预畸变系统的结构示意图,如图1所示,本发明提供的一种基于FPGA的近眼显示图像预畸变系统,包括:HDMI视频接收器、SD卡存储器、DDR3存储器、近眼显示图像预畸变系统以及HDMI视频发送器。

HDMI视频接收器用于接收PC端发送的视频图像数据。

SD卡存储器用于存储预畸变系数映射表数据。

DDR3存储器用于将所述SD卡存储器中的所述预畸变系数映射表数据进行写入和读取。

近眼显示图像预畸变系统用于将所述视频图像数据缓存到Block RAM中,并根据所述预畸变系数映射表数据中的坐标位置信息从所述Block RAM的相应位置读取图像灰度值,并根据所述坐标位置信息得到插值系数数据,以及根据所述插值系数数据和所述图像灰度值重建灰度后得到预畸变后的图像灰度信息,进而得到预畸变后的视频图像数据。

HDMI视频发送器用于将所述预畸变后的视频图像数据发送到近眼显示器。

如图1所示,所述近眼显示图像预畸变系统包括:HDMI数据收发模块、预畸变系数存取模块、图像数据缓存模块、坐标预畸变模块以及灰度预畸变模块。

HDMI数据收发模块用于接收PC端的视频图像数据以及发送所述预畸变后的视频图像数据。

预畸变系数存取模块用于接收所述SD卡存储器中的预畸变系数映射表数据;还用于将所述预畸变系数映射表数据写入所述DDR3存储器,根据坐标预畸变模块发出的读请求信号从所述DDR3存储器读取所述预畸变系数映射表数据。

图像数据缓存模块用于将所述视频图像数据缓存到所述Block RAM中,然后根据所述预畸变系数映射表数据中的坐标位置信息从所述Block RAM的相应位置取出图像灰度值。

坐标预畸变模块用于将所述DDR3存储器中的所述预畸变系数映射表数据中的坐标位置信息适配为64bit索引格式的行列坐标数据和插值系数数据,并将所述坐标位置信息中的行列坐标数据作为Block RAM的读写地址。

灰度预畸变模块用于将所述插值系数数据以及所述图像灰度值进行双线性插值运算,得到预畸变后的图像灰度信息,进而得到所述预畸变后的视频图像数据。

所述HDMI数据收发模块包括:HDMI视频接收器接口、HDMI视频发送器接口以及HDMI寄存器配置单元。

HDMI视频接收器接口用于接收所述PC端的视频图像数据;视频分辨率为1280×1024@60Hz,工作时钟为108MHz。

HDMI视频发送器接口用于将所述预畸变后的视频图像数据输出到所述近眼显示器;视频分辨率为1280×1024@60Hz,工作时钟为108MHz。

HDMI寄存器配置单元用于通过IIC总线与FPGA的IO接口相连,并通过所述FPGA对所述HDMI视频接收器和所述HDMI视频发送器进行初始化和控制操作。

所述预畸变系数存取模块包括:SD卡存储器接口、SD卡存储器读取单元、DDR3存储器接口以及DDR3存储器存取单元。

SD卡存储器接口用于通过SPI总线通信接口进行所述FPGA与所述SD卡存储器的通信。

SD卡存储器读取单元用于通过SPI总线配置SD卡初始化和命令;还用于读取所述SD卡存储器中的所述预畸变系数映射表数据。

DDR3存储器接口用于通过AXI总线通信接口进行所述FPGA与所述DDR3存储器的通信。

DDR3存储器存取单元用于接收所述SD卡存储器读取单元发送的写请求信号并应答,并通过AXI总线将所述SD卡存储器读取单元中的写数据写入所述DDR3存储器中进行缓存;还用于接收所述坐标预畸变模块发送的读请求信号并应答,并通过AXI总线读取所述DDR3存储器中缓存的预畸变系数映射表数据。

图2为本发明所提供的所述预畸变系数存取模块的结构示意图,如图2所示,所示的预畸变系数存取模块主要包括SD卡存储器读取控制和DDR3存储器读写控制两大部分。

其中,FPGA通过SPI数据总线访问Micro SD卡,工作时钟为25MHz。SD卡存储器的初始化和命令/响应操作均通过SPI总线进行配置。SD卡数据传输长度采用512Bytes,预畸变系数表以64bit坐标索引格式存储,所以一次数据传输中读写64个64bit数据。

在DDR3存储设计中,选用64bit数据位用户接口适配64bit坐标索引格式,存储器工作时钟为200MHz,为了方便读写DDR3存储器,系统调用了Xilinx提供的DDR3控制器IP核MIG,由于选用具有AXI总线的DDR3控制器,所以需要添加AXI4总线协议转换模块与用户接口进行数据交互。同时,由于各模块的控制时钟不同,所以分别使用了读写FIFO存储阵列进行数据交互。

所述图像数据缓存模块包括:BRAM写地址控制单元以及BRAM存储单元。

BRAM写地址控制单元用于生成BRAM的写地址;写地址为[1:max_add]顺序生成。

BRAM存储单元用于将接收的所述HDMI视频接收器接口的视频图像数据进行缓存。

图3为本发明所提供的所述图像数据缓存模块的结构示意图,如图3所示,图像数据缓存模块设计了4个BlockRAM缓存结构,其中两个缓存奇行数据,两个缓存偶行数据,每个RAM中只缓存原来二分之一的数据。在一个时钟内,两个奇行Block RAM分别读出(T

所述坐标预畸变模块包括:BRAM读地址控制单元以及插值系数缓冲单元。

BRAM读地址控制单元用于接收所述DDR3存储器存取单元中的所述行列坐标数据,并将所述行列坐标数据作为BRAM的读地址。

插值系数缓冲单元用于接收所述DDR3存储器存取单元中的所述插值系数数据,并将所述插值系数数据进行缓冲后,输出到所述灰度预畸变模块。

所述灰度预畸变模块包括:双线性插值单元。

双线性插值单元用于接收所述BRAM存储单元的相邻两行的4个像素值,并与所述插值系数缓冲单元中的2个插值系数进行双线性插值运算,得到预畸变后的图像灰度值。

图4为本发明所提供的所述双线性插值子模块的结构示意图,如图4所示,所示的双线性插值子模块在一个时钟取出相邻两行的4个像素值,分别记为data_odd,data_odd1,data_even和data_even1,经过1024倍放大的插值系数记为coef_x和coef_y,因此双线性插值公式可以改为:

其中,具体的实现步骤如下:

(1)计算1-coef_x和1-coef_y,因为插值系数放大了1024倍,所以这里“1”对应“1024”,同时4个像素值缓存相应时钟。

(2)10bit的coef_x和1-coef_x按照插值公式分别与4个8bit像素值相乘,得到4个18bit的中间值,同时coef_y和1-coef_y缓存相应时钟。

(3)10bit的coef_y和1-coef_y分别与4个18bit的中间值相乘,得到4个28bit的运算结果。

(4)4个28bit的运算结果两两相加。

(5)得到值再一步相加,取高8bit结果输出,即为新的灰度值。

计算过程共进行8次乘法运算和5次加法运算,利用DSP48E硬件乘法器实现。

本发明所提供的一种基于FPGA的近眼显示图像预畸变系统的具体工作过程为:

首先,软件计算出的预畸变系数映射表数据预先存储在SD卡存储器中,FPGA开发板上电后,系统将预畸变系数映射表数据读取到DDR3存储器中;PC端或其它视频源的视频数据通过HDMI视频接收模块解码后缓存到片内Block RAM中。然后,系统根据映射表中的坐标位置信息从Block RAM的相应位置取出图像灰度值与映射表中的插值系数进行双线性插值运算,运算得到的灰度值即为预畸变图像的灰度信息。最后,调整控制时序,将预畸变图像数据通过HDMI视频发送模块发送到近眼显示器上。

本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。

本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处。综上所述,本说明书内容不应理解为对本发明的限制。

- 一种基于FPGA的近眼显示图像预畸变系统

- 基于FPGA的近眼双目成像系统的图像处理系统及方法