驱动电路的驱动端口状态检测电路及方法

文献发布时间:2023-06-19 09:57:26

技术领域

本发明涉及电力电子技术领域,尤其涉及驱动电路的驱动端口状态检测电路及方法。

背景技术

对于功率管驱动端口的状态检测判断,通常的检测电路是在功率管驱动支路与功率管之间增加采样电阻,在功率管开启或关闭的瞬间,功率管栅极驱动电流会在采样电阻上产生压降,通过采集该压降作为采样信号进行判断,但是由于该采样信号通常时间较短,易受到干扰,以及由于存在抖动等问题,导致状态检测的结果不准确,使用局限性较大。

发明内容

为了解决上述的技术问题,本发明的一个目的是提供一种驱动端口状态检测电路,包括驱动电路、采样电路和延时模块;

所述驱动电路包括驱动管;

所述采样电路包括开关管和电容串联结构,所述开关管接入驱动电路的驱动端口,在开关管与驱动管之间设有延时模块,所述延时模块引入驱动信号的固定延时,开关管提前固定延时时间导通后形成电容串联结构;

所述电容串联结构包括串联结构的采样电容和驱动端口的寄生电容,在固定延时的时间内,电容串联结构利用小电流对采样电容和寄生电容进行充电,对驱动电路的驱动端状态进行采样。

采用以上技术方案,所述驱动管包括驱动端上驱动管,所述驱动端上驱动管与驱动电路的输入端口形成信号输入支路udb,在所述信号输入支路udb上引出信号输入支路uda,所述信号输入支路uda连接开关管,且在信号输入支路udb上设有延时模块,所述延时模块引入驱动信号的固定延时。

采用以上技术方案,所述驱动管包括驱动端下驱动管,所述驱动端下驱动管与驱动电路的驱动端口形成信号输入支路Idb,信号输入支路Idb上设有延时模块,所述延时模块引入驱动信号的固定延时。

采用以上技术方案,所述寄生电容包括第一寄生电容和第二寄生电容,所述第一寄生电容为驱动电路的驱动端口对地寄生电容,所述第二寄生电容为功率管栅极对地寄生电容,所述第一寄生电容、第二寄生电容满足以下关系:

Cs=Csp+Csd;

Csp>>Csd;

Cd>Csd;

Csp>>Cd;

且当Csp不存在时,Vcc*Csd/(Csd+Cd)<|Vthmp2|;

其中Cs为寄生电容,Csd为第一寄生电容,Csp为第二寄生电容,Cd为采样电容;Vcc为电源;Vthmp2为采样管的阈值开启电压。

采用以上技术方案,所述采样电路包括采样管,所述开关管的漏极与驱动电路的驱动端口相连,所述开关管的源极、采样管的栅极与采样电容的下极板三者相连,所述采样电容的上极板与采样管的源极连接电源Vcc。

采用以上技术方案,所述采样电路包括电流源Ibias,在所述采样管的漏极引入电流源Ibias。

本发明的另一目的是提供一种驱动端口状态检测方法,包括:

在开关管与驱动管之间引入驱动信号的固定延时;

驱动电路的输入端口输入驱动信号,开关管提前固定延时时间导通后形成电容串联结构;

在固定延时的时间内,电容串联结构利用小电流对串联的采样电容和寄生电容进行充电,对驱动电路的驱动端口状态进行采样,并在检测电路输出端口输出驱动端状态的指示信号;

根据检测电路输出端信号的波形判断驱动电路的驱动端的工作状态。

采用以上技术方案,所述在开关管与驱动管之间引入驱动信号的固定延时,包括:

驱动管包括驱动端上驱动管,驱动端上驱动管与驱动电路的输入端口形成信号输入支路udb,在信号输入支路udb上引出信号输入支路uda,信号输入支路uda连接开关管,以使开关管与驱动端上驱动管具有相同波形的驱动信号的输入,且在信号输入支路udb上引入驱动信号的固定延时,以使开关管与驱动端上驱动管之间具有驱动信号输入的固定延时。

采用以上技术方案,所述电容串联结构利用小电流对串联的采样电容和寄生电容进行充电,包括:

开关管提前固定延时时间导通,利用小电流对采样电容和寄生电容进行充电,由于第二寄生电容远大于采样电容,采样电容的下极板节点Aadj电压被迅速下拉,并随着充电结束稳定在Vcd=Vcc*Cs/(Cd+Cs),其中Vcd为采样电容电压降,Vcc为电源电压,Cs为总的寄生电容,Cd为采样电容;

在固定延时的时间内,由于驱动端口的寄生电容容值远大于采样电容容值,因此采样管的栅源电压Vgsmp2小于采样管的阈值开启电压Vthmp2,采样管导通且采样管的漏极电流远大于电流源Ibias,使得采样管的漏极电压由Gnd迅速拉升至接近Vcc。

采用以上技术方案,所述根据检测电路输出端信号的波形判断所述驱动电路的驱动端的工作状态,包括:

首先判断检测电路输出信号和输入信号是否为具有相同周期的周期性脉冲,如果判断结果为是,那么该驱动电路的驱动端为正常状态;

如果判断结果为否,那么判断检测电路输出端信号的波形是否为高电平;如果判断结果为是,那么该驱动电路的驱动端为短路状态;

如果判断结果为否,那么该驱动电路的驱动端为开路状态。

本发明的有益效果:本发明在驱动电路的驱动端口与电源之间设置电源对地的电容串联结构,在开关管与驱动管之间引入驱动信号的固定延时,在固定延时时间内,通过开关管控制在一个微小导通时间内对该电容串联结构进行充电,并对驱动电路的驱动端进行采样,通过判断采样结果判断驱动电路的驱动端的工作状态,由于引入相对独立的采样判断时间并使用电容器件进行采样,采样信号稳定且不易受到干扰,大大提高了检测结果的精确性,确保判断结果准确可靠。

附图说明

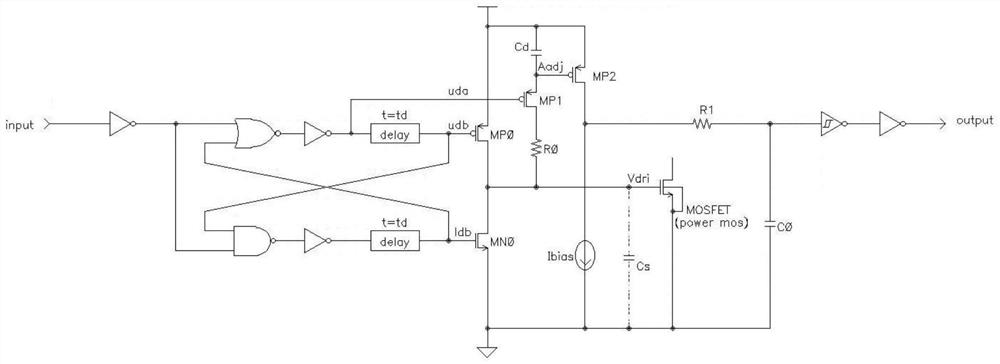

图1是本发明驱动线路的驱动端口状态检测电路的原理示意图。

图2是本发明电容串联结构的原理示意图。

图3是本发明驱动线路的驱动端口状态检测方法的流程示意图。

图4是本发明驱动线路的驱动端口为正常状态下的各个节点的波形图。

图5是本发明驱动线路的驱动端口为开路状态下的电容串联结构的原理示意图。

图6是本发明驱动线路的驱动端口为开路状态下的各个节点的波形图。

图7是本发明驱动线路的驱动端口为短路状态下的电容串联结构的原理示意图。

图8是本发明驱动线路的驱动端口为短路状态下的各个节点的波形图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。

所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本发明,而不能理解为对本发明的限制。

在本发明中,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本发明中的具体含义。

图1所示为本发明一种驱动电路的驱动端口状态检测电路的电路结构示意图,图中input为驱动电路的输入端口,MP0为驱动端上驱动管,MP1为开关管,MP2为采样管,MN0为驱动端下驱动管,delay为延时模块,Cd为采样电容,Cs为寄生电容(本发明特指驱动端对地的寄生电容),MOSFET为功率管,output为驱动电路的驱动端口状态检测电路的检测信号输出端口。

请参见图1所示,驱动端上驱动管MP0、驱动端下驱动管MN0组成该检测电路的驱动电路,在驱动电路的输入端口input有驱动信号输入时,通过驱动端上驱动管MP0和驱动端下驱动管MN0的上拉或下拉实现功率管MOSFET的开启或关闭。

请参见图1所示,开关管MP1、采样管MP2,电流源Ibias和电容串联结构组成该检测电路的采样电路,一方面驱动端上驱动管MP0与驱动电路的输入端口形成信号输入支路udb,在信号输入支路udb上引出信号输入支路uda,信号输入支路uda连接开关管MP1,且在信号输入支路udb上设有延时模块delay,延时模块delay引入驱动信号的固定延时td,使得驱动端上驱动管MP0和开关管MP1具有相同的驱动信号波形,但两者之间的驱动信号具有固定延时td;另一方面电容串联结构包括采样电容Cd和寄生电容Cs,在驱动电路的电源与驱动端口之间引入采样电容Cd和寄生电容Cs形成电源对地的电容串联结构;还有开关管MP1的源极,采样管MP2的栅极与采样电容Cd的下极板三者相连,采样电容Cd的上极板与采样管MP2的源极连接电源Vcc,采样管MP2的漏极与电流源Ibias相连,以保证电路在检测周期输出状态稳定。

请参见图1所示,驱动管包括驱动端下驱动管MN0,驱动端下驱动管MN0与驱动电路的驱动端口形成信号输入支路Idb,信号输入支路Idb上设有延时模块delay,延时模块delay引入驱动信号的固定延时td。其主要目的为保证功率管MOSFET的驱动波形与驱动电路的输入端口input的波形脉宽完全一致,寄生电容Cs的上极板节点Vdri的信号相对驱动电路的输入端口input的信号向后平移2*td的时间。通常情况下,功率管MOSFET的开关频率周期的时间Tsw>>td,且Csp>>Cd,因此功率管MOSFET本身的限制因素可以近似忽略。

设计中需要满足(Vcc-Vcd) 还有电阻R1和滤波电容C0组成该检测电路的滤波电路以进一步消除毛刺干扰。 检测电路设计中在驱动端上驱动管MP0的输入端口引入驱动信号的固定延时td,当开关管MP1在固定延时td时间内导通时(驱动端上驱动管MP0为关断),形成电源Vcc对地Gnd的电容串联结构。图2所示为电容串联结构的电路结构示意图,图中Csd为第一寄生电容,Csp为第二寄生电容,Aadj为采样电容Cd的下极板节点;Vdri为寄生电容Cs的上极板节点。 具体的,采样电容Cd与寄生电容Cs形成电容串联结构,其中寄生电容Cs包括第一寄生电容Csd和第二寄生电容Csp,第一寄生电容Csd为驱动电路的驱动端口对地寄生电容,第二寄生电容Csp为功率管MOSFET的栅极对地寄生电容,第一寄生电容Csd、第二寄生电容Csp和采样电容Cd满足以下关系: Cs=Csp+Csd; Csp>>Csd; Cd>Csd; Csp>>Cd; 且当Csp不存在时,Vcc*Csd/(Csd+Cd)<|Vthmp2|; 其中Vcc为电源;Vthmp2为采样管的阈值开启电压。 请参见图2所示,根据电容串联结构中电容压降与电容容量成反比的关系,可以得出公式如下:|Vgsmp2|=Vcd=Vcc*Cs/(Cd+Cs),其中Vgsmp2为采样管MP2的栅源电压,Vcd为采样电容电压降。 还有电阻R0可等效为开关管MP1的导通电阻及分压电阻之和,以对电容充电时间常数进行调整。 图3所示为本发明实施例2一种驱动电路的驱动端口状态检测方法的流程示意图,该检测方法结合图1和图2的内容进行详细的阐述。 参照图3所示,一种驱动电路的驱动端口状态检测方法,包括如下步骤: 在步骤S101中,在开关管MP1与驱动管之间引入驱动信号的固定延时。 示例地,驱动端上驱动管MP0与驱动电路的输入端口形成信号输入支路udb,在信号输入支路udb上引出信号输入支路uda,信号输入支路uda连接开关管MP1,以使开关管MP1与驱动端上驱动管MP0具有相同驱动信号的输入,且在信号输入支路udb上引入驱动信号的固定延时,以使开关管MP1与驱动端上驱动管MP0之间具有驱动信号输入的固定延时。 在步骤S102中,驱动电路的输入端口输入驱动信号,开关管MP1提前固定延时时间导通后形成电容串联结构。 在步骤S103中,在固定延时的时间内,电容串联结构利用小电流对串联的采样电容Cd和寄生电容Cs进行充电,对驱动电路的驱动端口的状态进行采样,并在检测电路输出端口output输出驱动端状态的指示信号。 示例地,开关管MP1提前固定延时时间导通,利用小电流对采样电容Cd和寄生电容Cs进行充电,由于第二寄生电容Csp远大于采样电容Cd,采样电容Cd的下极板节点Aadj电压被迅速下拉,随着充电结束稳定在Vcd=Vcc*Cs/(Cd+Cs);其中Vcd为采样电容上的电压降,Vcc为电源电压,Cs为寄生电容,Cd为采样电容;在固定延时的时间内,由于寄生电容Cs远大于采样电容Cd,因此采样管MP2的栅源电压小于采样管MP2的阈值开启电压,采样管导通且采样管的漏极电流远大于电流源Ibias,使得采样管MP2的漏极电压由Gnd迅速拉升至接近Vcc;之后检测电路输出端output输出驱动端口检测信号供后级电路读取结果。 在步骤S104中,根据检测电路输出端信号的波形判断驱动电路的驱动端的工作状态。 示例地,首先判断输出信号和输入信号是否为具有相同周期的周期性脉冲,如果判断结果为是,那么该驱动电路的驱动端状态正常;如果判断结果为否,那么判断检测电路输出端信号的波形是否为高电平;如果判断结果为是,那么该驱动电路的驱动端为短路状态;如果判断结果为否,那么该驱动电路的驱动端为开路状态。 综上所述,本发明在驱动电路的电源正与驱动端之间引入采样电容Cd,并利用驱动端对地寄生电容Cs,形成电源对地的电容串联结构,并且在开关管MP1与驱动端上驱动管MP0之间引入驱动信号的固定延时,在固定延时时间内,通过开关管MP1控制在一个微小导通时间内对该电容串联结构进行充电,并对驱动电路的驱动端进行采样,通过采样结果判断驱动电路驱动端的工作状态,由于引入相对独立的采样判断时间并使用电容器件进行采样,采样信号稳定且不易受到干扰,大大提高了检测结果的精确性,确保判断结果准确可靠。 还有传统的驱动端口状态检测电路大多只能单一的检测驱动端口的开路或短路状态,而本发明能够同时检测驱动端口的开路和短路状态,显著减小了使用局限性。 下面将采用实施例的方式具体的阐述本发明一种驱动电路的驱动端口状态检测方法的具体内容。 实施例1 以驱动端上驱动管MP0为PMOS管,功率管MOSFET为下管的驱动电路的驱动端口为正常工作状态的一种情况示例如下,图4为驱动电路的驱动端为正常状态的结果示意图。 由于固定延时td的引入,开关管MP1的栅极波形与驱动端上驱动管MP0的栅极波形完全相同,但驱动端上驱动管MP0的栅极波形相对于开关管MP1的栅极波形存在固定延时td向后平移,如图4中uda和udb的波形所示。 开始时,寄生电容Cs的上极板节点Vdri电压被驱动端下驱动管MN0提前释放为零电荷,当开关管MP1提前固定延时td时间导通时,如图2所示,电容串联结构开始对采样电容Cd和寄生电容Cs进行充电,此时由于功率管MOSFET的栅极寄生电容Csp(Csp>>Cd)存在(电荷为零),因此采样电容Cd的下极板节点Aadj电压被迅速下拉,并随着充电结束采样电容电压降稳定在Vcd=Vcc*Cs/(Cd+Cs),形成如图4所示的zoomA区域的Aadj波形。 在固定延时td时间内,寄生电容Cs由于小电流充电,寄生电容Cs的上极板节点Vdri电压会略微抬起,形成如图4所示的zoomB区域的Vdri波形。 在固定延时td时间内,由于Cs>>Cd,因此采样管MP2的栅源电压Vgsmp2小于采样管MP2的阈值开启电压Vthmp2,采样管MP2导通,漏极电流远大于电流源Ibias电流,促使采样管MP2的漏极电压由Gnd迅速拉升至接近Vcc,检测电路输出端output信号由零电平跳变为高电平。 当固定延时td时间结束,驱动端上驱动管MP0开启,由于驱动端上驱动管MP0的宽长比W/Lmp0远远大于开关管MP1的宽长比W/Lmp1,寄生电容Cs电压(Vdri节点电压)迅速上拉至Vcc,这时候功率管MOSFET开启,采样电容Cd的下极板节点Aadj电压跟随寄生电容Cs的上极板节点Vdri电压抬升至Vcc,采样电容Cd的两端等效短接,采样管MP2的栅源电压Vgsmp2变为0并关断,采样管MP2的漏极电压被电流源Ibias下拉为0,此时驱动电路端口状态检测电路的输出端output的信号跳变为低电平;在上半驱动周期结束时,开关管MP1提前固定延时td时间结束,此时节点Aadj处不存在电流释放通路,采样电容Cd下极板的节点Aadj电压被稳定锁存在Vcc,此时采样管MP2的栅源电压Vgsmp2=0V,采样管MP2保持关断。 综上所述,以上为该检测电路一个检测周期中各个节点的信号变化,在固定延时td开启到结束的过程中,驱动电路的驱动端口的状态检测电路的输出端output产生与驱动电路的输入端口input相同周期的周期性脉冲信号。 实施例2 以驱动端上驱动管MP0为PMOS管,功率管MOSFET为下管的驱动电路的驱动端为开路状态的一种情况示例如下,图6为驱动电路的驱动端口为开路状态的结果示意图。 当驱动电路的驱动端口开路时,功率管MOSFET的栅极与驱动端上驱动管MP0和驱动端下驱动管MN0的驱动端口断开,此时第二寄生电容Csp不存在。 开始时,寄生电容Cs的上极板节点Vdri电压被驱动端下驱动管MN0提前释放为零电荷,当开关管MP1提前固定延时td时间导通时,如图5所示,电容串联结构开始对采样电容Cd和寄生电容Cs进行充电,此时由于功率管MOSFET的栅极寄生电容Csp不存在,则有采样电容电压降Vcd=Vcc*Cs/(Cd+Cs)=Vcc*Csd/(Cd+Csd),其中设计时需满足Cd>Csd,形成如图6所示的zoomA区域的Aadj波形。 在固定延时td时间内,寄生电容Cs的上极板节点Vdri电压会在开关管MP1的电流充电下快速抬高到Vcs=Vcsd=Vcc*Cd/(Cd+Csd),形成如图6所示的zoomB区域的Vdri波形。 在固定延时td时间内,由于电路设计中保证Vcd<|Vthmp2|,则可保证采样管MP2在该种情况下保持截至状态,采样管MP2的漏极电压被电流源Ibias下拉持续为零,此时得到的驱动电路的驱动端口状态检测电路结果输出口output的信号在功率管MOSFET的栅极开路的情况下,始终维持低电平输出。 该检测电路输入,输出及中间各个节点的波形如图6所示,在驱动电路的驱动端口开路时,驱动电路的驱动端口状态检测电路结果输出口output的信号始终维持低电平0V输出。 实施例3 以驱动端上驱动管MP0为PMOS管,功率管MOSFET为下管的驱动电路的驱动端口为短路状态的一种情况示例如下,图8为驱动电路的驱动端口为短路状态的结果示意图。 当驱动电路的驱动端口对GND短路时,功率管MOSFET的栅极与驱动端上驱动管MP0和驱动端下驱动管MN0的驱动端口对地短路,寄生电容Cs的节点Vdri电压被强行下拉至Gnd,此时第一寄生电容Csd和第二寄生电容Csp均两端对地短接。 在整个驱动周期内,驱动端上驱动管MP0和开关管MP1导通,由于寄生电容Cs的节点Vdri电压短接至Gnd,故采样电容Cd的下极板节点Aadj电压同样被下拉至Gnd;当开关管MP1提前固定延时td时间截至时,如图7所述,该节点无电流通路,因此采样电容Cd的下极板节点Aadj电压被锁存至0V,在这种情况下,Vgsmp2 该检测电路输入,输出及中间各个节点的波形如图8所示,在驱动电路的驱动端口短路时,驱动电路的驱动端口状态检测电路结果输出口output的信号始终维持高电平Vcc输出。 以上所述实施例仅是为充分说明本发明而所举的较佳的实施例,本发明的保护范围不限于此。本技术领域的技术人员在本发明基础上所作的等同替代或变换,均在本发明的保护范围之内。本发明的保护范围以权利要求书为准。

- 驱动电路的驱动端口状态检测电路及方法

- 自带功率输出端口状态检测的驱动电路及低端和/或高端驱动控制电路