半导体电路以及半导体系统

文献发布时间:2023-06-19 10:11:51

相关申请

本申请享受以日本专利申请2019-166273号(申请日:2019年9月12日)为基础申请的优先权。本申请通过参照该基础申请而包含基础申请的所有内容。

技术领域

本发明的实施方式涉及半导体电路以及半导体系统。

背景技术

在检测流经马达等控制对象的电流的电流检测电路中,使用了隔离放大器。隔离放大器具有能够以保持电绝缘的状态对流经控制对象的电流进行检测并传送的特征。

在隔离放大器中设有ΔΣADC、解码器等信号处理电路,该信号处理电路中的处理花费时间,因此电流检测的响应时间需要几十μs左右的时间。因此,存在过电流在控制对象中流经时不能迅速地检测该过电流这一问题。

发明内容

实施方式提供能够迅速地检测流经控制对象的过电流的半导体电路以及半导体系统。

实施方式的半导体电路具备:一次电路,根据流经控制对象的电流使发光元件发光,并且在过电流流经所述控制对象的情况下,使所述发光元件更明亮地发光;二次电路,与所述一次电路电绝缘,输出与所述发光元件的发光量相应的电压,并且输出表示所述发光元件更明亮地发光这一情况的过电流检测信号。

附图说明

图1是表示具备一实施方式的半导体电路的半导体系统的概略构成的框图。

图2是表示图1的隔离放大器的内部构成的一个例子的框图。

图3是表示具备一比较例的半导体电路的半导体系统的概略构成的框图。

图4是表示一比较例的隔离放大器的内部构成的框图。

具体实施方式

以下,参照附图,对半导体电路以及半导体系统的实施方式进行说明。以下,以半导体电路以及半导体系统的主要的构成部分为中心进行说明,但半导体电路以及半导体系统中可以存在未图示或者未说明的构成部分、功能。以下的说明并不排除未图示或者未说明的构成部分、功能。

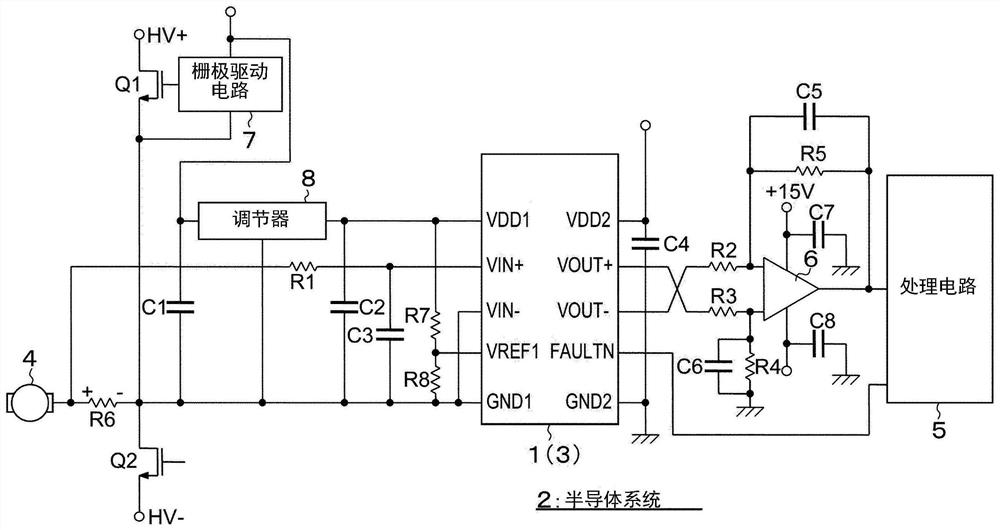

图1是表示具备一实施方式的半导体电路1的半导体系统2的概略构成的框图。图1的半导体电路1具有隔离放大器3。隔离放大器3以电绝缘的状态检测流经控制对象的电流,转换为电压并输出。在本说明书中,对控制对象是马达4的例子进行说明,但控制对象只要具有流过电流的电路即可,并不一定限定于马达4。

图1的半导体系统2具备控制马达4的处理电路5。处理电路5基于流过马达4的电流,对控制马达4的控制信号进行反馈控制。通过该控制信号,控制流过马达4的电流。处理电路5能够由MPU、ASIC或者DSP等构成。除此之外,图1的半导体系统2具备上述隔离放大器3、使隔离放大器3的输出信号放大的放大器6、驱动马达4的高压侧晶体管Q1以及低压侧晶体管Q2、控制高压侧晶体管Q1的栅极电压的栅极驱动电路7、生成隔离放大器3的电源电压VDD1的调节器8、电阻R1~R6、以及电容器C1~C8。

从处理电路5输出的控制信号被输入到栅极驱动电路7。栅极驱动电路7基于控制信号来驱动高压侧晶体管Q1的栅极。在图1中,虽然省略,但驱动低压侧晶体管Q2的栅极的未图示的栅极驱动电路7也由来自处理电路5的控制信号控制。

通过来自处理电路5的控制信号,使高压侧晶体管Q1与低压侧晶体管Q2接通或者断开,从而控制向马达4供给的电流与其方向。

在马达4的一端与接地节点GND1之间连接有分流电阻R6,流经马达4的电流流入分流电阻R6。由此,分流电阻R6的两端电压成为与流经马达4的电流相应的电压。该电压经由电阻R1被输入到隔离放大器3的VIN+端子。隔离放大器3的VIN-端子连接于接地节点GND1。

由调节器8调整后的电压作为电源电压VDD1输入到隔离放大器3。隔离放大器3以电绝缘的状态检测输入到VIN+的电压,差动地从VOUT+与VOUT-输出与流经马达4的电流相应的电压。它们的差动的输出电压经由电阻R2、R3被输入到放大器6。放大器6将从隔离放大器3输出的差动的输出电压放大,并向处理电路5输入。

图2是表示图1的隔离放大器3的内部构成的一个例子的框图。图2的隔离放大器3具备一次电路11与二次电路12。一次电路11根据流经马达4的电流使发光元件13发光。二次电路12被从一次电路11电绝缘,输出与发光元件13的发光量相应的电压。

一次电路11具有第一比较器14、第一电压控制器15、以及第二电压控制器16。第一比较器14判定与流经马达4的电流相应的电压是否超过第一基准电压VREF1。第一基准电压VREF1例如由外置的电阻R7、R8所构成的电阻分压电路17生成。通过将电阻R7、R8外置于图1的半导体电路1,使得用户能够任意地设定第一基准电压VREF1的电压电平。图1的半导体电路1具有外部连接端子TL1,以能够外置电阻R7、R8。另外,在使第一基准电压VREF1为固定的电压的情况下,也可以在图1的半导体电路1内设置用于生成第一基准电压VREF1的基准电压产生电路。

第一基准电压VREF1被设定为用于检测过电流流过马达4这一情况的电压电平。流经马达4的电流越多,分流电阻R6的两端电压越大,一次电路11的VIN+端子的电压越大。第一比较器14在VIN+端子的电压超过第一基准电压VREF1时,检测为过电流,例如将输出电平设为高电压。

第一电压控制器15在利用第一比较器14判定为超过第一基准电压VREF1时,将发光元件13的一端侧电压(阴极电压)控制为发出比判定为未超过第一基准电压VREF1时更大的发光量的光。第一电压控制器15例如具有带接通/断开功能的恒流电路(电流切换电路)18。该恒流电路18的一端连接于发光元件13的阴极,另一端连接于接地节点GND1。若利用第一比较器14判定为超过第一基准电压VREF1,则恒流电路18从发光元件13的阴极向接地节点GND1流过恒流。由此,发光元件13流过比通常更多的阴极电流,因此更明亮地发光。另一方面,若利用第一比较器14判定为未超过第一基准电压VREF1,则恒流电路18使恒流输出停止。由此,来自发光元件13的阴极的电流仅流向后述的第二电压控制器16,发光元件13比恒流电路18流过恒流的情况更暗地点亮。

第二电压控制器16例如具有ΔΣADC21、编码器22、驱动器23、时钟生成器24、以及基准电压生成器25。ΔΣADC21与由时钟生成器24生成的时钟信号同步地将与流经马达4的电流相应的电压转换为数字信号。编码器22对由ΔΣADC21转换后的数字信号进行编码。驱动器23基于编码器22的输出信号,生成发光元件13的阴极电压。与流经马达4的电流相应的电压被ΔΣADC21转换为数字信号,并被编码器22编码。驱动器23基于编码器22的输出信号,控制发光元件13的阴极电压。发光元件13以与阴极电压相应的发光量、即与流经马达4的电流相应的发光量发光。此时,如上述那样,若第一电压控制器15内的恒流电路18流过恒流,则发光元件13的阴极电流增大,发光元件13更明亮地发光。

如此,发光元件13根据第一电压控制器15内的恒流电路18是否流过恒流而使发光强度变化。

图2的隔离放大器3内的二次电路12具有光检测器31、跨阻抗放大器(TIA)32、第二比较器33、第三比较器34、缓冲器35、解码器36、时钟恢复电路37、基准电压生成器38、1比特DAC39、以及低通滤波器(LPF)40。第二比较器33、解码器36、时钟恢复电路37、基准电压生成器38、1比特DAC39以及低通滤波器40构成了第三电压控制器。在向二次电路12输入的电源电压VDD2与接地节点GND2之间连接有电容器C4。

光检测器31输出与发光元件13的发光量相应的电流。光检测器31与发光元件13电绝缘,接收由发光元件13发出的光并进行光电转换,输出光电转换后的电流。

跨阻抗放大器32将从光检测器31输出的电流转换为电压。从跨阻抗放大器32输出的电压被输入到第二比较器33与第三比较器34。第二比较器33判定从跨阻抗放大器32输出的电压是否超过了第二基准电压。第三比较器34判定从跨阻抗放大器32输出的电压是否超过了比第二基准电压高的第三基准电压,若判定为超过第三基准电压,则输出过电流检测信号。第二基准电压与第三基准电压可以在图1的半导体电路1内生成,也可以由外置的电阻分压电路生成。

第二比较器33的输出信号被输入到解码器36。解码器36基于第二比较器33的输出信号进行解码处理。该解码处理是用于将第二电压控制器16内的编码器22编码后的信号恢复到编码前的信号的处理。

1比特DAC39将由解码器36解码后的信号转换为模拟信号。低通滤波器40将从1比特DAC39输出的模拟信号所含的不必要的频率成分去除,并从输出端子输出差动电压VOUT+与VOUT-。该差动电压被输入到图1的放大器6。

第三比较器34是为了检测出马达4中流经过电流这一情况而设置的。若马达4中流经过电流,则如上述那样,发光元件13更明亮地发光。因此,流经二次电路12内的光检测器31的电流变大,跨阻抗放大器32的输出电压增大。由此,向第三比较器34输入的跨阻抗放大器32的输出电压变得比第三基准电压大,第三比较器34的输出信号成为高电压。第三比较器34的输出信号经由缓冲器35而从图1的半导体电路1的FAULTN端子输出。FAULTN端子是通知过电流检测的端子,例如在马达4中流经过电流时成为高电压。由此,通过对图1的半导体电路1的FAULTN端子的电压进行监视,能够迅速地掌握马达4中流经过电流。

图3是表示具备一比较例的半导体电路50的半导体系统51的概略构成的框图。若将图3与图1比较,则图3的半导体电路50内的隔离放大器52不具有VREF1端子,也不具备连接于该VREF1端子的电阻带来的电阻分压电路17。除此以外,图1与图3的半导体电路1为同样构成。

图4是表示一比较例的隔离放大器52的内部构成的框图。若将图4与图2比较,则图4的隔离放大器52内的一次电路11不具备第一比较器14。另外,图4的隔离放大器52内的二次电路12不具备第三比较器34与缓冲器35,但除此以外的构成与图2相同。

图4的隔离放大器52由解码器36与1比特DAC39来检测与流经马达4的电流相应的电压,能够由这些解码器36与1比特DAC39检测出马达4中流经过电流这一情况。然而,解码器36与1比特DAC39的处理花费时间,因此判断是否为过电流将花费时间。

与此相对,在图2的隔离放大器3中,若马达4中流经过电流,则发光元件13会更明亮地发光,并且若由第三比较器34检测出发光元件13更明亮地发光,则使FAULTN端子例如转变为高电压。由此,无需进行图2那样的解码处理、D/A转换处理,就能够迅速地使FULTN端子的电压电平转变,能够迅速地进行过电流检测。

另外,图4中未图示出相当于图2的第二比较器33的部件,但实际上图4中也设有相当于第二比较器33的部件,在图4中仅是省略而已。由此,图2与图4的二次电路12的构成上的不同点是图4中不具有第三比较器34与缓冲器35。

如此,在本实施方式中,在一次电路11内设置第一比较器14,并且在二次电路12内设置第三比较器34与缓冲器35,因此若马达4中流经过电流,则能够使发光元件13更明亮地发光,并且由第三比较器34检测出发光元件13更明亮地发光这一情况,并从FAULTN端子输出。由此,能够迅速地检测马达4中流经过电流。

另外,本实施方式与一比较例相比,仅仅是在一次电路11内追加第一比较器14、并且在二次电路12内追加第三比较器34的简易的电路变更即可,因此设计变更较容易。而且,本实施方式利用外置的电阻,从而用户能够任意地设定过电流的电流电平,因此能够应用于各种用途,通用性变高。

虽然说明了本发明的几个实施方式,但这些实施方式是作为例子而提出的,并不意图限定发明的范围。这些新的实施方式能够以其他各种方式实施,在不脱离发明的主旨的范围内能够进行各种省略、替换、变更。这些实施方式及其变形包含在发明的范围及主旨中,并且包含在权利要求书所记载的发明与其等效的范围内。

- 半导体集成电路系统、半导体集成电路、操作系统和半导体集成电路的控制

- 半导体集成电路、包括半导体集成电路的系统设备及半导体集成电路控制方法