一种多参数可调节高速伪随机码驱动源装置

文献发布时间:2023-06-19 10:24:22

技术领域

本发明涉及通信仪器设计技术领域,特别是一种多参数可调节高速伪随机码驱动源装置。

背景技术

伪随机码在扩频通信、光纤通信、无线通信等技术领域中起着重要的作用。目前,市场上应用的伪随机码射频驱动源大多源自国外电子企业,相当一部分的国内通信实验设备,要么没有伪随机码发生电路,要么传输速率慢,要么参数不可调。因此,研发一种多参数可调节高速伪随机码驱动源装置就变的相当必要。

发明内容

本发明的目的在于提供一种传输速率高、能够动态配置频率、m序列位宽、集成度高、应用范围广、成本低的伪随机码驱动源装置。

实现本发明目的的技术解决方案为:一种多参数可调节高速伪随机码驱动源装置,包括加电控制模块、时钟管理模块和嵌入式系统;

所述加电控制模块包括CPLD、数字晶振、第一开关电源和5个低压差线性稳压器;

所述时钟管理模块包括温补晶体振荡器、第二开关电源和时钟扇出缓冲器;

所述嵌入式系统包括FPGA主芯片、串行FLASH、RS422通信电路、LVDS接口和标准LVTTL驱动电路;

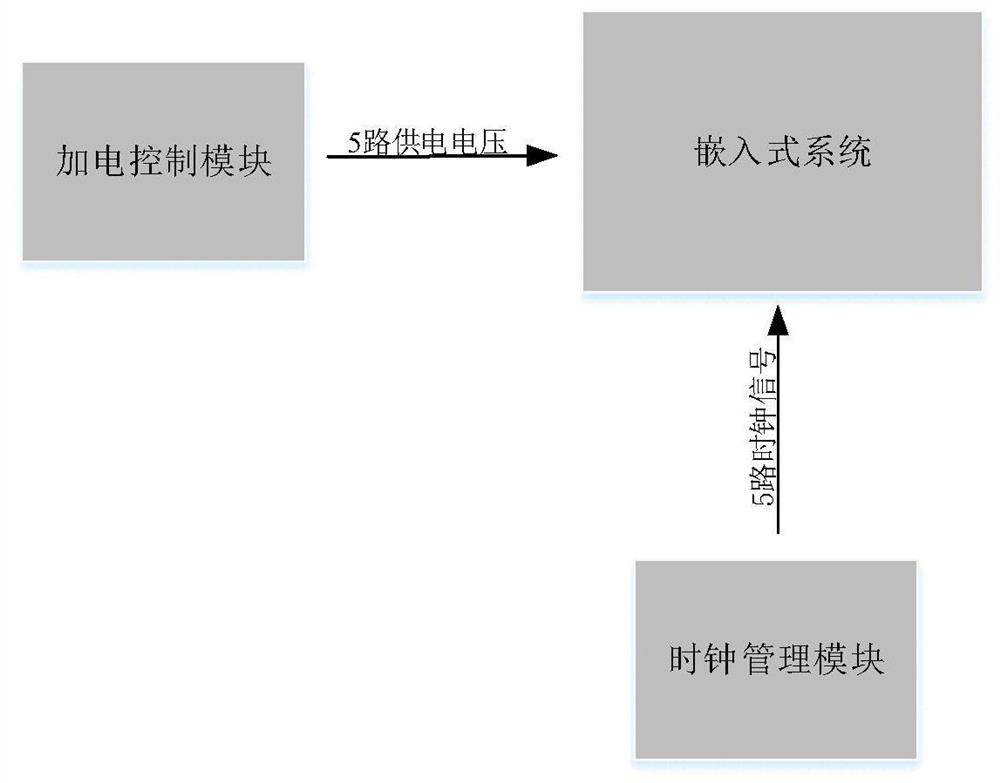

所述加电控制模块为所述嵌入式系统提供五路供电电压,所述时钟管理模块为所述嵌入式系统提供五路时钟信号。

进一步地,所述嵌入式系统包括FPGA主芯片、串行FLASH、RS422通信电路、LVDS接口和标准LVTTL驱动电路,其中:

FPGA主芯片内部包含一个片上系统,串行FLASH、RS422通信电路、LVDS接口和标准LVTTL驱动电路构成了FPGA主芯片的外设电路;所述FPGA主芯片采用Intel公司Cyclone10GX系列的10CX105YF780I5G,用于搭建片上系统SOPC;芯片内部含有多路串行收发器,收发器具有以下特点:支持速率最高达到12.5Gbps,具有用户可配置小数综合能力的ATX发送PLL,发送器预加重和去加重,单个收发器通道的动态重配置;使用串行收发器实现m序列伪随机码的传输,利用收发器动态配置的特性实现频率、m序列位宽的调节;

所述串行FLASH拥有512M的存储空间,使用QSPI接口,默认为FPGA主芯片的上电配置器件,在使用Nios II软核时,作为软件代码的存储空间;

所述RS422通信电路,用于接收上位机软件发送的报文和给上位机发送握手信号,实现驱动源参数的控制;通信端口属性为波特率115200bps/S、无校验位、8位数据位和1位停止位;

所述LVDS接口选用FPGA主芯片串行收发器中发送器的专用高速差分I/O,用于发送高速伪随机码信号;

所述标准LVTTL驱动电路将外部设备提供的标准TTL信号转换成3V的LVTTL信号,在装置使用过程中能够替代RS422通信电路,接收外部的控制信号。

进一步地,所述FPGA主芯片包括核心电压电源VCC、外设电路和收发器架构接口电源VCCP、配置管脚电源VCCPGM、嵌入式存储器电源VCCERAM、电池备用电源VCCBAT、可编程功耗技术和I/O预驱动器的电源VCCPT、I/O缓冲器电源VCCIO、PLL模拟电源VCCA_PLL、收发器bank电源VCCT_GXB和VCCR_GXB、模拟级发送缓冲电源VCCH_GXB;

整个电源轨被分成五组,包括VCC/VCCP/VCCERAM、VCCT_GXB/VCCR_GXB、VCCPT/VCCA_PLL/VCCH_GXB/VCCBAT、VCCPGM/VCCIO_1.8V、VCCIO_3V;其中VCCIO_1.8V和VCCIO_3V分别是1.8V和3.3V的I/O缓冲器电源,各个电源组满足加电序列。

进一步地,所述加电控制模块包括CPLD、数字晶振、第一开关电源和5个低压差线性稳压器,其中:

所述CPLD选用Intel公司的EPM7064AETI44-7,使用一个计数器产生5个低压差线性稳压器的使能信号,从而控制电源的加电顺序;

所述数字晶振采用中电熊猫公司的ZCC-T-E-20M000-ASHN芯片,为CPLD提供20MHz稳定低噪的时钟信号;

所述低压差线性稳压器选用ADI公司的ADP1741,最大输出电流2A,具有软启动特性,提供可调输出电压选项0.75V~3.3V;本装置中ADP1741连接1nF的外部软启动电容,对启动进行编程设置,启动时间设置为1ms。

进一步地,所述时钟管理模块为所述嵌入式系统提供五路时钟信号,包括两路差分100MHz全局时钟GlobalCLK、两路差分100MHz串行收发器的参考时钟REFCLK和一路单端100MHz收发器的校准时钟CLKUSR;

包括温补晶体振荡器、第二开关电源和时钟扇出缓冲器,其中:

温补晶体振荡器的型号为SFT5S-LS6HB-100M,产生100MHz时钟信号;

时钟扇出缓冲器选用ADI公司的ADCLK846,能够选LVDS/CMOS输出,包括6路LVDS或者12路CMOS输出,两条控制线路用于确定固定模块输出是LVDS输出还是CMOS输出。

进一步地,所述FPGA主芯片内部包含一个片上系统,该片上系统通过QuartusPrime Pro18.1软件的系统集成设计工具Platform Designer完成搭建,片上系统包括NiosII软核处理器、UART、伪随机码发生模块、Reset Controller模块、Cyclone 10GX NativePHY模块、PLL 1.5G模块、PLL 2G模块、PLL 5G模块和PLL 10G模块,其中:

(1)所述Nios II软核处理器是整个片上系统的控制中枢,具有以下特性:

1)32位指令集

2)32位数据位宽

3)32个通用寄存器

4)32个外部中断源

5)2GB寻址空间

Nios II软核处理器通过UART接收来自外部的RS422指令信号,并且完成信号的解析,转换成对应的频率信息和m序列信息;指令信号解析完成之后,Nios II软核处理器控制伪随机码发生模块产生对应的并行m序列伪随机码流,并控制Cyclone10GX Native PHY模块完成收发器的重配置和重校准工作;

(2)所述Cyclone 10GX Native PHY模块用于配置和加载对应通道上的收发器,包括4种配置模式,并存储在4个profile文件中,该4个profile文件的特性如下:

1)profile0:1.5Gbps速率、16位数据接口宽度;

2)profile1:2Gbps速率、16位数据接口宽度;

3)profile2:5Gbps速率、32位数据接口宽度;

4)profile3:10Gbps速率、32位数据接口宽度;

(3)所述PLL 1.5G模块、PLL 2G模块、PLL 5G模块和PLL 10G模块,为Cyclone10GXNative PHY模块提供传输数据的时钟,PLL 1.5G模块、PLL 2G模块、PLL 5G模块和PLL 10G模块提供的参考时钟分别设置为750MHz、1GHz、2.5GHz、5GHz;

(4)所述Reset Controller模块为Cyclone 10GX Native PHY模块和PLL模块提供各个运行阶段的复位信号;

(5)所述伪随机码发生模块包括本原多项式查找表和线性反馈移位寄存器;

线性反馈移位寄存器用于产生伪随机数,由n个D触发器和若干个异或门组成,n个D触发器最多能够产生2

本原多项式查找表存储了1至32位宽m序列的本原多项式,16位宽和32位宽的m序列对应的本原多项式分别是f(x)=x

进一步地,片上系统的软件设计基于NIOS II集成开发环境,包括串口接收模块、命令解析模块和动态配置模块,其中:

串口接收模块用于配置串口,并接收串口信号,串口配置步骤如下:

1)清零状态寄存器;

2)读空接收寄存器中的无用值;

3)设置波特率为115200;

4)使能接收中断;

串口接收模块调用接收中断函数处理串口信号;

命令解析模块将接收到的串口信号转换成动态配置模块需要的profile文件和PLL的选择信号;

动态配置模块用于profile文件和PLL的重配置,PLL的重配置步骤如下:

1)保持Native PHY处于复位状态;

2)在Avalon MM总线上申请Native PHY接口权限;

3)读取地址0x117中的值;

4)往地址0x111写入对应的PLL配置信息;

profile文件的重配置步骤如下:

1)读取地址0x2中的值;

2)往地址0x340中写入对应的profile信息;

3)将地址0x100[1]和地址0x100[5]对应的rx_cal_en和tx_cal_en置为1;

4)执行收发器通道重校准命令;

5)释放收发器通道重校准总线;

清零Native PHY的复位信号。

本发明与现有技术相比,其显著优点在于:(1)传输速率高最高传输速率可以达到10Gbps;(2)基于以Nios II软核处理器为核心的嵌入式系统的硬件配置,实现了频率、m序列位宽的动态配置,弥补了现有技术的传输速率慢和参数不可调的缺陷;(3)应用范围广、集成度高、成本低、利润高,应用和市场需求前景广阔。

附图说明

图1为本发明多参数可调节高速伪随机码驱动源装置的原理框图。

图2为本发明多参数可调节高速伪随机码驱动源装置的具体结构框图。

图3为本发明中片上系统的结构框图。

图4为本发明中伪随机码发生模块的结构框图。

图5为本发明实施例中软件设计的结构框图。

具体实施方式

下面结合附图和具体实施例对本发明做进一步的详细说明。

如图1~2所示,一种多参数可调节高速伪随机码驱动源装置,包括加电控制模块、时钟管理模块和嵌入式系统;

所述加电控制模块为所述嵌入式系统提供五路供电电压,所述时钟管理模块为所述嵌入式系统提供五路时钟信号。

进一步地,所述嵌入式系统是整个装置的核心部分,包括FPGA主芯片、串行FLASH、RS422通信电路、LVDS接口和标准LVTTL驱动电路。其中,FPGA主芯片内部包含一个片上系统,串行FLASH、RS422通信电路、LVDS接口和标准LVTTL驱动电路构成了其基本外设电路。

FPGA主芯片采用Intel公司Cyclone 10GX系列的10CX105YF780I5G,该芯片采用TSMC的20nm工艺技术,内部集成了32位高性能Nios II软核处理器,可以用于搭建片上系统(SOPC)。芯片内部含有多路低功耗串行收发器,收发器具有以下特点:支持速率最高达到12.5Gbps,具有用户可配置小数综合能力的ATX发送PLL,发送器预加重和去加重,单个收发器通道的动态重配置。本装置使用了串行收发器实现m序列伪随机码的高速传输,利用收发器动态配置的特性实现了频率、m序列位宽的调节。

FPGA主芯片电气特性复杂,包括核心电压电源VCC、外设电路和收发器架构接口电源VCCP、配置管脚电源VCCPGM、嵌入式存储器电源VCCERAM、电池备用电源VCCBAT、可编程功耗技术和I/O预驱动器的电源VCCPT、I/O缓冲器电源VCCIO、PLL模拟电源VCCA_PLL、收发器bank电源VCCT_GXB和VCCR_GXB、模拟级发送缓冲电源VCCH_GXB。

整个电源轨被分成五组,包括VCC/VCCP/VCCERAM、VCCT_GXB/VCCR_GXB、VCCPT/VCCA_PLL/VCCH_GXB/VCCBAT、VCCPGM/VCCIO_1.8V、VCCIO_3V。其中VCCIO_1.8V和VCCIO_3V分别是1.8V和3.3V的I/O缓冲器电源。各个电源组需要满足严格的加电序列。

串行FLASH拥有512M的存储空间,使用QSPI接口,默认作为FPGA主芯片的上电配置器件,在使用Nios II软核时,作为软件代码的存储空间,让Nios II能够顺畅运行。

RS422通信电路负责接收上位机软件发送的报文和给上位机发送握手信号,实现驱动源参数的控制。通信端口属性为波特率115200bps/S、无校验位、8位数据位和1位停止位。

LVDS接口选用FPGA主芯片串行收发器中发送器的专用高速差分I/O,用于发送高速伪随机码信号。

标准LVTTL驱动电路将外部设备提供的标准的TTL信号转换成3V的LVTTL信号,在装置使用过程中可以替代RS422通信电路,接收外部的控制信号,简化使用难度,具有很好的可扩展性。

进一步地,所述加电控制模块为嵌入式系统提供五路精准可控的供电电压,以满足Cyclone 10GX的加电要求,它包括CPLD、数字晶振、第一开关电源、5个低压差线性稳压器。

CPLD选用Intel公司的EPM7064AETI44-7,它使用一个计数器产生5个低压差线性稳压器的使能信号,从而控制电源的加电顺序。

数字晶振采用中电熊猫公司的ZCC-T-E-20M000-ASHN芯片,为CPLD提供20MHz稳定低噪的时钟信号。

低压差线性稳压器选用ADI公司的ADP1741,最大输出电流2A,具有软启动特性,提供可调输出电压选项0.75V~3.3V。本装置中ADP1741连接1nF的外部软启动电容,对启动进行编程设置,启动时间设置为1ms。

进一步地,所述时钟管理模块包括温补晶体振荡器、第二开关电源、时钟扇出缓冲器。它为嵌入式系统提供五路时钟信号,包括两路差分100MHz全局时钟GlobalCLK、两路差分100MHz串行收发器的参考时钟REFCLK和一路单端100MHz收发器的校准时钟CLKUSR。

温补晶体振荡器选用型号为SFT5S-LS6HB-100M,产生100MHz时钟信号。技术指标如下:

功率:>10dBm

谐波:<-25dBc

杂波:<-70dBc

时钟扇出缓冲器选用ADI公司的ADCLK846,可选LVDS/CMOS输出,多达6路LVDS或者12路CMOS输出,两条控制线路用于确定固定模块输出是LVDS输出还是CMOS输出。

进一步地,所述伪随机码驱动源装置通过Quartus Prime Pro18.1软件的系统集成设计工具Platform Designer完成片上系统的搭建,图3为片上系统结构框图,包括NiosII软核处理器、UART、伪随机码发生模块、Reset Controller模块、Cyclone 10GX NativePHY模块、PLL 1.5G模块、PLL 2G模块、PLL 5G模块和PLL 10G模块。

Nios II软核处理器是整个片上系统的控制中枢,它具有以下特性:

1)32位指令集

2)32位数据位宽

3)32个通用寄存器

4)32个外部中断源

5)2GB寻址空间

Nios II软核处理器通过UART接收来自外部的RS422指令信号,并且完成信号的解析,转换成对应的频率信息和m序列信息。指令信号解析完成之后,Nios II软核处理器控制伪随机码发生模块产生对应的并行m序列伪随机码流,并控制Cyclone10GXNative PHY模块完成收发器的重配置和重校准工作。

Cyclone 10GX Native PHY模块用于配置和加载对应通道上的收发器。本装置中设计了4种配置模式,并存储在4个profile文件中,以便于动态配置的时候调用。以下是4个profile文件的主要特性:

1)profile0:1.5Gbps速率、16位数据接口宽度

2)profile1:2Gbps速率、16位数据接口宽度

3)profile2:5Gbps速率、32位数据接口宽度

4)profile3:10Gbps速率、32位数据接口宽度

片上系统包含了4个PLL模块,分别是PLL 1.5G模块、PLL 2G模块、PLL 5G模块和PLL 10G模块,它们为Cyclone 10GX Native PHY模块提供传输数据的时钟。由于收发器采用DDR的方式传输数据,即时钟的上升沿和下降沿均传输数据,所以PLL 1.5G模块、PLL 2G模块、PLL 5G模块和PLL 10G模块提供的参考时钟分别设置为750MHz、1GHz、2.5GHz、5GHz。

Reset Controller模块为Cyclone 10GX Native PHY模块和PLL模块提供各个运行阶段的复位信号。

图4为伪随机码发生模块结构框图,包括本原多项式查找表和线性反馈移位寄存器(LFSR)。

线性反馈移位寄存器用于产生伪随机数,它是由n个D触发器和若干个异或门组成的,n个D触发器最多可以产生2

本原多项式查找表存储了1至32位宽m序列的本原多项式。在本设计中,16位宽和32位宽的m序列对应的本原多项式分别是f(x)=x

整个软件设计基于NIOS II集成开发环境,图5为软件设计结构框图,包括串口接收模块、命令解析模块和动态配置模块。

串口接收模块用于配置串口,并接收串口信号,首先,串口配置步骤如下:

1)清零状态寄存器

2)读空接收寄存器中的无用值

3)设置波特率为115200

4)使能接收中断

串口接收模块调用接收中断函数处理串口信号。

命令解析模块将接收到的串口信号转换成动态配置模块需要的profile文件和PLL的选择信号。

动态配置模块负责完成profile文件和PLL的重配置,PLL的重配置步骤如下:

1)保持Native PHY处于复位状态

2)在Avalon MM总线上申请Native PHY接口权限

3)读取地址0x117中的值

4)往地址0x111写入对应的PLL配置信息

profile文件的重配置步骤如下:

1)读取地址0x2中的值

2)往地址0x340中写入对应的profile信息

3)将地址0x100[1]和地址0x100[5]对应的rx_cal_en和tx_cal_en置为1

4)执行收发器通道重校准命令

5)释放收发器通道重校准总线

6)清零Native PHY的复位信号

本发明提供的多参数可调节高速伪随机码驱动源装置,最高传输速率可以达到12.5Gbps,它基于以Nios II软核处理器为核心的嵌入式系统的硬件配置,实现了频率、m序列位宽的动态配置,从而弥补了现有技术的传输速率慢和参数不可调的缺陷,整个装置应用范围广、集成度高、成本低、利润高,应用和市场需求前景广阔。

- 一种多参数可调节高速伪随机码驱动源装置

- 一种多路反馈全光异或逻辑高速超长伪随机码发生器