一种防护型半导体器件

文献发布时间:2023-06-19 10:29:05

技术领域

本公开涉及半导体器件,尤其涉及关于高压和/或大功率的一种防护型半导体器件。

背景技术

半导体防护器件广泛应用于消费电子、白色家电、工业控制、电力电子以及国防电子等领域。作为瞬间释放多余电压或电流的电子元器件,在正常状态下,防护器件仅仅是作为主电路的辅助元件而不参与或影响主电路的正常电路功能;只有当防护器件两端的电压或流过防护器件的电流超出一定的阈值时,防护器件进入击穿钳位或闩锁的工作状态,让电路中多余的能量从旁路的防护器件泄放,从而达到保护主电路的目的。

由于防护器件多为被动元件,无法提前或延迟控制其工作,因此不适合某些需主动泄放电路能量的应用领域;其次,特别在高电压或大功率防护的应用场合,将对防护型半导体器件的响应速度、鲁棒性和可靠性提出及其严苛的要求,而现有的防护器件很难胜任这些领域的应用。主要原因是半导体器件往往是由成千上万个最小元胞单位并联排布而成,受到工艺偏差、引线寄生参数等因素的影响,极难实现器件内所有元胞一致工作,因此极大的影响器件的动态性能并降低器件的安全工作区,甚至引起器件失效。

发明内容

本公开提供了一种防护型半导体器件,其技术目的是:在高电压或大功率下,提高防护型半导体器件的响应速度、增强其鲁棒性和可靠性。

本公开的上述技术目的是通过以下技术方案得以实现的:

一种防护型半导体器件,包括第一第一导电类型半导体区,所述第一第一导电类型半导体区的底部设有第一第二导电类型半导体区,所述第一第二导电类型半导体区底部连接有阳极;

所述第一第一导电类型半导体区的顶部设有第二第二导电类型半导体区,所述第二第二导电类型半导体区内设有沿水平方向变化掺杂剂量的第二第一导电类型半导体区;

所述第二第二导电类型半导体区的一侧设有触发区、另一侧设有阴极,所述触发区包括部分的所述第一第一导电类型半导体区、部分的所述第二第二导电类型半导体区及部分的所述第二第一导电类型半导体区;所述阴极与部分的所述第二第二导电类型半导体区和部分的所述第二第一导电类型半导体区都形成欧姆接触;

所述触发区内还设有至少一个触发电极,所述触发电极与部分的所述第二第二导电类型半导体区形成欧姆接触;或

所述触发电极与部分的所述第一第一导电类型半导体区、部分的所述第二第二导电类型半导体区及部分的所述第二第一导电类型半导体区之间都通过介质相隔离。

进一步地,所述第二第二导电类型半导体区是:

一个沿水平方向掺杂剂量均相同的第二第二导电类型半导体区;或

一个沿水平方向变化掺杂剂量的第二第二导电类型半导体区。

进一步地,所述第二第一导电类型半导体区的杂质的掺杂剂量沿着从所述触发区到所述阴极的方向逐渐增加;

所述第二第二导电类型半导体区沿水平方向变化掺杂剂量时,所述第二第二导电类型半导体区的杂质的掺杂剂量沿着从所述触发电极到所述阴极的方向逐渐增加。

进一步地,所述触发区包括平面栅MOSFET结构和沟槽删MOSFET结构;

所述触发区为所述平面栅MOSFET结构时,所述平面栅MOSFET结构包括:部分的所述第一第一导电类型半导体区成为所述平面栅MOSFET结构的漏区、部分的所述第二第二导电类型半导体区成为所述平面栅MOSFET结构的源体区,及部分的所述第二第一导电类型半导体区成为所述平面栅MOSFET结构的源区,存在第一介质沿水平方向覆盖部分的所述第一第一导电类型半导体区、部分的所述第二第二导电类型半导体区及部分的所述第二第一导电类型半导体区,所述第一介质成为所述平面栅MOSFET结构的第一栅介质,所述触发电极覆盖所述第一栅介质,所述触发电极成为所述平面栅MOSFET结构的栅极;

所述触发区为所述沟槽删MOSFET结构时,所述沟槽删MOSFET结构包括:部分的所述第一第一导电类型半导体区成为所述沟槽栅MOSFET结构的漏区、部分的所述第二第二导电类型半导体区成为所述沟槽栅MOSFET结构的源体区,及部分的所述第二第一导电类型半导体区成为所述沟槽栅MOSFET结构的源区,存在第二介质沿竖直方向覆盖部分的所述第一第一导电类型半导体区、部分的所述第二第二导电类型半导体区及部分的所述第二第一导电类型半导体区,所述第二介质成为所述沟槽栅MOSFET结构的第二栅介质,所述触发电极与所述第二栅介质直接接触,所述触发电极成为所述沟槽栅MOSFET结构的栅极;

进一步地,所述第二第二导电类型半导体区顶部设有至少两个MIS(金属-介质-半导体)结构,对每个所述MIS结构施加不同的偏置电压从而得到各个所述MIS结构的反型电荷密度,从而获得沿水平方向变化掺杂剂量的所述第二第一导电类型半导体区。

进一步地,所述阳极还连接有第三第一导电类型半导体区,所述第三第一导电类型半导体区与所述第一第二导电类型半导体区相接触,所述第三第一导电类型半导体区还与所述第一第一导电类型半导体区相接触。

进一步地,在所述第一第一导电类型半导体区底部还设有第四第一导电类型半导体区,且所述第四第一导电类型半导体区与所述第一第二导电类型半导体区相接触。

本公开的有益效果在于:本公开所述的防护型半导体器件包括第一第一导电类型半导体区,所述第一第一导电类型半导体区的底部设有第一第二导电类型半导体区,所述第一第二导电类型半导体区底部连接有阳极。所述第一第一导电类型半导体区的顶部设有第二第二导电类型半导体区,所述第二第二导电类型半导体区内设有沿水平方向变化掺杂剂量的第二第一导电类型半导体区。

由于所述第二第一导电类型半导体区为变化掺杂的半导体区,与第二第二导电类型半导体区之间能够形成多次的电子-空穴-电子-空穴循环往复,从而在阳极A与阴极K之间形成强大的电流,这个过程只需要十几纳秒。因此,当外电路有浪涌电流出现时,通过主动控制触发极T即可在阳极A和阴极K之间形成极大电流的通道,极大地提升器件过浪涌电流的能力,从而实现对半导体器件的主动防护,提高其响应速度、增强其鲁棒性和可靠性。

附图说明

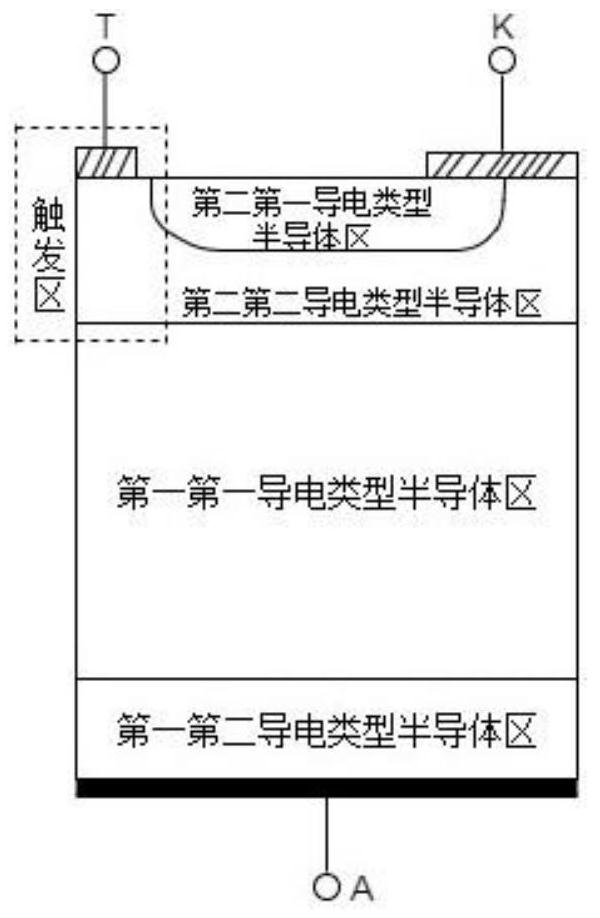

图1为本发明所述的防护型半导体器件的结构示意图;

图2为防护型半导体器件的一个元胞单元的结构示意图;

图3为多段掺杂来实现N-VLD和P-VLD的结构示意图;

图4为触发区采用平面栅MOSFET结构的结构示意图;

图5为触发区采用沟槽栅MOSFET结构的结构示意图;

图6为采用多个MIS结构来实现N-VLD的结构示意图;

图7为采用平面栅MOSFET结构作为触发区,并且N-VLD区部分采用MIS结构的结构示意图;

图8为采用沟槽栅MOSFET结构作为触发区,并且N-VLD区部分采用MIS结构的结构示意图;

图9为采用阳极短路方法的结构示意图;

图10为增加缓冲层的结构示意图。

具体实施方式

下面将结合附图对本公开技术方案进行详细说明。在本申请的描述中,需要理解地是,术语“第一”、“第二”、“第三”、“第四”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量,仅用来区分不同的组成部分。在本申请的描述中,第一导电类型包括N型和P型,第二导电类型同样包括N型和P型,当第一导电类型为N型时,第二导电类型则为P型;当第一导电类型为P型时,第二导电类型则为N型。

另外,术语“上”、“下”、“前”、“后”、“左”、“右”、“顶部”、“底部”、“侧壁”、“竖直”、“水平”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

附图和说明被认为在本质上是示出性的,而不是限制性的。在图中,结构相似的单元以相同标号表示。另外,为了理解和便于描述,附图中示出的每个组件的尺寸和厚度是任意示出的,但是本申请不限于此。

在附图中,为了清晰、理解和便于描述,夸大设备、系统、组件、电路的配置范围。将理解的是,当组件被称作“在”另一组件“上”时,所述组件可以直接在所述另一组件上,或者也可以存在中间组件。

另外,在说明中,除非明确地描述为相反的,否则词语“包括”将被理解为意指包括所述组件,但是不排除任何其他组件。此外,在说明书中,“在......上”意指位于目标组件上方或者下方,而不意指必须位于基于重力方向的顶部上。

为更进一步阐述本申请为达成预定发明目的所采取的技术手段及功效,以下结合附图及具体实施例,对依据本申请提出的高压和/或大功率的主动防护型半导体器件,其具体实施方式、结构、特征及其功效以下将详细说明。

本发明所述的防护型半导体器件为一种高耐压的防护型半导体三端器件,具有独立的控制端口。图1为本发明所述的防护型半导体器件的结构示意图,如图1所示,该防护型半导体器件包括第一第一导电类型半导体区,该第一第一导电类型半导体区的底部设有第一第二导电类型半导体区,第一第二导电类型半导体区底部连接有阳极A。

第一第一导电类型半导体区的顶部设有第二第二导电类型半导体区,第二第二导电类型半导体区内设有沿水平方向变化掺杂剂量的第二第一导电类型半导体区。第二第二导电类型半导体区的一侧设有触发区、另一侧设有阴极K,触发区包括部分的第一第一导电类型半导体区、部分的第二第二导电类型半导体区及部分的第二第一导电类型半导体区;阴极与K部分的第二第二导电类型半导体区和部分的第二第一导电类型半导体区都形成欧姆接触。

触发区内还设有至少一个触发电极T,该触发电极T与部分的第二第二导电类型半导体区形成欧姆接触(图1所示的触发区)或该触发电极与部分的第一第一导电类型半导体区、部分的第二第二导电类型半导体区及部分的第二第一导电类型半导体区之间都通过介质相隔离(图4所示的触发区)。

图2即为防护型半导体器件中一个元胞单元的具体实施例的结构示意图,即该防护型半导体器件至少包括一个元胞单元。图2中,半导体器件包括第一导电类型为N型的半导体衬底002(n区002),其底部设置有第二导电类型为P型的掺杂区域001,称为阳极区,该P型掺杂区域001(P区001)接触阳极金属层A。半导体衬底002的顶部设置有沿横向变化掺杂的P型半导体区(P-VLD),称为P型基区,在变化掺杂的P型半导体区内设置有沿横向变化掺杂的N型半导体区(N-VLD),在P-VLD区的一侧设置有触发区,在触发区内设置有触发电极T,触发电极T的金属层与P-VLD区形成欧姆接触。在P-VLD区的另一侧设置有阴极K,阴极K的金属层不仅与部分的P-VLD区形成欧姆接触,还与部分的N-VLD区形成欧姆接触。图2虽以第一导电类型为N型,第二导电类型为P型为例,但第一导电类型为P型,第二导电类型为N型亦适用,以下皆同。

图2所示的防护型半导体器件的工作原理具体如下。在半导体器件被触发前,阳极A和阴极K之间加有正偏置电压V

半导体器件往往是由成千上万个可重复元胞的单元并联堆叠形成的,由图2所示的元胞单元通过并联堆叠的方式可形成一个半导体器件。然而,在实际情形中,由于受到工艺偏差、版图布线寄生参数以及其它诸多因素的影响,并联排布的每一个元胞无法保证绝对同步的工作状态,因此容易造成局部元胞的工作状态先于其它元胞而导致电流集中,极大地降低了器件抗浪涌冲击的能力,更严重的情形下则会导致器件的失效。为了让器件内每一个元胞达到同步工作的效果,本发明提出的主动防护型半导体器件设置了沿横向变化掺杂的P型半导体区(P-VLD)和沿横向变化掺杂的N型半导体区(N-VLD),其工作原理如下:

在器件被触发之后,触发极T和阴极K之间被灌入一定的触发电流IAK,并在P-VLD区内形成从T极向K极方向逐渐减小的横向电压降。显然,由P-VLD和N-VLD形成的PN结首先在靠近触发区的地方被触发导通,而在靠近阴极一侧的PN结并未进入正向导通状态,因此从阳极A到阴极K的电流通路主要集中在靠近触发区的一侧。本发明设置P-VLD区的受主杂质的掺杂剂量沿着从T极到K极的方向逐渐增加,因此P-VLD区内的横向压降也是非线性的,靠近触发区的横向压降最大,在靠近阴极K的地方横向压降最小,于是首先被触发导通的PN结内的空穴将在横向电压降的作用下快速向阴极K方向扩散,进而带动AK之间电流通路快速从触发区一侧向阴极区一侧扩散,从而达到快速均流的目的。本发明还设置N-VLD区的施主杂质的掺杂剂量沿着从T极到K极的方向逐渐增加,因此由P-VLD和N-VLD形成的PN结的非平衡载流子的注入效率将沿着从T极到K极的方向逐渐增加,当在由P-VLD和N-VLD形成的PN结首先在靠近触发区的地方被触发导通时,此处较低的非平衡载流子的注入效率限制了电流的急剧增加;更进一步,由于此时电流会沿横向流经N-VLD区,并在N-VLD区产生从T极向K极方向逐渐减小的横向电压降,该横向压降的存在反过来削弱了触发区附近PN结的正向压降,因此也限制了电流的急剧增加。一方面由于P-VLD区的作用让电流快速均流,另一方面由于N-VLD区的作用让先导通的PN结电流受限制,因此可以让并联排布的其它元胞有足够的时间进入与该元胞相同的工作状态,于是可以在很大程度上提高器件快速均流的目的,极大地提升器件过浪涌电流的能力。

作为具体实施例地,为了获得快速均流的电性能和工艺复杂度的折中,P-VLD区也可以采用一级分段方法,即P-VLD区所有区域都有相同的掺杂,如图8中的P-VLD区所示。

图3、图4、图5、图6及图7均展示了通过多段掺杂来实现N-VLD和P-VLD的结构示意图,为了理解和便于描述,图中的N1、N2、N3区以及P1、P2、P3区仅是作为示例,显然本申请不限于此。图3中,N1、N2、N3区掺杂剂量的关系为:N1区的掺杂剂量 图4为触发区采用平面栅MOSFET(Metal-Oxide-Semiconductor Field-EffectTransistor,金属-氧化物半导体场效应晶体管)结构的结构示意图,与图2的电流触发方法不同,图4采用电压控制触发,其工作原理如下。如图4所示,在部分的n区002的顶部,部分的P1区顶部以及部分的N1区顶部覆盖有介质区,在介质区顶部覆盖有触发电极T的导体,形成一个平面栅N-MOSFET,部分的n区002是该平面栅N-MOSFET的漏区,部分的P1区是该平面栅N-MOSFET的源体区,部分的N1区则成为该平面栅N-MOSFET的源区,电极T成为该平面栅N-MOSFET的栅极。当给触发极T施加一定的相对于阴极K的正电压V 图5则示出了采用沟槽栅MOSFET作为触发区的一种结构,如图5所示,在部分的n区002和部分的P1区的侧壁以及部分的N1区顶部设置有介质区,在介质区另一侧覆盖有触发电极T的导体,形成一个沟槽栅N-MOSFET,n区002是该沟槽栅N-MOSFET的漏区,部分的P1区是该沟槽栅N-MOSFET的源体区,部分的N1区则成为该沟槽栅N-MOSFET的源区,电极T成为该沟槽栅N-MOSFET的栅极。当给触发极T施加一定的相对于阴极K的正电压V 图6示出了采用多个MIS(Metal-Insulator-Semiconductor,金属-绝缘层-半导体)结构的反型电子层来实现N-VLD区的一种结构。与图3的不同之处在于,图6通过采用设置多个金属-介质层-半导体的MIS结构,并通过给各个MIS结构施加不同的偏置电压来获得不同剂量的反型电子层(各个MIS结构的反型电荷密度不同),从而获得等效为沿水平方向变化掺杂剂量的N型半导体区(N-VLD)。需要特别指出的是,由于不同的MIS结构是相互间隔的,因此图6在各MIS结构之间设置了n+区以便在电学上连通各MIS结构的反型电子层。图6的方法相比图3由于少了不同剂量的多次N区掺杂,因此工艺更为简单。 作为具体实施例地,图7则示出了采用平面栅MOSFET结构作为触发区,并且N-VLD区部分采用MIS结构的一种防护型半导体器件。 作为具体实施例地,图8示出了采用沟槽栅MOSFET结构作为触发区,并且N-VLD区部分采用MIS结构的一种防护型半导体器件。其中的P-VLD区采用一级分段方法(即P-VLD区各处的掺杂相同),以获得快速均流的电性能和工艺复杂度的折中。 图9是采用阳极短路的一种半导体结构,具体为:阳极金属不仅与P区001接触,还与N+区007(可以理解为第三第一导电类型半导体区)接触,从而形成阳极短路结构。图9所示的阳极短路结构可以让器件的耐压更高,反偏漏电流更小,还可以形成由P-VLD区、n区002和N+区007构成的体二极管,特别适合需要续流应用的场景。 与图9不同的是,图10在n区002底部增加了缓冲层008(即第四第一导电类型半导体区),即n-buffer层,n-buffer层的设置可以让器件耐压区电场接近梯形,从而在一定的击穿电压下使得耐压区n区002的厚度更小,以降低器件导通时的内阻,提升过流能力。 以上为本公开示范性实施例,本公开的保护范围由权利要求书及其等效物限定。

- 一种半导体器件的静电防护方法及半导体器件

- 一种电流防护型半导体器件