一种iSP信号的解码方法、解码系统

文献发布时间:2023-06-19 10:32:14

【技术领域】

本发明涉及图像传输技术领域,尤其涉及一种iSP信号的解码方法、解码系统。

【背景技术】

随着现代通信技术和多媒体技术的发展,人们对信号传输速率的需求越来越高。

最早的图像传输技术通常采用单端互连方式,传输速率低并且易受到干扰和噪声的影响;为了提高传输速率,后来多采用包含有源同步时钟的串行差分传输方式,但由于在传输过程中时钟信号与数据信号分别传输,容易导致各信号抖动不一致,破坏了接收数据信号与时钟信号之间的定时关系,因此传输速率虽然有所提高,但也很难超过1Gbps/通道;为了进一步提高传输速率,出现了iSP,是一种专门针对图像传输开发的数字接口标准,其支持多端口数据输出,最大传输速率高达3.6Gbps,然而由于iSP信号结构复杂,解码较为困难。

【发明内容】

为了解决上述技术问题,本发明提供一种iSP信号的解码方法、解码系统。

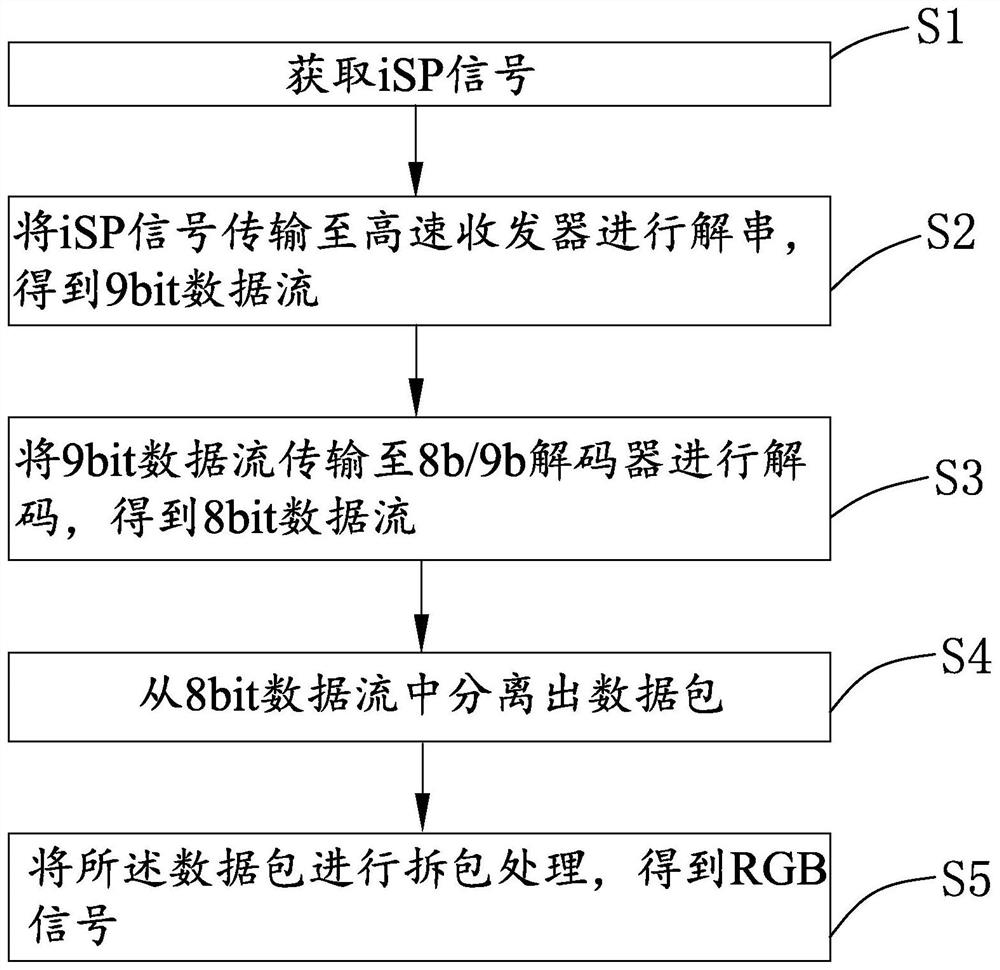

本发明提供的一种iSP信号的解码方法,其包括以下步骤:步骤S1,获取iSP信号;步骤S2,将所述iSP信号传输至高速收发器进行解串,得到9bit数据流;步骤S3,将所述9bit数据流传输至8b/9b解码器进行解码,得到8bit数据流;步骤S4,从所述8bit数据流中分离出数据包;步骤S5,将所述数据包进行拆包处理,得到RGB信号。

在本发明提供的iSP信号的解码方法的一种较佳实施例中,上述步骤S4具体为:将所述8bit数据流传输至解扰码器进行解扰处理,得到所述数据包。

在本发明提供的iSP信号的解码方法的一种较佳实施例中,在步骤S2中,始终检测数据的传输状态,当检测到数据传输处于场消隐期时进行相位跟踪以得到稳定的所述9bit数据流。

在本发明提供的iSP信号的解码方法的一种较佳实施例中,所述8b/9b解码器为一IP核。

在本发明提供的iSP信号的解码方法的一种较佳实施例中,所述解扰码器进行解扰处理采用的多项式为:G(X)=X16+X5+X4+X3+1。

在本发明提供的iSP信号的解码方法的一种较佳实施例中,上述步骤S2在FPGA芯片中进行。

本发明提供的一种iSP信号的解码系统,至少包括:高速收发器,用于将所述iSP信号进行解串,得到9bit数据流;8b/9b解码器,用于将所述9bit数据流进行解码,得到8bit数据流;分离模块,用于从所述8bit数据流中分离出数据包;拆包器,用于将所述数据包进行拆包处理,得到RGB信号。

在本发明提供的iSP信号的解码系统的一种较佳实施例中,所述分离模块为解扰码器,所述解扰码器从所述8bit数据流中分离出数据包的方式具体为:将所述8bit数据流进行解扰处理,得到所述数据包。

在本发明提供的iSP信号的解码系统的一种较佳实施例中,所述高速收发器至少包括自恢复相位跟踪模块,用于检测数据传输是否处于场消隐期,当检测到数据传输处于场消隐期时,进行相位跟踪。

相较于现有技术,本发明提供的iSP信号的解码方法、解码系统具有以下有益效果:

一、本发明提供的一种iSP信号的解码方法,其方法为首先获取iSP信号,然后将iSP信号传输至高速收发器进行解串,得到9bit数据流,再将该9bit数据流传输至8b/9b解码器进行解码,得到8bit数据流,从该8bit数据流中分离出数据包,再将数据包进行拆包处理,就得到了RGB信号,填补了iSP信号解码技术的空白,使得iSP信号的应用能够进一步扩展,因而本iSP信号解码方法具有极高的实用性。

二、再者,将传输速率高但复杂的iSP信号解码为常规的RGB信号,方便了对应用iSP信号的电子产品进行测试及维修,使得测试该电子产品时不需要再用原机屏测试,从而大大降低了其测试成本,提高了测试效率,因而本iSP信号解码方法能够大大推进iSP信号的应用,进而推动整体图像传输领域的传输速率进一步提高。

三、本发明提供的iSP信号的解码方法中,其采用高速收发器,将获取到的iSP信号解串为9bit数据流并提取出时钟信号,高速收发器的选用使得高传输速率的iSP信号能够快速被解串,使得后期能够快速对其进行解码,从而提高了本iSP信号解码方法的效率性。

四、本发明提供的iSP信号的解码方法中,由于解串后的9bit数据流其中的时钟信号是扩频时钟,当需要跟踪的扩频时钟的范围过大时,会出现时钟失锁,造成无法解码,而在本发明中,始终检测数据的传输状态,每当检测到数据传输处于场消隐期时,则进行相位跟踪,并且相位跟踪后会自动复位,因处于场消隐期时,不会有图像数据传输,故在场消隐期进行相位跟踪,不会造成数据丢失,保证了数据的准确性,并且,因为在每次相位跟踪后都会自动复位,故不会出现时钟失锁的情况,同时也使得该9bit数据流更加稳定,从而提高了解码后数据的准确度和稳定性。

五、本发明提供的iSP信号的解码方法中,由于iSP信号采用的编码方式不同与常见的8b/10b编码方式,而是一种比较特殊的8b/9b编码方式,因此本发明采用8b/9b解码方式,能够快速地将9bit数据流解码为8bit数据流,并且该解码器为一IP核,解码时,直接调用该IP核,9bit数据流经过该IP核,查找对应的编码,后直接输出8bit数据流,IP核的使用,使得该解码器的可移植性很强,能够适用于各种芯片,因而使得本解码方法可使用的场景更加多样化。

六、本发明提供的iSP信号的解码方法中,对于进行了加扰处理的数据,相对应在本方法中也设置有对扰码进行解扰的过程,加扰是对数据做有规律的随机化处理,减少数据流中连续高电平和连续低电平的长度,以保证接收数据时能提取到时钟信号,加扰后的数据更适合基带传输,对扰码进行对应的解扰处理,将扰码恢复为原始数据,使得能够从该数据流中分离出完整的数据包,解扰步骤的设置,极大地减少了解码错误的情况,进一步提高了解码后数据的准确度和稳定性。

七、本发明提供的iSP信号的解码方法中,从数据流中找到数据包的包头和包尾,即可分理出完整的数据包,将该数据包进行拆包处理,起始信号和包尾之间的数据就是可直接读取的RGB信号,将iSP信号解码成常规的RGB信号,使得电子设备在利用iSP信号高传输速率的基础上,能够直接读取解码后的信号,提高了本解码方法的通用性。

八、本发明提供的iSP信号的解码方法中,上述步骤S2在FPGA芯片中进行,FPGA芯片的可定制性和可重构性大大提高了本解码方法的灵活性和适应性。

九、本发明提供的iSP信号的解码系统中,其至少包括FPGA芯片,且该FPGA芯片至少包括高速收发器,用于将iSP信号进行解串,得到9bit数据流;8b/9b解码器,用于将该9bit数据流进行解码,得到8bit数据流;分离模块,用于从该8bit数据流中分离出数据包;拆包器,用于将该数据包进行拆包处理,得到RGB信号,本解码系统采用FPGA芯片直接对iSP信号进行解码,不需要外挂接口芯片,大大节约了生产成本,并且FPGA芯片的可定制性和可重构性,极大地扩展了本iSP信号解码系统的适用范围。

【附图说明】

为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图,其中:

图1是本发明第一实施例提供的一种iSP信号的解码方法的步骤流程示意图;

图2是本发明第一实施例提供的一种iSP信号的解码方法中的数据包封装格式示意图;

图3是本发明第二实施例提供的一种iSP信号的解码系统的模块示意图一;

图4是本发明第二实施例提供的一种iSP信号的解码系统的模块示意图二;

图5是本发明第三实施例提供的一种电视机测试系统的模块示意图一。

附图标识说明:

1、iSP信号的解码系统;2、电视机测试系统;

11、高速收发器;12、8b/9b解码器;13、分离模块;14、拆包器;21、电视机主板;

131、解扰码器。

【具体实施方式】

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

为方便理解,本发明在此对iSP信号进行说明,iSP信号是一种应用于TFT-LCD的集成流协议信号,该信号是一种专门针对图像传输开发的数字接口标准,其支持多端口数据输出,最大传输速率高达3.6Gbps。

请参考图1,本发明第一实施例提供一种iSP信号的解码方法,其包括以下步骤:

步骤S1,获取iSP信号;

步骤S2,将iSP信号传输至高速收发器进行解串,得到9bit数据流;

步骤S3,将9bit数据流传输至8b/9b解码器进行解码,得到8bit数据流;

步骤S4,从8bit数据流中分离出数据包;

步骤S5,将数据包进行拆包处理,得到RGB信号。

基于上述的iSP信号的解码方法,可以将传输速率极高但信号结构复杂的iSP信号解码为常规的RGB信号,该解码方法填补了iSP信号解码技术的空白,使得iSP信号的应用能够进一步扩展,再者,将复杂的iSP信号解码为常规的RGB信号,方便了对应用iSP信号的电子产品进行测试及维修,使得测试该电子产品时不需要再用原机屏测试,从而大大降低了其测试成本,提高了测试效率,因而该iSP信号解码方法能够大大推进iSP信号的应用,推动了整体图像传输领域的传输速率进一步提高。

可选地,在本发明提供的iSP信号的解码方法中,其高速收发器为高速串行收发器或高速并行收发器,可以理解地,其高速收发器用于对接收到的iSP信号进行快速解串,并不限于高速串行收发器和高速并行收发器这两个类型,只要能实现对接收到的iSP信号进行快速解串即可,具体地,作为一种实施例,在本发明提供的iSP信号的解码方法中,其高速收发器为高速串行收发器。

进一步地,由于解串后的9bit数据流其中的时钟信号是扩频时钟,当需要跟踪的扩频时钟的范围过大时,会出现时钟失锁,造成无法解码,在本发明提供的iSP信号的解码方法的步骤S2中,其始终检测数据的传输状态,每当检测到数据传输处于场消隐期时,则进行相位跟踪,并且相位跟踪后会自动复位,因处于场消隐期时,不会有图像数据传输,故在场消隐期进行相位跟踪,不会造成数据丢失,保证了数据的准确性,并且,因为在每次相位跟踪后都会自动复位,故不会出现时钟失锁的情况,同时也使得该9bit数据流更加稳定,从而提高了解码后数据的准确度和稳定性,得到了稳定的9bit数据流。

可以理解地,8b/9b编码方式,采用的是二段式编码。第一段编码,先将数据经过逻辑计算,即得到type II的结果;然后经过一个逻辑判断条件,若判断条件不成立,type II的结果就等于type I的结果,即最终编码结果;若判断条件成立,type II的结果还需经过一些逻辑计算后,才得到type I,即最终编码结果,当使用8b/9b编码方式编码后的数据需要解码,则对编码后的数据进行与编码过程相反的操作即可,即TYPEI/TYPEII-8b/9b解码方式。

进一步地,由于iSP信号采用的编码方式不同于常见的8b/10b编码方式,而是比较特殊的8b/9b编码方式,在本发明提供的iSP信号的解码方法中,采用8b/9b解码器,能够快速地将9bit数据流解码为8bit数据流,更进一步地,该8b/9b解码器为一知识产权核(Intellectual Property core,IP核),其IP核采用无延时解码电路结构或低延时解码电路结构,其解码方式为查表法,解码时,直接调用该IP核,9bit数据流经过该IP核,查找对应的编码,后直接输出8bit数据流,IP核的使用,使得该解码器的可移植性很强,能够适用于各种芯片,从而使得本解码方法可使用的场景更加多样化。

具体地,作为一种实施例,在本发明提供的iSP信号的解码方法中,该8b/9b解码器采用的解码方式为TYPEI/TYPEII-8b/9b解码方式,TYPEI/TYPEII-8b/9b解码方式是通过查表法进行解码,即将256(2^8)个数据,全部经过type I/type II-8b/9b编码后,会得到256个编码后的数据,将编码前和编码后的数据做成一个对应关系表,存放在FPGA的ROM中,构成IP核,解串后的9bit数据流经过该IP核后,查找表中对应的数据,就可以得到编码前的数据,即完成解码,得到8bit数据流。可以理解地,加扰是一种数据信号的加工处理方法,即为对数据做有规律的随机化处理,用扰码与原始信号相乘,从而得到新的信号,减少数据流中连续高电平和连续低电平的长度,以保证接收数据时能提取到时钟信号,加扰后的数据更适合基带传输,与原始信号相比,新的信号即扰码在时间上、频率上被打散,而将加扰的数据信号恢复为原有数据信号的操作即为解扰。

进一步地,对于进行了加扰处理的数据,相对应在本方法中也设置有对扰码进行解扰的过程,在将9bit数据流解码为8bit数据流之后,将8bit数据流传输至解扰码器进行与加扰处理对应的解扰处理,即可将扰码恢复为原始数据,使得能够从该数据流中分离出完整的数据包,解扰步骤的设置,避免了未解扰导致解码错误的情况,进一步提高了解码后数据的准确度和稳定性。

进一步地,经过解扰后的数据即为一个个完整的数据包,找到数据包的包头和包尾,即可分理出数据包,将该数据包进行拆包处理,起始信号和包尾之间的数据就是可直接读取的RGB信号,将iSP信号解码成常规的RGB信号,使得电子设备在利用iSP信号高传输速率的基础上,能够直接读取解码后的信号,提高了本解码方法的通用性。

请参考图2,具体地,作为一种实施例,在本发明提供的iSP信号的解码方法中,数据包的封装格式如图2所示,其中包头为BAC,其值为“8'b0f”,起始信号为POL,其值为“8'b0c”或“8'bf3”,包尾为EOL,其值为“8'b3f”,而所需的常规RGB信号即为Data。

具体地,作为一种实施例,在本发明提供的iSP信号的解码方法中,其解扰码器为一种新型的解扰码器,其包括一线性反馈移位寄存器,其进行解扰处理采用的多项式为:G(X)=X16+X5+X4+X3+1,该多项式表示,在该线性反馈移位寄存器的第16级,第5级,第4级,第3级和第0级存在反馈线。

进一步地,上述步骤S2在FPGA芯片中进行,FPGA芯片的可定制性和可重构性大大提高了本解码方法的灵活性和适应性。

请结合图3-图4,本发明第二实施例提供一种iSP信号的解码系统1,其至少包括FPGA芯片,FPGA芯片至少包括:

高速收发器11,用于将iSP信号进行解串,得到9bit数据流;

8b/9b解码器12,用于将9bit数据流进行解码,得到8bit数据流;

分离模块13,用于从8bit数据流中分离出数据包;

拆包器14,用于该数据包进行拆包处理,得到RGB信号。

其iSP信号的解码系统1采用FPGA芯片直接对iSP信号进行解码,不需要外挂接口芯片,大大节约了生产成本,并且FPGA芯片的可定制性和可重构性,极大地扩展了该iSP信号的解码系统1的适用范围。

作为一种实施方式,分离模块13为解扰码器131,解扰码器131从8bit数据流中分离出数据包的方式具体为:将8bit数据流进行解扰处理,得到数据包。解扰码器131能够对进行了加扰处理的数据进行解扰,将扰码恢复为原始数据,使得能够从该数据流中得到完整的数据包。

可选地,高速收发器11至少包括自恢复相位跟踪模块,用于检测数据传输是否处于场消隐期,每当检测到数据传输处于场消隐期时,进行相位跟踪,在场消隐期进行相位跟踪,不会造成数据丢失,保证了数据的准确性,并且,因每次相位跟踪后都会自动复位,故不会出现时钟失锁的情况,从而提高了本iSP信号的解码系统1的数据准确度和稳定性。

请参考图5,本发明第三实施例提供一种电视机测试系统2,电视机测试系统2包括电视机主板21及本发明第二实施例提供的iSP信号的解码系统1,其电视机主板21与其iSP信号的解码系统1连接,电视机主板21发出iSP信号,iSP信号的解码系统1将该iSP信号进行解码得到RGB信号,将电视机主板21发出的结构复杂的iSP信号解码成常规的RGB信号,便于制造和维修过程中对该电视机主板21进行测试,使得该电视机测试系统2解码后的信号能够在大部分电视机显示屏上显示相应的画面,无须使用与其电视机主板21对应的电视机显示屏,使得对发出iSP信号的电视机主板21的测试和维修过程更方便快捷,大大提高了电视机主板21的测试效率和维修成本。。

示例性的,该电视机测试系统2的工作过程为:先将电视机主板21与iSP信号的解码系统1通过信号导线连接,实现物理链路层的连接;然后为电视机主板21供电,使其发出iSP信号,该iSP信号的解码系统1中的高速收发器接收到iSP信号并对其进行解串,解串出9bit数据流并提取出其中的时钟信号,高速收发器中的自恢复相位跟踪模块始终检测9bit数据流的传输状态,当检测到数据传输处在场消隐期时,其自恢复相位跟踪模块产生相位跟踪信号并进行相位跟踪,且在相位跟踪后自动恢复,从而可以避免发生时钟失锁的情况,同时也使得该9bit数据流更加稳定;然后对得到的稳定的9bit数据流通过TYPEI/TYPEII-8b/9b解码方式进行解码,9bit数据流进入8b/9b解码器,与IP核中的数据比对,得到与该9bit数据流对应的数据,则得到解码后的8bit数据流;然后该8bit数据流进入解扰码器进行解扰,该解扰处理采用的多项式为:G(X)=X16+X5+X4+X3+1,经过解扰后的数据即为一个个完整的数据包,找到数据包的包头和包尾,即可分理出数据包;最后将该数据包进行拆包处理,其起始信号和包尾之间的数据就是可直接读取的RGB信号,其包头值为“8'b0f”,其起始信号值为“8'b0c”或“8'bf3”,其包尾值为“8'b3f”,而所需的常规RGB信号即起始信号和包尾之间的数据。

相较于现有技术,本发明提供的iSP信号的解码方法、解码系统具有以下有益效果:

一、本发明提供的一种iSP信号的解码方法,其方法为首先获取iSP信号,然后将iSP信号传输至高速收发器进行解串,得到9bit数据流,再将该9bit数据流传输至8b/9b解码器进行解码,得到8bit数据流,从该8bit数据流中分离出数据包,再将数据包进行拆包处理,就得到了RGB信号,填补了iSP信号解码技术的空白,使得iSP信号的应用能够进一步扩展,因而本iSP信号解码方法具有极高的实用性。

二、再者,将传输速率高但复杂的iSP信号解码为常规的RGB信号,方便了对应用iSP信号的电子产品进行测试及维修,使得测试该电子产品时不需要再用原机屏测试,从而大大降低了其测试成本,提高了测试效率,因而本iSP信号解码方法能够大大推进iSP信号的应用,进而推动整体图像传输领域的传输速率进一步提高。

三、本发明提供的iSP信号的解码方法中,其采用高速收发器,将获取到的iSP信号解串为9bit数据流并提取出时钟信号,高速收发器的选用使得高传输速率的iSP信号能够快速被解串,使得后期能够快速对其进行解码,从而提高了本iSP信号解码方法的效率性。

四、本发明提供的iSP信号的解码方法中,由于解串后的9bit数据流其中的时钟信号是扩频时钟,当需要跟踪的扩频时钟的范围过大时,会出现时钟失锁,造成无法解码,而在本发明中,始终检测数据的传输状态,每当检测到数据传输处于场消隐期时,则进行相位跟踪,并且相位跟踪后会自动复位,因处于场消隐期时,不会有图像数据传输,故在场消隐期进行相位跟踪,不会造成数据丢失,保证了数据的准确性,并且,因为在每次相位跟踪后都会自动复位,故不会出现时钟失锁的情况,同时也使得该9bit数据流更加稳定,从而提高了解码后数据的准确度和稳定性。

五、本发明提供的iSP信号的解码方法中,由于iSP信号采用的编码方式不同与常见的8b/10b编码方式,而是一种比较特殊的8b/9b编码方式,因此本发明采用8b/9b解码方式,能够快速地将9bit数据流解码为8bit数据流,并且该解码器为一IP核,解码时,直接调用该IP核,9bit数据流经过该IP核,查找对应的编码,后直接输出8bit数据流,IP核的使用,使得该解码器的可移植性很强,能够适用于各种芯片,因而使得本解码方法可使用的场景更加多样化。

六、本发明提供的iSP信号的解码方法中,对于进行了加扰处理的数据,相对应在本方法中也设置有对扰码进行解扰的过程,加扰是对数据做有规律的随机化处理,减少数据流中连续高电平和连续低电平的长度,以保证接收数据时能提取到时钟信号,加扰后的数据更适合基带传输,对扰码进行对应的解扰处理,将扰码恢复为原始数据,使得能够从该数据流中分离出完整的数据包,解扰步骤的设置,极大地减少了解码错误的情况,进一步提高了解码后数据的准确度和稳定性。

七、本发明提供的iSP信号的解码方法中,从数据流中找到数据包的包头和包尾,即可分理出完整的数据包,将该数据包进行拆包处理,起始信号和包尾之间的数据就是可直接读取的RGB信号,将iSP信号解码成常规的RGB信号,使得电子设备在利用iSP信号高传输速率的基础上,能够直接读取解码后的信号,提高了本解码方法的通用性。

八、本发明提供的iSP信号的解码方法中,上述步骤S2在FPGA芯片中进行,FPGA芯片的可定制性和可重构性大大提高了本解码方法的灵活性和适应性。

九、本发明提供的iSP信号的解码系统中,其至少包括FPGA芯片,且该FPGA芯片至少包括高速收发器,用于将iSP信号进行解串,得到9bit数据流;8b/9b解码器,用于将该9bit数据流进行解码,得到8bit数据流;分离模块,用于从该8bit数据流中分离出数据包;拆包器,用于将该数据包进行拆包处理,得到RGB信号,本解码系统采用FPGA芯片直接对iSP信号进行解码,不需要外挂接口芯片,大大节约了生产成本,并且FPGA芯片的可定制性和可重构性,极大地扩展了本iSP信号解码系统的适用范围。

- 一种iSP信号的解码方法、解码系统

- 可分层音频编解码方法系统及瞬态信号可分层编解码方法