一种抗单粒子瞬态的高电平复位电路

文献发布时间:2023-06-19 10:32:14

技术领域

本发明涉及CMOS集成电路技术领域,尤其涉及一种抗单粒子瞬态的高电平复位电路。

背景技术

在宇宙空间中,存在大量高能粒子(质子、电子、重离子等)。集成电路受到这些高能粒子轰击后,会产生单粒子瞬态脉冲。单粒子瞬态脉冲对于集成电路的正常工作将产生极大的负面影响,例如,当单粒子瞬态脉冲传播至时序电路单元复位端口时,由于时序单元采用异步复位模式,只需满足复位信号最小脉冲宽度即可立刻使时序单元发生复位,改变时序单元所存储的数据值。由于复位信号是一个全局信号,若单粒子瞬态脉冲在复位电路根节点产生,那么就会使得整个集成电路复位,从而造成错误。如L.W.Massengill等人在IEEE transaction on Nuclear Science(IEEE核科学汇刊)上发表的“Single EventTransients in Digital CMOS-A Review”(关于数字CMOS电路中单粒子瞬态的综述,2013年6月第60卷第3期,第1767-1790页)就指出,单粒子瞬态现已成为软错误的一个主要来源。因此,有必要针对复位电路进行抗单粒子瞬态加固。

CMOS集成电路复位电路通常由CMOS缓冲器构成,传统CMOS缓冲器由多个晶体管构成,当CMOS缓冲器工作时,必然会有晶体管处于关闭状态,而这种处于关闭状态的晶体管对粒子轰击是敏感的。当高能粒子轰击CMOS缓冲器中处于关闭状态的晶体管时,即会有单粒子瞬态产生,因而CMOS缓冲器对单粒子瞬态是较为敏感的。如图1所示,传统CMOS缓冲器至少包含有2个PMOS晶体管和2个NMOS晶体管,当CMOS缓冲器工作时,至少有1个PMOS晶体管和1个NMOS晶体管处于关闭状态,这2个处于关闭状态的晶体管会对重离子轰击敏感,这也即为敏感节点。如图2所示,晶体管N1以及晶体管P2即为敏感节点。传统复位电路如图3所示,各级缓冲器依次连接形成链路,其中末端位置处的缓冲器连接触发器。对于高电平复位电路,如由如图1所示的CMOS缓冲器单元构成高电平复位电路,启动CMOS缓冲器单元工作,当输入为低电平时,晶体管N1以及晶体管P2均处于关闭状态,当粒子轰击到复位电路中任意一级缓冲器中该这两个晶体管时会产生单粒子瞬态,会影响整个电路的稳定性。因此,亟需提供一种能够抗单粒子瞬态(SET,Single-Event Transient)的高电平复位电路,以提高高电平复位电路的抗单粒子瞬态能力。

发明内容

本发明要解决的技术问题就在于:针对现有技术存在的技术问题,本发明提供一种结构简单、成本低、具有抗单粒子瞬态能力、稳定可靠的抗单粒子瞬态的高电平复位电路。

为解决上述技术问题,本发明提出的技术方案为:

一种抗单粒子瞬态的高电平复位电路,包括两级以上的缓冲器单元,各级所述缓冲器单元依次串联连接,各级所述缓冲器单元中处于末端位置处的末级缓冲器单元为加固缓冲器单元,所述加固缓冲器单元包括依次连接的与非门电路以及反相器电路,所述与非门电路包括相互连接的第一晶体管P1、第二晶体管P2、延时单元以及第一电阻R1,所述反相器电路包括相互连接的第二电阻R2以及第三晶体管N1,当输入信号为低电平时,所述第一晶体管P1、第二晶体管P2、第三晶体管N1均为打开状态。

进一步的,所述与非门电路中,所述第一晶体管P1的栅极、所述延时单元的输入端均连接至输入信号端,所述第一晶体管P1、第二晶体管P2的源极均连接电源,所述第一晶体管P1、第二晶体管P2的漏极均分别连接至所述反相器电路的输入端以及通过所述第一电阻R1接地,所述延时单元的输出端连接至第二晶体管P2的栅极。

进一步的,所述反相器电路中,所述第三晶体管N1的栅极连接所述与非门电路的输出端,所述第三晶体管N1的漏极分别连接输出信号端以及通过所述第二电阻连接电源,所述第三晶体管N1的源极接地。

进一步的,所述第一晶体管P1、第二晶体管P2均为PMOS晶体管,所述第三晶体管N1为NMOS晶体管。

进一步的,所述第一电阻R1和/或第二电阻R2为多晶硅电阻。

进一步的,各级所述缓冲器单元中节点数量逐级递增,每个节点对应为一个缓冲器单元。

进一步的,处于末端位置处的所述末级缓冲器单元连接触发器。

与现有技术相比,本发明的优点在于:

1、本发明通过与非门电路以及反相器电路构成加固缓冲器单元,在敏感节点位置处使用电阻,当输入信号为低电平时,电路中各晶体管均为打开状态,不存在关闭状态的晶体管,可以消除对于重离子轰击敏感的敏感节点,使得缓冲器单元中不会存在敏感节点,从而具备过滤单粒子瞬态脉冲功能且无法产生单粒子瞬态,可以实现复位电路的抗单粒子瞬态加固。

2、本发明在功能电路正常工作后,粒子轰击加固缓冲器单元,无法产生单粒子瞬态脉冲,粒子轰击加固缓冲器单元以外的复位电路虽然会产生单粒子瞬态脉冲,但会被该位于复位电路末端的加固缓冲器单元过滤,从而可以确保功能电路的正常工作。

3、本发明仅需在复位电路末端设置加固缓冲器单元,使得复位电路链的末端具备单粒子瞬态脉冲功能且无法产生单粒子瞬态,其余链路可以保留原电路结构,因而仅需较小的简单改造即可实现高电平复位电路的抗单粒子瞬态加固,且可兼容性较好,易于与传统复位电路设计流程兼容。

附图说明

图1为现有技术中缓冲器电路的电路结构图。

图2为现有技术中缓冲器单元输出低电平时的敏感节点示意图。

图3为现有技术中复位电路的电路结构示意图。

图4为本实施例抗单粒子瞬态的高电平复位电路中加固缓冲器单元的电路结构示意图。

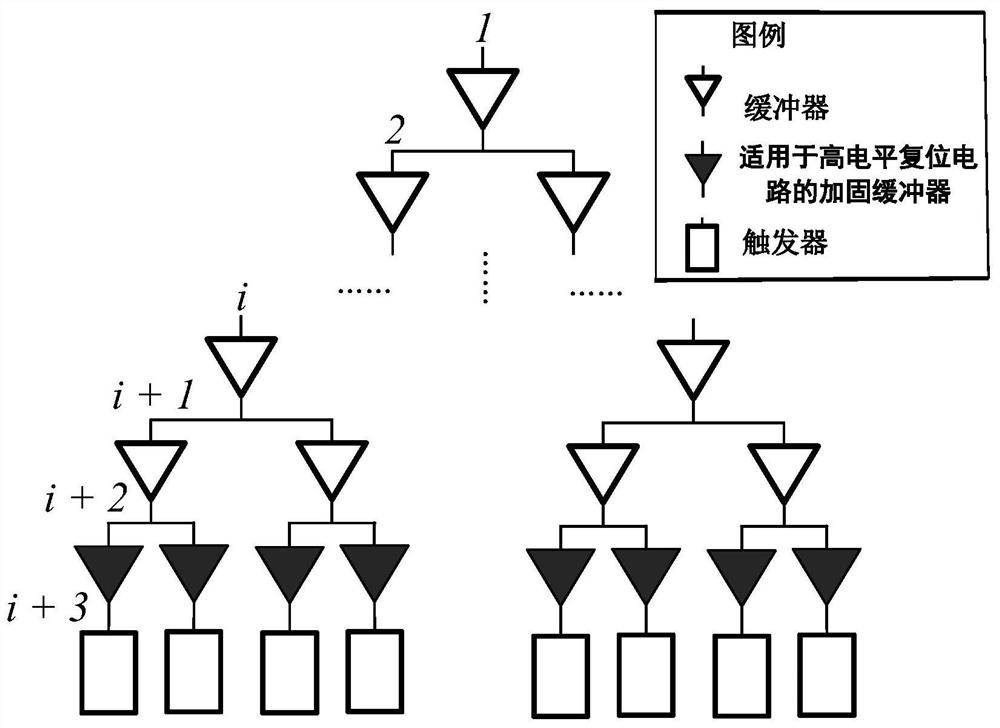

图5为本实施例抗单粒子瞬态的高电平复位电路的电路结构示意图。

图6为对现有技术中复位电路测试时受粒子轰击的模拟波形图。

图7为对本发明抗单粒子瞬态的高电平复位电路测试时受粒子轰击的模拟波形图。

具体实施方式

以下结合说明书附图和具体优选的实施例对本发明作进一步描述,但并不因此而限制本发明的保护范围。

如图4、5所示,本实施例抗单粒子瞬态的高电平复位电路包括两级以上的缓冲器单元,各级缓冲器单元依次串联连接,各级缓冲器单元中处于末端位置处的末级缓冲器单元为加固缓冲器单元,加固缓冲器单元包括依次连接的与非门电路以及反相器电路,与非门电路包括相互连接的第一晶体管P1、第二晶体管P2、延时单元(DELAY)以及第一电阻R1,反相器电路包括相互连接的第二电阻R2以及第三晶体管N1,当输入信号为低电平时,第一晶体管P1、第二晶体管P2、第三晶体管N1均为打开状态。

本实施例首先确定出高电平复位电路的缓冲器中的敏感节点,如图2所示,当由如图1所示的CMOS缓冲器构成高电平复位电路时,启动CMOS缓冲器工作,当输入为低电平时,晶体管N1以及晶体管P2处于关闭状态,晶体管N1以及晶体管P2即为敏感节点。本实施例在确定出高电平复位电路缓冲器中敏感节点后,在敏感节点位置处使用电阻,通过与非门电路以及反相器电路构成加固缓冲器单元,当输入信号为低电平时,电路中各晶体管均为打开状态,不存在关闭状态的晶体管,可以消除对于重离子轰击敏感的敏感节点,即该加固缓冲器单元中不会存在敏感节点,具备过滤单粒子瞬态脉冲功能且无法产生单粒子瞬态,可以实现高电平复位电路的抗单粒子瞬态加固,因而在功能电路正常工作后,粒子轰击该加固缓冲器单元,无法产生单粒子瞬态脉冲,粒子轰击加固缓冲器单元以外的复位电路虽然会产生单粒子瞬态脉冲,但会被该位于复位电路末端的加固缓冲器单元过滤,从而可以确保功能电路的正常工作。

本实施例上述复位电路,仅需在复位电路末端设置加固缓冲器单元,使得复位电路链的末端具备过滤单粒子瞬态脉冲功能且无法产生单粒子瞬态,其余链路可以保留原电路结构,因而仅需较小的简单改造即可实现复位电路的抗单粒子瞬态加固,且可兼容性较好,易于与传统复位电路设计流程兼容。

如图3所示,本实施例与非门电路中,第一晶体管P1的栅极、延时单元(DELAY)的输入端均连接至输入信号端A,第一晶体管P1、第二晶体管P2的源极均连接电源VDD,第一晶体管P1、第二晶体管P2的漏极均分别连接至反相器电路的输入端以及通过第一电阻R1接地GND,延时单元的输出端连接至第二晶体管P2的栅极;反相器电路中,第三晶体管N1的栅极连接与非门电路的输出端,第三晶体管N1的漏极分别连接输出信号端Y以及通过第二电阻连接电源VDD,第三晶体管N1的源极接地GND。上述第一晶体管P1、第二晶体管P2均为PMOS晶体管,第三晶体管N1为NMOS晶体管。

本实施例中,第一电阻R1、第二电阻R2采用多晶硅电阻。多晶硅电阻稳定性好,精度高,通过在缓冲器单元的敏感节点处使用多晶硅电阻可以进一步提高缓冲器的抗单粒子瞬态性能,且更适合于工程应用。

参见图4,本实施例加固缓冲器单元具体由1个单输入的与非门电路和1个反相器电路构成,其中与非门由2个PMOS晶体管(P1和P2)、1个延时单元(DELAY)和1个电阻(R1)组成,反相器由1个多晶硅电阻(R2)和1个NMOS晶体管(N1)组成。在与非门电路中,晶体管P1和P2的源极均连接VDD,漏极均连接与非门电路的输出X0,晶体管P1的栅极连接与非门电路的输入A(同时也是缓冲器单元的输入端),P1的栅极同时连接延时单元(DELAY),延时单元(DELAY)的输出连接至晶体管P2的栅极;电阻R1的一端连接与非门的输出端X0,另外一端接地GND。在反相器电路中,晶体管N1的栅极连接反相器电路的输入端X1(同时也为与非门电路的输出X0),晶体管N1的漏极连接反相器电路的输出端Y(同时也为加固缓冲器单元的输出端),晶体管N1的源极接地GND,电阻R2的一端接电源VDD,另外一端连接反相器电路的输出Y(同时也为加固缓冲器单元的输出端)。由于上述加固缓冲器单元在输入为低电平状态时,P1晶体管、P2晶体管和N1晶体管均处于打开状态,不存在单粒子瞬态敏感节点。

在具体应用实施例中先由2个PMOS晶体管、1个延时单元和1个多晶硅电阻按照上述连接方式构成与非门电路,由1个多晶硅电阻和1个NMOS晶体管按照上述连接方式构成反相器电路;由与非门电路、反相器电路连接即构成加固缓冲器单元;再构建复位电路,复位电路中除末级缓冲器外,各级缓冲器均使用普通缓冲器单元,末级缓冲器即为处于末端位置级、连接触发器的缓冲器,末级缓冲器使用上述加固缓冲器单元,即构建形成所需的能够抗单粒子瞬态的高电平复位电路,如图5所示。

本实施例中,复位电路的各级缓冲器单元中节点数量逐级递增,每个节点对应为一个缓冲器单元。如图5所示,对于最左侧的复位缓冲器单元链路,第1级缓冲器单元的输入为1节点,输出为2节点;第2级缓冲器单元的输入为2节点,输出为3节点;第i级缓冲器单元的输入为i节点,输出为i+1节点,其中末级(连接触发器的复位缓冲器单元)采用了上述加固缓冲器单元。

为验证本发明高电平复位电路的功能,在具体应用实施例中分别对如图1所示的传统缓冲器构成复位电路以及本发明上述高电平复位电路进行粒子轰击,并对结果进行对比。

如图3所示,当采用传统高电平复位电路时,对于最左侧的复位缓冲器单元链路,第1级缓冲器单元的输入为1节点,输出为2节点;第2级缓冲器单元的输入为2节点,输出为3节点;第i级缓冲器单元的输入为i节点,输出为i+1节点。对于图4中的高电平复位电路,当i=97时,最左侧的复位缓冲器链路共有99级复位缓冲器,用v(1)表示第1级复位缓冲器的输入电压波形,用v(2)表示第2级复位缓冲器的输出电压波形,用v(99)表示第98级复位缓冲器的输出电压波形,用v(100)表示第99级复位缓冲器的输出电压波形。当功能电路正常工作时,该复位电路输入低电平,输出低电平。通过指数电流源模拟粒子轰击该复位电路第1级复位缓冲器的P2晶体管,注入一段1ns的SET脉冲,这段SET脉冲将持续传播下去。在具体应用实施例中得到的SPICE仿真波形如图6所示,第99级复位缓冲器的输出电压波形存在单粒子瞬态脉冲,从而会引发触发器复位,进而引发功能电路出错。

对于如图4、5中本发明的高电平复位电路,当i=97时,最左侧的复位缓冲器链路共有99级复位缓冲器,用v(1)表示第1级复位缓冲器的输入电压波形,用v(2)表示第2级复位缓冲器的输出电压波形,用v(99)表示第98级复位缓冲器的输出电压波形,用v(100)表示第99级复位缓冲器的输出电压波形。当功能电路正常工作时,该复位电路输入低电平,输出低电平。通过指数电流源模拟粒子轰击该复位电路第1级复位缓冲器的P2晶体管,注入一段1ns的SET脉冲,在具体应用实施例中得到的SPICE仿真波形如图7所示,尽管这段SET脉冲可以在现有缓冲器链(第1级到第98级缓冲器)中传播,但当这段SET脉冲经过第99级加固缓冲器后,SET脉冲消失,不会引发触发器复位,功能电路可以正常工作。即本发明抗单粒子瞬态的高电平复位电路能够对单粒子瞬态免疫。

上述只是本发明的较佳实施例,并非对本发明作任何形式上的限制。虽然本发明已以较佳实施例揭露如上,然而并非用以限定本发明。因此,凡是未脱离本发明技术方案的内容,依据本发明技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均应落在本发明技术方案保护的范围内。

- 一种抗单粒子瞬态的高电平复位电路

- 一种用于低电平复位电路的抗单粒子瞬态缓冲器