交易执行方法、区块链一体机和区块链网络

文献发布时间:2023-06-19 10:32:14

技术领域

本申请涉及区块链技术领域,具体涉及一种交易执行方法、区块链一体机和区块链网络。

背景技术

在现有技术中,由于区块链一体机价格低廉,大量用户选择部署区块链一体机来使用区块链服务;上述区块链一体机由于价格低廉、其上的cpu性能不足,且cpu将花费大量算力在签名验证上,当上述区块链一体机在一段时间内收到大量交易时,必然会造成tps不足的问题。

发明内容

鉴于现有技术中的上述缺陷或不足,期望提供一种成本较低、且保证tps的交易执行方法、区块链一体机和区块链网络。

第一方面,本发明提供一种适用于区块链一体机的交易执行方法,区块链一体机包括SOC FPGA芯片,SOC FPGA芯片包括CPU IP核和FPGA IP核,CPU IP核包括交易池模块,上述方法包括:

交易池模块接收第一交易,将第一交易发送至FPGA IP核;

FPGA IP核验证第一交易的签名信息,并向交易池模块返回第一交易的第一验证结果;

在第一验证结果为通过验证时,交易池模块存储第一交易。

第二方面,本发明提供一种区块链一体机,包括SOC FPGA芯片,SOC FPGA芯片包括CPU IP核和FPGA IP核,CPU IP核包括交易池模块;其中,

交易池模块用于接收第一交易,将第一交易发送至FPGA IP核,以及,接收并保存FPGA IP核返回的第一交易的第一验证结果,以及,在第一验证结果为通过验证时,存储第一交易;

FPGA IP核用于验证第一交易的签名信息,并向交易池模块返回第一交易的第一验证结果。

第三方面,本发明还提供一种区块链网络,区块链网络包括若干如第二方面所述的区块链一体机。

本发明诸多实施例提供的交易执行方法通过交易池模块接收第一交易,将第一交易发送至FPGA IP核;FPGA IP核验证第一交易的签名信息,并向交易池模块返回第一交易的第一验证结果;在第一验证结果为通过验证时,交易池模块存储第一交易的方法,在区块链一体机成本较低的情况下保证tps。

附图说明

通过阅读参照以下附图所作的对非限制性实施例所作的详细描述,本申请的其它特征、目的和优点将会变得更明显:

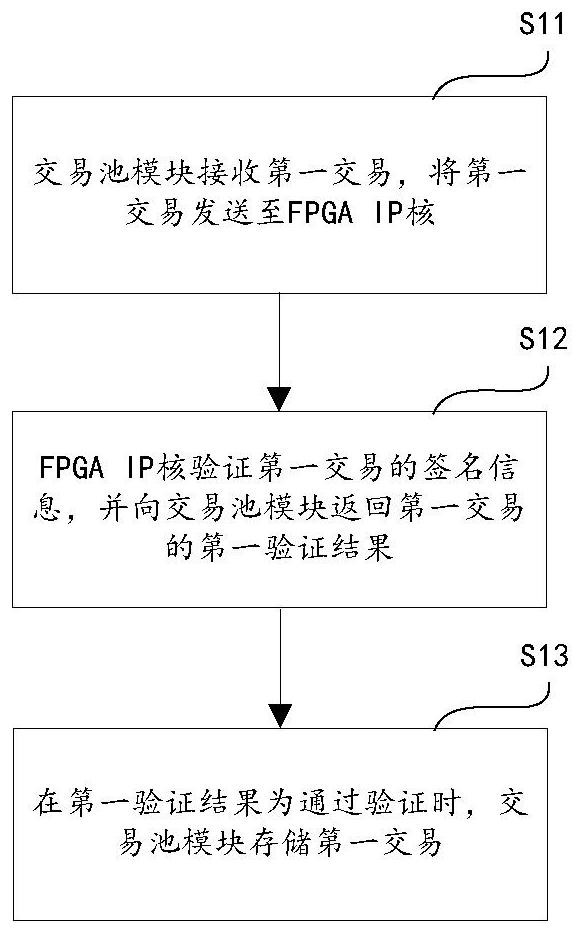

图1为本发明一实施例提供的一种交易执行方法的流程图。

图2为图1所示的方法的一种优选实施方式的流程图。

图3为图2所示的方法的一种优选实施方式的流程图。

图4为图1所示的方法的另一种优选实施方式的流程图。

图5为本发明一实施例提供的一种区块链一体机的结构示意图。

具体实施方式

下面结合附图和实施例对本申请作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释相关发明,而非对该发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与发明相关的部分。

需要说明的是,在不冲突的情况下,本申请中的实施例及实施例中的特征可以相互组合。下面将参考附图并结合实施例来详细说明本申请。

图1为本发明一实施例提供的一种交易执行方法的流程图。如图1所示,在本实施例中,本发明提供一种适用于区块链一体机的交易执行方法,区块链一体机包括SOC FPGA芯片,SOC FPGA芯片包括CPU IP核和FPGA IP核,方法包括:

S11:交易池模块接收第一交易,将第一交易发送至FPGA IP核;

S12:FPGA IP核验证第一交易的签名信息,并向交易池模块返回第一交易的第一验证结果;

S13:在第一验证结果为通过验证时,交易池模块存储第一交易。

具体地,交易池模块核执行步骤S11,接收交易tx1,将tx1发送至FPGA IP核;

FPGA IP核执行步骤S12,验证tx1的签名信息,并向交易池模块返回tx1的验证结果;

交易池模块执行步骤S13,在tx1的验证结果为通过验证时,存储tx1。

在更多实施例中,还可以根据实际需求配置tx1未验证通过的操作,例如配置为,内存池模块将tx1打上验证失败标识,且区块链上配置有查询接口,上述查询接口用于供用户在内存池模块上查询tx1的失败状态。

本领域技术人员应当理解,FPGA IP核还可以根据实际需求处理区块链服务中的其它需要大量消耗tps的任务,例如用于验证零知识证明、计算哈希值(例如计算哈希值以构造梅克尔树)等。

上述实施例在区块链一体机成本较低的情况下保证tps,保证了区块链一体机的整体性能。

图2为图1所示的方法的一种优选实施方式的流程图。如图2所示,在一实施例中,上述方法还包括:

S14:CPU IP核将所接收的第一区块的各第二交易发送至FPGA IP核;

S15:FPGA IP核验证第一区块中的各第二交易的签名信息,在全部验证结束时通知CPU IP核;

S16:CPU IP核从FPGA IP核获取各第二交易对应的第二验证结果以执行各第二交易。

具体地,CPU IP核执行步骤S14,将所接收的区块block(100)的各交易(tx10~tx20)发送至FPGA IP核;

FPGA IP核执行步骤S15,验证tx10~tx20的签名信息,在全部验证结束时通知CPUIP核;

CPU IP核执行步骤S16,从FPGA IP核获取tx10~tx20对应的验证结果以执行tx10~tx20。

图3为图2所示的方法的一种优选实施方式的流程图。如图3所示,在一优选实施例中,在S12后,上述方法还包括:

S17:FPGA IP核缓存验证通过的第一交易的第一哈希值;

步骤S15包括:

FPGA IP核对各第二交易执行如下操作:

S1511:FPGA IP核判断是否缓存有与第二交易的第二交易哈希值相同的第一哈希值:

是,则执行步骤S1512:不再次验证第二交易的签名信息,并将第二交易的第二验证结果确定为正确;

S152:在全部验证结束时通知CPU IP核。

具体地,FPGA IP核执行步骤S17,缓存hash(tx1);

假设FPGA IP核此时缓存有hash(tx10)、hash(tx50)、hash(tx1);

FPGA IP核对tx10~tx20分别执行如下操作:

对于tx10:

FPGA IP核执行步骤S1511,核判断是否缓存有hash(tx10):

是,则执行步骤S1512,不验证tx10的签名信息,并将tx10的验证结果确定为正确;

对于tx11:

FPGA IP核执行步骤S1511,核判断是否缓存有hash(tx11):

否,则验证tx11的签名信息;

tx12~tx20与tx11相同,此处不再赘述;

FPGA IP核执行步骤S152,在tx10~tx20全部验证结束时通知CPU IP核。

上述方法可以有效避免重复性检查验证,进一步提高tps。

图4为图1所示的方法的另一种优选实施方式的流程图。如图4所示,在一优选实施例中,在S12后,上述方法还包括:

S18:FPGA IP核缓存验证通过的第一交易的第一哈希值;

S191:FPGA IP核接收交易池模块发送的第三交易,判断是否缓存有与第三交易的第三交易哈希值相同的第一哈希值:

是,则执行步骤S192:丢弃第三交易。

具体地,FPGA IP核执行步骤S18,缓存hash(tx1);

假设FPGA IP核此时缓存有hash(tx10)、hash(tx50)、hash(tx1);

FPGA IP核执行步骤S191,接收交易池模块发送的交易tx50,判断是否缓存有hash(tx50):

是,则执行步骤S192:丢弃tx50。

上述方法可以有效避免重复性检查验证,进一步提高tps。

优选地,FPGA IP核并行验证不同交易的签名信息。

本领域技术人员应当理解,FPGA IP核可以并行验证签名,其并行度取决于计算架构,同时其硬件成本也与并行度成正比,所以需要根据实际的tps决定采购多大并行度的FPGA IP核,一般可以使用并行度为4或者8的FPGA IP核,相当于4核或者8核的处理器。

图5为本发明一实施例提供的一种区块链一体机的结构示意图。如图5所示,在本实施例中,本发明提供一种区块链一体机10,包括SOC FPGA芯片100,SOC FPGA芯片100包括CPU IP核110和FPGA IP核120,CPU IP核包括交易池模块1110;其中,

交易池模块1110用于接收第一交易,将第一交易发送至FPGA IP核120,以及,接收并保存FPGA IP核返回的验证通过的第一交易的第一验证结果,以及,在第一验证结果为通过验证时,存储第一交易;

FPGA IP核120用于验证第一交易的签名信息,并向交易池模块1110返回第一交易的第一验证结果。

上述实施例在区块链一体机成本较低的情况下保证tps,保证了区块链一体机的整体性能。

优选地,CPU IP核还用于将所接收的第一区块的各第二交易发送至FPGA IP核,以及,接收FPGA IP核发送的通知信息,从FPGA IP核获取各第二交易对应的第二验证结果以执行各第二交易;

FPGA IP核还用于验证第一区块中的各第二交易的签名信息,并在全部验证结束时通知CPU IP核。

进一步优选地,FPGA IP核还包括缓存模块和验证模块;其中,

缓存模块用于缓存验证通过的第一交易的第一哈希值;

验证模块用于对各第二交易执行如下操作:

FPGA IP核判断是否缓存有与第二交易的第二交易哈希值相同的第一哈希值:

是,则将不再次验证第二交易的签名信息,并将第二交易的第二验证结果确定为正确;

在全部验证结束时通知CPU IP核。

上述方法可以有效避免重复性检查验证,进一步提高tps。

优选地,FPGA IP核还包括缓存模块和查重模块;其中,

缓存模块用于缓存验证通过的第一交易的第一哈希值;

查重模块用于接收交易池模块发送的第三交易,判断是否缓存有与第三交易的第三交易哈希值相同的第一哈希值:

是,则丢弃第三交易。

上述方法可以有效避免重复性检查验证,进一步提高tps。

优选地,FPGA IP核还包括多个验证模块,多个验证模块用于并行验证不同交易的签名信息。

本发明还提供一种区块链网络,区块链网络包括若干如图5及其优选实施方式所示的区块链一体机。

描述于本申请实施例中所涉及到的单元或模块可以通过软件的方式实现,也可以通过硬件的方式来实现。所描述的单元或模块也可以设置在处理器中,例如,各单元可以是设置在计算机或移动智能设备中的软件程序,也可以是单独配置的硬件装置。其中,这些单元或模块的名称在某种情况下并不构成对该单元或模块本身的限定。

以上描述仅为本申请的较佳实施例以及对所运用技术原理的说明。本领域技术人员应当理解,本申请中所涉及的发明范围,并不限于上述技术特征的特定组合而成的技术方案,同时也应涵盖在不脱离本申请构思的情况下,由上述技术特征或其等同特征进行任意组合而形成的其它技术方案。例如上述特征与本申请中公开的(但不限于)具有类似功能的技术特征进行互相替换而形成的技术方案。

- 交易执行方法、区块链一体机和区块链网络

- 区块链交易执行方法、区块链节点及控制装置