一种SIC功率半导体器件及其模块

文献发布时间:2023-06-19 10:38:35

技术领域

本发明属于功率半导体技术领域,尤其涉及一种SIC功率半导体器件及其模块。

背景技术

传统以硅为材料的功率半导体,正逐渐面临发展瓶颈,碳化硅功率器件的能量损耗只有硅器件的功率30%-80%,发热量也只有硅器件的50%,且有更高的电流密度。在相同功率等级下,碳化硅功率模块的体积显著小于硅(Si)功率模块,在电力电子、国防工业等领域有广阔应用前景,国家各级政府在政策给予大力支持,是国家重点引导产业之一。

发明内容

本发明提供一种SIC功率半导体器件及其模块,旨在解决现有技术存在的问题。

本发明是这样实现的,一种SIC功率半导体器件,包括SIC衬底、SIC外延层、绝缘层、源极、栅极和漏极;

所述SIC外延层形成于所述SIC衬底的顶部;

所述SIC外延层的顶部具有相对设置的第一区域和第二区域,每一个所述第一区域和所述第二区域内分别凹陷形成有一个第一沟槽和一个第二沟槽,所述第一沟槽内覆盖有第一金属层,所述第二沟槽内覆盖有第二金属层;

所述SIC外延层的顶部覆盖有绝缘层,所述绝缘层具有两个对称设置的通孔,两个所述通孔内分别设置有所述源极和所述漏极,所述源极接触所述第一金属层,所述漏极接触所述第二金属层;所述栅极设置在所述绝缘层的上表面且位于所述源极和所述漏极之间;

所述第一区域与所述SIC外延层为不同导电类型;

所述第二区域与所述SIC外延层为相同的导电类型。

优选的,所述绝缘层的材料为SiO

优选的,所述绝缘层的厚度为10~40nm。

优选的,所述沟槽采用干法刻蚀或湿法刻蚀制备而成。

优选的,所述沟槽采用ICP-RIE刻蚀法制备而成。

优选的,所述SIC外延层的厚度为80μm。

优选的,所述SIC外延层采用高温化学气相沉积法制备而成,掺杂浓度范围在1015~1019cm,表面宏观缺陷密度小于8cm

优选的,所述沟槽的深度为50nm~300nm。

优选的,所述SIC衬底的厚度为5~10μm。

本发明还提供一种SIC功率半导体模块,包括如上述任意一种SIC功率半导体器件。

与现有技术相比,本发明的有益效果是:本发明的一种SIC功率半导体器件及其模块,通过设置SIC衬底、SIC外延层、绝缘层、源极、栅极和漏极;并且SIC外延层形成于SIC衬底的顶部;SIC外延层的顶部具有相对设置的第一区域和第二区域,SIC外延层的顶部覆盖有绝缘层,绝缘层具有两个对称设置的通孔,两个通孔内分别设置有源极和漏极,源极接触第一金属层,漏极接触第二金属层;栅极设置在绝缘层的上表面且位于源极和漏极之间。从而实现具有高耐压性能和低开启电压的功率半导体,使用更安全,适用范围更广。

附图说明

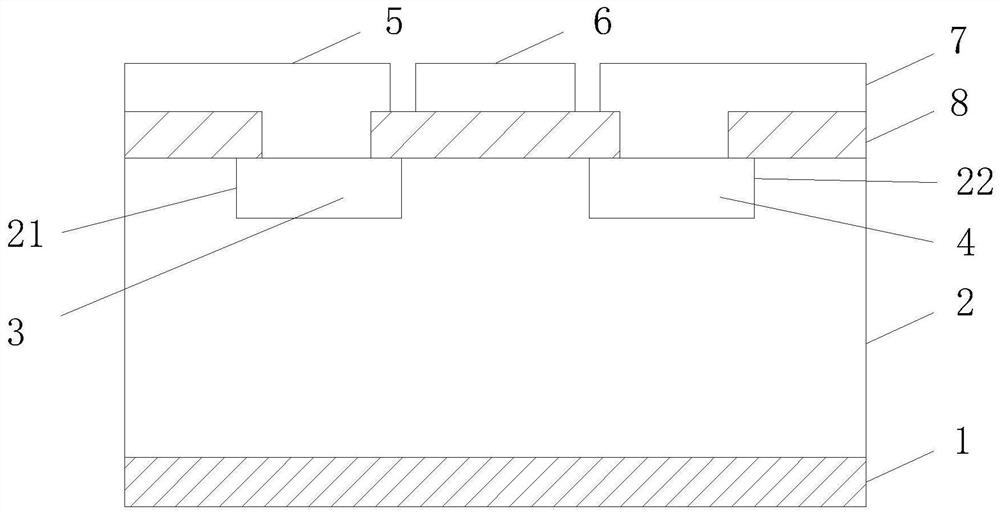

图1为本发明的一种SIC功率半导体器件的整体结构示意图。

图中:1-SIC衬底、2-SIC外延层、21-第一区域、22-第二区域、3-第一金属层、4-第二金属层、5-源极、6-栅极、7-漏极、8-绝缘层。

具体实施方式

为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

实施例1

请参阅图1,本实施例提供一种技术方案:一种SIC功率半导体器件及其模块,功率半导体器件包括SIC衬底1、SIC外延层2、绝缘层4、源极5、栅极6和漏极7。

SIC外延层2形成于SIC衬底1的顶部。SIC衬底1的厚度为5~10μm。

SIC外延层2的顶部具有相对设置的第一区域21和第二区域22,每一个第一区域和第二区域内分别凹陷形成有一个第一沟槽和一个第二沟槽,第一沟槽内覆盖有第一金属层3,第二沟槽内覆盖有第二金属层4。

SIC外延层2的顶部覆盖有绝缘层8,绝缘层8具有两个对称设置的通孔,两个通孔内分别设置有源极5和漏极7,源极5接触第一金属层3,漏极7接触第二金属层3;栅极6设置在绝缘层8的上表面且位于源极5和漏极7之间。第一区域21与SIC外延层2为不同导电类型。形成PN结,第二区域22与SIC外延层2为相同的导电类型。

绝缘层4的材料为SiO

SIC外延层2的厚度为80μm。SIC外延层2采用高温化学气相沉积法制备而成,掺杂浓度范围在1015~1019cm,表面宏观缺陷密度小于8cm

利用HTCVD法制备的高阻SIC衬底1。通过添加含氯元素的先驱体源,实现厚膜外延材料,单层外延层厚度达80微米,掺杂浓度范围在1015-1019cm,表面宏观缺陷密度小于8cm-2。在SiC外延生长技术开发方面,工业界普通CVD法外延非掺杂有源层,厚度仅有20多微米。本项目突破厚膜生长的重复性、稳定性、一致性等产业化瓶颈共性技术,获得高质量的6英寸碳化硅外延材料。

本实施例的一种SIC功率半导体模块,包括上述的一种SIC功率半导体器件。

实施例2

请参阅图1,本实施例提供一种技术方案:一种SIC功率半导体器件及其模块,功率半导体器件包括SIC衬底1、SIC外延层2、绝缘层4、源极5、栅极6和漏极7。

SIC外延层2形成于SIC衬底1的顶部。SIC衬底1的厚度为5~10μm。

SIC外延层2的顶部具有相对设置的第一区域21和第二区域22,每一个第一区域和第二区域内分别凹陷形成有一个第一沟槽和一个第二沟槽,第一沟槽内覆盖有第一金属层3,第二沟槽内覆盖有第二金属层4。

SIC外延层2的顶部覆盖有绝缘层8,绝缘层8具有两个对称设置的通孔,两个通孔内分别设置有源极5和漏极7,源极5接触第一金属层3,漏极7接触第二金属层3;栅极6设置在绝缘层8的上表面且位于源极5和漏极7之间。第一区域21与SIC外延层2为不同导电类型。形成PN结,第二区域22与SIC外延层2为相同的导电类型。

绝缘层4的材料为Al

SIC外延层2的厚度为80μm。SIC外延层2采用高温化学气相沉积法制备而成,掺杂浓度范围在1015~1019cm,表面宏观缺陷密度小于8cm

本实施例的一种SIC功率半导体模块,包括上述的一种SIC功率半导体器件。

实施例3

请参阅图1,本实施例提供一种技术方案:一种SIC功率半导体器件及其模块,功率半导体器件包括SIC衬底1、SIC外延层2、绝缘层4、源极5、栅极6和漏极7。

SIC外延层2形成于SIC衬底1的顶部。SIC衬底1的厚度为5~10μm。

SIC外延层2的顶部具有相对设置的第一区域21和第二区域22,每一个第一区域和第二区域内分别凹陷形成有一个第一沟槽和一个第二沟槽,第一沟槽内覆盖有第一金属层3,第二沟槽内覆盖有第二金属层4。

SIC外延层2的顶部覆盖有绝缘层8,绝缘层8具有两个对称设置的通孔,两个通孔内分别设置有源极5和漏极7,源极5接触第一金属层3,漏极7接触第二金属层3;栅极6设置在绝缘层8的上表面且位于源极5和漏极7之间。第一区域21与SIC外延层2为不同导电类型,形成PN结。第二区域22与SIC外延层2为相同的导电类型,形成欧姆接触。

绝缘层4的材料为AlN。绝缘层4的厚度为10~40nm。沟槽的深度为50nm~300nm。沟槽采用干法刻蚀制备而成。

SIC外延层2的厚度为80μm。SIC外延层2采用高温化学气相沉积法制备而成,掺杂浓度范围在1015~1019cm,表面宏观缺陷密度小于8cm

本实施例的一种SIC功率半导体模块,包括上述的一种SIC功率半导体器件。

实施例4

请参阅图1,本实施例提供一种技术方案:一种SIC功率半导体器件及其模块,功率半导体器件包括SIC衬底1、SIC外延层2、绝缘层4、源极5、栅极6和漏极7。

SIC外延层2形成于SIC衬底1的顶部。SIC衬底1的厚度为5~10μm。

SIC外延层2的顶部具有相对设置的第一区域21和第二区域22,每一个第一区域和第二区域内分别凹陷形成有一个第一沟槽和一个第二沟槽,第一沟槽内覆盖有第一金属层3,第二沟槽内覆盖有第二金属层4。

SIC外延层2的顶部覆盖有绝缘层8,绝缘层8具有两个对称设置的通孔,两个通孔内分别设置有源极5和漏极7,源极5接触第一金属层3,漏极7接触第二金属层3;栅极6设置在绝缘层8的上表面且位于源极5和漏极7之间。第一区域21与SIC外延层2为不同导电类型。形成PN结,第二区域22与SIC外延层2为相同的导电类型。

绝缘层4的材料为AlON。绝缘层4的厚度为10~40nm。沟槽的深度为50nm~300nm。沟槽采用湿法刻蚀制备而成。

SIC外延层2的厚度为80μm。SIC外延层2采用高温化学气相沉积法制备而成,掺杂浓度范围在1015~1019cm,表面宏观缺陷密度小于8cm

本实施例的一种SIC功率半导体模块,包括上述的一种SIC功率半导体器件。

实施例5

请参阅图1,本实施例提供一种技术方案:一种SIC功率半导体器件及其模块,功率半导体器件包括SIC衬底1、SIC外延层2、绝缘层4、源极5、栅极6和漏极7。

SIC外延层2形成于SIC衬底1的顶部。SIC衬底1的厚度为5~10μm。

SIC外延层2的顶部具有相对设置的第一区域21和第二区域22,每一个第一区域和第二区域内分别凹陷形成有一个第一沟槽和一个第二沟槽,第一沟槽内覆盖有第一金属层3,第二沟槽内覆盖有第二金属层4。

SIC外延层2的顶部覆盖有绝缘层8,绝缘层8具有两个对称设置的通孔,两个通孔内分别设置有源极5和漏极7,源极5接触第一金属层3,漏极7接触第二金属层3;栅极6设置在绝缘层8的上表面且位于源极5和漏极7之间。第一区域21与SIC外延层2为不同导电类型。形成PN结,第二区域22与SIC外延层2为相同的导电类型。

绝缘层4的材料为HfO

SIC外延层2的厚度为80μm。SIC外延层2采用高温化学气相沉积法制备而成,掺杂浓度范围在1015~1019cm,表面宏观缺陷密度小于8cm

本实施例的一种SIC功率半导体模块,包括上述的一种SIC功率半导体器件。

综上所述,本发明的一种SIC功率半导体器件及其模块,通过设置SIC衬底1、SIC外延层2、绝缘层8、源极5、栅极6和漏极7;并且SIC外延层2形成于SIC衬底1的顶部;SIC外延层2的顶部具有相对设置的第一区域21和第二区域22,SIC外延层2的顶部覆盖有绝缘层8,绝缘层8具有两个对称设置的通孔,两个通孔内分别设置有源极5和漏极7,源极5接触第一金属层3,漏极7接触第二金属层4;栅极6设置在绝缘层8的上表面且位于源极5和漏极7之间。从而实现具有高耐压性能和低开启电压的功率半导体,使用更安全,适用范围更广

以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

- 一种SIC功率半导体器件及其模块

- 一种低功耗4H-SiC电压控制型功率半导体器件及其制备方法