输出驱动电路及存储器

文献发布时间:2023-06-19 10:38:35

技术领域

本发明涉及集成电路领域,尤其涉及一种输出驱动电路及存储器。

背景技术

LPDDR4(Low Power Double Data Rate SDRAM 4)和LPDDR4X的应用中,都是采用了LVSTL(Low Voltage Swing Terminated Logic)的高速接口标准。LPDDR4JEDEC标准中输出信号幅度可以设置成VDDQ/3或者是VDDQ/2,传统的设计中会把整个预放大级的信号占空比设计为50%,但是由于输出幅度为VDDQ/3时,上下阻抗不对称,这样最终输出级的输出信号占空比就会偏离50%很多,从而影响高速信号传输的质量,减少输入接收端的信号容限。另外,随着工艺温度电压的变化,也会引起最终输出级的输出信号占空比的偏离。

因此,亟需一种能够避免输出信号占空比偏离的输出驱动电路。

发明内容

本发明所要解决的技术问题是,提供一种输出驱动电路及存储器,其能够避免在不同输出电压情况下,由于输出阻抗不匹配而导致的输出信号占空比偏离,影响信号质量的问题。

为了解决上述问题,本发明提供了一种输出驱动电路,其包括至少一驱动模块,所述驱动模块包括:信号输入端,输入一控制信号和一具有预设占空比的输入信号,所述输入信号包括互补的正输入信号及负输入信号;上拉NMOS管,其漏极与电源电压连接;上拉电阻,其第一端与所述上拉NMOS管的源极连接;上拉预放大单元,所述上拉预放大单元的输入端接所述信号输入端,所述上拉预放大单元的输出端接所述上拉NMOS管的栅极,所述上拉预放大单元将所述信号输入端的正输入信号放大并改变占空比后输出一第一输出信号,所述第一输出信号具有第一占空比,所述第一占空比比所述预设占空比增大一设定值;下拉NMOS管,其源极接地;下拉电阻,其第二端与所述下拉NMOS管的漏极连接;下拉预放大单元,所述下拉预放大单元的输入端接所述信号输入端,所述下拉预放大单元的输出端接所述下拉NMOS管的栅极,所述下拉预放大单元将所述信号输入端的负输入信号放大并改变占空比后输出第二输出信号,所述第二输出信号具有一第二占空比,所述第二占空比比所述预设占空比减小所述设定值;信号输出端,与所述上拉电阻的第二端及所述下拉电阻的第一端连接,输出第三输出信号,所述第三输出信号具有一第三占空比,所述第三占空比与所述预设占空比相等。

进一步,所述上拉预放大单元包括至少一占空比调整单元一及至少一占空比控制单元一,所述占空比调整单元一的输入端接所述正输入信号,所述占空比控制单元一的输入端接控制信号,所述占空比控制单元一的输出端连接所述占空比调整单元一并可以调节所述占空比调整单元一的输出信号占空比的大小。

进一步,所述占空比调整单元一包括至少一反相器组,所述反相器组包括串联的第一反相器及第二反相器,所述第一反相器包括多个并联的PMOS管组成的第一PMOS管阵列及多个并联的NMOS管组成的第一NMOS管阵列,所述第二反相器包括多个并联的PMOS管组成的第二PMOS管阵列及多个并联的NMOS管组成的第二NMOS管阵列;所述占空比控制单元一输出一第一占空比控制信号至所述第一反相器的输入端;所述第一反相器根据所述第一占空比控制信号及所述正输入信号调整所述第一PMOS管阵列中的PMOS管导通的数量及第一NMOS管阵列中NMOS管导通的数量,并输出一第一反相器输出信号,所述第二反相器接收所述第一反相器输出信号,以使所述第一输出信号的第一占空比比所述预设占空比增大所述设定值。

进一步,所述占空比控制单元一还能够输出一第二占空比控制信号至所述第二反相器的输入端,所述第二反相器根据所述第二占空比控制信号及所述第一反相器输出信号调整所述第二PMOS管阵列中的PMOS导通的数量及第二NMOS管阵列中NMOS管导通的数量,以使所述第一输出信号的第一占空比比所述预设占空比增大所述设定值。

进一步,所述第一反相器根据所述第一占空比控制信号及所述输入信号减小或增大所述第一PMOS管阵列中的PMOS管导通的数量及增大或减少第一NMOS管阵列中NMOS管导通的数量,以使所述第一输出信号的第一占空比比所述预设占空比增大所述设定值。

进一步,所述上拉预放大单元还包括至少一放大器一,所述放大器一的输入端接所述占空比调整单元一的输出端,所述放大器一的输出端为所述上拉预放大单元的输出端。

进一步,所述下拉预放大单元包括至少一占空比调整单元二及至少一占空比控制单元二,所述占空比调整单元二的输入端接负输入信号,所述占空比控制单元二的输入端接控制信号,所述占空比控制单元二的输出端连接所述占空比调整单元二并可以调节所述占空比调整单元二的输出信号占空比的大小。

进一步,所述占空比调整单元二包括至少一反相器组,所述反相器组包括串联的第三反相器及第四反相器,所述第三反相器包括多个并联的PMOS管组成的第三PMOS管阵列及多个并联的NMOS管组成的第三NMOS管阵列,所述第四反相器包括多个并联的PMOS管组成的第四PMOS管阵列及多个并联的NMOS管组成的第四NMOS管阵列;所述占空比控制单元二输出一第三占空比控制信号至所述第三反相器的输入端;所述第三反相器根据所述第三占空比控制信号及所述负输入信号调整所述第三PMOS管阵列中的PMOS管导通的数量及第三NMOS管阵列中NMOS管导通的数量,并输出一第三反相器输出信号,所述第四反相器接收所述第三反相器输出信号,以使所述第二输出信号的第二占空比比所述预设占空比减小所述设定值。

进一步,所述占空比控制单元二还能够输出一第二占空比控制信号至所述第二反相器的输入端,所述第二反相器根据所述第二占空比控制信号及所述第一反相器输出信号调整所述第二PMOS管阵列中的PMOS管导通的数量及第二NMOS管阵列中NMOS管导通的数量,以使所述第二输出信号的第二占空比比所述预设占空比减小所述设定值。

进一步,所述第三反相器根据所述第三占空比控制信号及所述负输入信号增大或减少所述第三PMOS管阵列中的PMOS管导通的数量及减小或增大第三NMOS管阵列中NMOS管导通的数量,以使所述第二输出信号的第二占空比比所述预设占空比减小所述设定值。

进一步,所述下拉预放大单元还包括至少一放大器二,所述放大器二与所述占空比调整单元二串联。

进一步,所述输出驱动电路包括多个相同的驱动模块,所述驱动模块并联。

进一步,所述预设占空比为0.5,所述设定值的绝对值大于0且小于0.4。

本发明还提供一种存储器,其包括如上所述的输出驱动电路。

本发明驱动输出电路在信号输入端及信号输出端之间设置上拉预放大单元及下拉预放大单元,所述上拉预放大单元及下拉预放大单元对正输入信号与负输入信号的占空比进行调整,使得信号输出端的输出信号与信号输入端的输入信号的占空比相同,避免了在不同输出电压情况下,由于输出阻抗不匹配而导致的输出信号占空比偏离,影响信号质量的问题。

附图说明

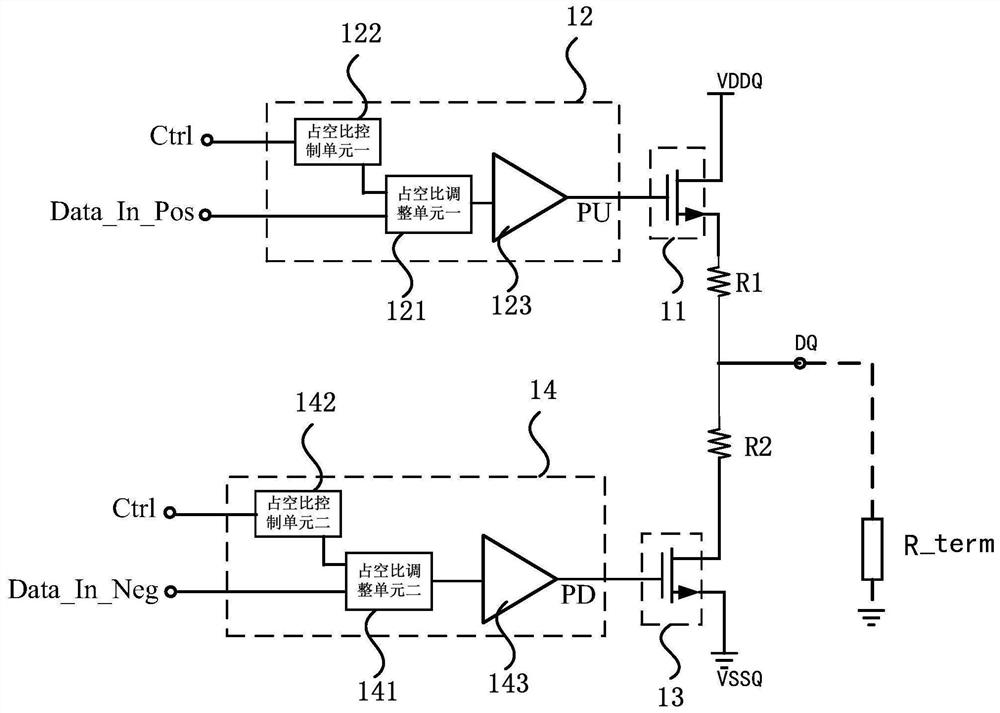

图1是本发明驱动输出电路的第一具体实施方式的结构示意图;

图2为本发明驱动输出电路的驱动模块的第一具体实施方式的电路图;

图3是信号输入端的正输入信号Data_In_Pos及所述上拉预放大单元的第一输出信号PU的时序图;

图4是信号输入端的正输入信号Data_In_Pos及所述上拉预放大单元的第一输出信号PU的另一时序图;

图5是所述占空比调整单元一的一具体实施方式的电路图;

图6是信号输入端的负输入信号Data_In_Neg及所述下拉预放大单元的第二输出信号PD的时序图;

图7是信号输入端的负输入信号Data_In_Neg及所述下拉预放大单元的第二输出信号PD的另一时序图;

图8是所述占空比调整单元二的一具体实施方式的电路图。

具体实施方式

下面结合附图对本发明提供的输出驱动电路及存储器的具体实施方式做详细说明。

图1是本发明驱动输出电路的第一具体实施方式的结构示意图。请参阅图1,所述驱动输出电路包括至少一驱动模块10。在本具体实施方式中,所述驱动输出电路包括多个并联的所述驱动模块10,所述驱动模块10的布局相同。本发明驱动输出电路中驱动模块10复用,可以极大地简化电路的设计和版图的实现,提高驱动模块间的匹配度,减小电路间的寄生,特别是高速信号线,从而提高电路高速运行下的性能。

如背景技术所述,并请参阅图2,LPDDR4JEDEC标准中输出信号幅度可以设置成VDDQ/3或者是VDDQ/2,传统的设计中会把整个预放大级的信号占空比设计为50%。当信号输出端DQ的输出幅度为VDDQ/2时,输出级的输出信号占空比不会偏离,但是当信号输出端DQ输出幅度为VDDQ/3时,上拉NMOS管11和电阻R1的等效阻抗之和与电阻R_term的阻抗不对称,这使得的信号输出端DQ的输出信号占空比就会偏离50%很多,从而影响高速信号传输的质量,减少输入接收端的信号容限。另外,随着工艺温度电压的变化,也会引起最终输出级的输出信号占空比的偏离。

为了解决上述技术问题,本发明提供了如下的驱动输出电路的驱动模块。

图2为本发明驱动输出电路的驱动模块的第一具体实施方式的电路图。请参阅图2,所述驱动模块10包括信号输入端、上拉NMOS管11、上拉电阻R1、上拉预放大单元12、下拉NMOS管13、下拉电阻R2、下拉预放大单元14及信号输出端DQ。

所述信号输入端输入一控制信号Ctrl和一具有预设占空比的输入信号。所述输入信号包括互补的正输入信号Data_In_Pos及负输入信号Data_In_Neg。所述输入信号为由前级经过并串转换后的信号。

所述上拉NMOS管11具有源极、漏极及栅极。所述上拉NMOS管11的漏极与电源电压VDDQ连接,所述上拉NMOS管11的源极与所述上拉电阻R1的第一端连接,所述上拉NMOS管11的栅极与所述上拉预放大单元12连接。所述上拉NMOS管11输出一输出信号DQ。

所述上拉电阻R1的第一端与所述上拉NMOS管11的源极连接,第二端与所述信号输出端DQ连接。

所述上拉预放大单元12的输入端接所述信号输入端,具体地说,所述上拉预放大单元12的输入端接所述信号输入端的正输入信号Data_In_Pos。所述上拉预放大单元12的输出端接所述上拉NMOS管11的栅极。所述上拉预放大单元12将所述信号输入端的正输入信号Data_In_Pos放大并改变占空比后输出一第一输出信号PU。所述第一输出信号PU作为所述上拉NMOS管11的驱动信号。

所述第一输出信号PU具有一第一占空比。所述第一占空比比所述预设占空比增大一设定值Δ,所述设定值Δ可以为正值,也可以为负值。若所述设定值Δ为正值,则所述第一占空比比所述预设占空比大,若所述设定值Δ为负值,则所述第一占空比比所述预设占空比小。其中,在本发明一具体实施方式中,所述预设占空比为0.5,所述设定值Δ的绝对值大于0且小于0.4。

在本发明第一具体实施方式中,所述设定值Δ为正值,即所述第一占空比比预设占空比大。请参阅图3,其为信号输入端的正输入信号Data_In_Pos及所述上拉预放大单元12的第一输出信号PU的时序图,在第一输出信号PU的时序图上采用虚线示意性绘示了正输入信号Data_In_Pos的位置,经所述上拉预放大单元12后,驱动所述上拉NMOS管11的第一输出信号PU的第一占空比比所述正输入信号Data_In_Pos的预设占空比增大了设定值Δ,即所述上拉NMOS管11的导通时间占比增加了Δ,所述上拉NMOS管11的输出信号DQ的占空比增加了设定值Δ。

在本发明第二具体实施方式中,所述设定值Δ为负值,即所述第一占空比比预设占空比小。请参阅图4,其为信号输入端的正输入信号Data_In_Pos及所述上拉预放大单元12的第一输出信号PU的时序图,经所述上拉预放大单元12后,驱动所述上拉NMOS管11的第一输出信号PU的第一占空比比所述正输入信号Data_In_Pos的预设占空比减小了设定值Δ,即所述上拉NMOS管11的导通时间占比减小了Δ,所述上拉NMOS管11的输出信号DQ的占空比减小了设定值Δ。

请继续参阅图2,所述上拉预放大单元12包括至少一占空比调整单元一121及至少一占空比控制单元一122,所述占空比调整单元一121的输入端接所述正输入信号Data_In_Pos,所述占空比控制单元一122的输入端接控制信号Ctrl,所述占空比控制单元一122的输出端连接所述占空比调整单元一121的输入端。

所述占空比控制单元一122与所述正输入信号Data_In_Pos组合,以调节所述占空比调整单元一121的输出信号的占空比的大小。在本具体实施方式中,所述上拉预放大单元12包括一个占空比调整单元一121及一个占空比控制单元一122。

进一步,在第一具体实施方式中,所述上拉预放大单元12还包括至少一放大器一123,所述放大器一123的输入端接所述占空比调整单元一121的输出端,所述放大器一123的输出端为所述上拉预放大单元12的输出端。也就是说,正输入信号Data_In_Pos经所述占空比调整单元一121及放大器一123后,其占空比被调整,信号被放大,形成具有第一占空比的第一输出信号PU。

下面举例说明所述占空比调整单元一的一具体实施方式。图5是所述占空比调整单元一的一具体实施方式的电路图。请参阅图5,所述占空比调整单元一121包括至少一反相器组A。所述反相器组A包括串联的第一反相器A1及第二反相器A2。所述第一反相器A1包括多个并联的PMOS管Mp1_PU_adj<0:n>组成的第一PMOS管阵列及多个并联的NMOS管Mn1_PU_adj<0:n>组成的第一NMOS管阵列;所述第二反相器A2包括多个并联的PMOS管Mp2_PU_adj<0:m>组成的第二PMOS管阵列及多个并联的NMOS管Mn2_PU_adj<0:m>组成的第二NMOS管阵列。其中n表示第一PMOS管阵列中并联的PMOS管的数量及第一NMOS管阵列中并联的NMOS管的数量,m表示第二PMOS管阵列中并联的PMOS管的数量及第二NMOS管阵列中并联的NMOS管的数量。在本具体实施方式中,所述第一反相器A1与所述第二反相器A2串联,使得输入信号经所述反相器组A后同相输出。

所述占空比控制单元一122输出第一占空比控制信号Mp1_PU<0:n>和Mn1_PU<0:n>分别至Mp1_PU_adj<0:n>组成的第一PMOS管阵列的栅极和Mn1_PU_adj<0:n>组成的第一NMOS管阵列的栅极;所述第一反相器A1根据所述第一占空比控制信号Mp1_PU<0:n>和Mn1_PU<0:n>分别调整所述第一PMOS管阵列中的PMOS导通的数量及第一NMOS管阵列中NMOS管导通的数量,并输出一第一反相器输出信号out1_pos,所述第二反相器A2接收所述第一反相器输出信号out1_pos,并输出一第二反相器输出信号out2_pos,所述第二反相器输出信号out2_pos的占空比比所述正输入信号Data_In_Pos的预设占空比增大或减小。也就是说,所述占空比控制单元一122通过调整所述第一PMOS管阵列及第一NMOS管阵列导通的晶体管的数量,即所述第一PMOS管阵列及第一NMOS管阵列的尺寸,从而控制所述第二反相器输出信号out2_pos的占空比。

在本具体实施方式中,所述占空比调整单元一121包括一个反相器组A。所述反相器组A包括串联的第一反相器A1及第二反相器A2,则经所述第二反相器A2输出的第二反相器输出信号out2_pos的占空比比所述正输入信号Data_In_Pos的预设占空比增大所述设定值Δ,进而使得所述第一输出信号PU的第一占空比比所述预设占空比增大所述设定值Δ,进而使得信号输出端DQ的占空比为50%。在本发明其他具体实施方式中,所述占空比调整单元一121包括多个反相器组A,则经最后一个反相器A输出的输出信号的占空比比所述正输入信号Data_In_Pos的预设占空比减小所述设定值Δ,即占空比经多个反相器组A调整而使输出信号PU占空比比减小所述设定值Δ,进而使得信号输出端DQ的占空比为50%。

具体地说,在本具体实施方式中,所述设定值Δ为正值,所述占空比控制单元一122输出的第一占空比控制信号Mp1_PU<0:n>和Mn1_PU<0:n>与所述正输入信号Data_In_Pos组合形成一总的控制信号输入至所述第一反相器A1。所述第一反相器A1根据所述总控制信号减小所述第一PMOS管阵列中的PMOS导通的数量及增大所述第一NMOS管阵列中NMOS管导通的数量,所述第一反相器输出信号out1_pos中低电平占比大于高电平占比。所述第二反相器A1被该第一反相器输出信号out1_pos驱动后,第二反相器输出信号out2_pos中低电平占比小于高电平占比,该第二反相器输出信号out2_pos的占空比比正输入信号Data_In_Pos的预设占空比增大设定值|Δ|。该第二反相器输出信号out2_pos经所述放大器一123后形成具有第一占空比的第一输出信号PU,所述第一输出信号PU的第一占空比比预设占空比增大设定值|Δ|,所述第一输出信号PU驱动上拉NMOS管11,使得上拉NMOS管11的导通时间增加,从而使得DQ的占空比为50%。

在本发明第二具体实施方式中,所述设定值Δ为负值,所述占空比控制单元一122输出的第一占空比控制信号Mp1_PU<0:n>和Mn1_PU<0:n>与所述正输入信号Data_In_Pos组合形成一总的控制信号输入至所述第一反相器A1。所述第一反相器A1根据所述总控制信号增大所述第一PMOS管阵列中的PMOS导通的数量及减小所述第一NMOS管阵列中NMOS管导通的数量,所述第一反相器输出信号out1_pos中低电平占比小于高电平占比。所述第二反相器A1被该第一反相器输出信号out1_pos驱动后,第二反相器输出信号out2_pos中高电平占比小于低电平占比,该第二反相器输出信号out2_pos的占空比比正输入信号Data_In_Pos的预设占空比减小设定值|Δ|。该第二反相器输出信号out2_pos经所述放大器一123后形成具有第一占空比的第一输出信号PU,所述第一输出信号PU的第一占空比比预设占空比减小设定值|Δ|,所述第一输出信号PU驱动上拉NMOS管11,使得上拉NMOS管11的导通时间减小。

进一步,在第一具体实施方式中,所述占空比控制单元一122还能够输出一第二占空比控制信号Mp2_PU<0:n>和Mn2_PU<0:n>分别至Mp2_PU_adj<0:n>组成的第二PMOS管阵列的栅极和Mn2_PU_adj<0:n>组成的第二NMOS管阵列的栅极,所述第二反相器A2根据所述第二占空比控制信号Mp2_PU<0:n>和Mn2_PU<0:n>及所述第一反相器输出信号out1_pos调整所述第二PMOS管阵列中的PMOS管导通的数量及第二NMOS管阵列中NMOS管导通的数量,以使所述第一输出信号的第一占空比比所述预设占空比增大或减小所述设定值Δ。也就是说,所述正输入信号Data_In_Pos经所述第一反相器A1后,第一反相器输出信号out1_pos的占空比并未被调整至需要数值,则可通过所述第一反相器输出信号out1_pos与所述第二占空比控制信号Mp2_PU<0:n>和Mn2_PU<0:n>形成总控制信号来调整所述第二PMOS管阵列中的PMOS导通的数量及第二NMOS管阵列中NMOS管导通的数量,以使所述第一输出信号的第一占空比比所述预设占空比增大或减小所述设定值Δ。

上述为所述上拉预放大单元的一具体实施方式,在本发明其他具体实施方式中,也可采用其他的方法来实现所述上拉预放大单元的功能。

所述下拉NMOS管13具有源极、漏极及栅极,所述下拉NMOS管13的源极与接地端VSSQ连接,所述下拉NMOS管13的漏极与下拉电阻R2的第二端连接,所述下拉NMOS管13的栅极与所述下拉预放大单元14连接,所述下拉NMOS管13输出一输出信号DQ。

所述下拉电阻R2的第一端与所述信号输出端DQ连接,第二端与所述下拉NMOS管13的漏极连接。

所述下拉预放大单元14输入端接所述信号输入端。具体地说,所述下拉预放大单元14输入端接所述信号输入端的负输入信号Data_In_Neg。所述下拉预放大单元14的输出端接所述下拉PMOS管13的栅极。所述下拉预放大单元14将所述信号输入端的负输入信号Data_In_Neg放大并改变占空比后输出一第二输出信号PD。所述第二输出信号PD作为所述下拉PMOS管13的驱动信号。

所述第二输出信号PD具有一第二占空比,所述第二占空比比所述预设占空比减小所述设定值Δ。也就是说,所述第二输出信号PD与所述第一输出信号PU的占空比的变化量相同,变化方向相反。具体的说,若所述第一输出信号PU的第一占空比比预设占空比增大|Δ|,则所述第二输出信号PD的第二占空比比预设占空比减小|Δ|;若所述第一输出信号PU的第一占空比比预设占空比减小|Δ|,则所述第二输出信号PD的第二占空比比预设占空比增大|Δ|。

在本发明第一具体实施方式中,所述设定值Δ为正值,即所述第二占空比比预设占空比减小。请参阅图6,其为信号输入端的负输入信号Data_In_Neg的时序图及所述下拉预放大单元14的第二输出信号PD的时序图,经所述下拉预放大单元14后,驱动所述下拉PMOS管13的第二输出信号PD的第二占空比比所述负输入信号Data_In_Neg的预设占空比减小了设定值Δ,即所述下拉NMOS管13的导通时间占比减少了Δ。在本发明第二具体实施方式中,所述设定值Δ为负值,即所述第二占空比比预设占空比大。请参阅图7,其为信号输入端的负输入信号Data_In_Neg的时序图及所述下拉预放大单元14的第二输出信号PD的时序图,经所述下拉预放大单元14后,驱动所述下拉NMOS管13的第二输出信号PD的第二占空比比所述负输入信号Data_In_Neg的预设占空比增加了设定值|Δ|,即所述下拉NMOS管13的导通时间占比增加了|Δ|。

请继续参阅图2,所述下拉预放大单元14包括至少一占空比调整单元二141及至少一占空比控制单元二142,所述占空比调整单元二141的输入端接所述负输入信号Data_In_Neg,所述占空比控制单元二142的输入端接控制信号Ctrl,所述占空比控制单元二142的输出端连接所述占空比调整单元二141的输入端。

所述占空比控制单元二142与所述负输入信号Data_In_Neg组合,以调节所述占空比调整单元二141的输出信号的占空比的大小。在本具体实施方式中,所述下拉预放大单元14包括一个占空比调整单元二141及一个占空比控制单元二142。

进一步,在第一具体实施方式中,所述下拉预放大单元14还包括至少一放大器二143,所述放大器二143的输入端接所述占空比调整单元二141的输出端,所述放大器二143的输出端为所述下拉预放大单元14的输出端。也就是说,负输入信号Data_In_Neg经所述下拉预放大单元14及放大器二143后,其占空比被调整,信号被放大,形成具有第二占空比的第二输出信号PD。

下面举例说明所述占空比调整单元一的一具体实施方式。图8是所述占空比调整单元二的一具体实施方式的电路图。请参阅图8,所述占空比调整单元二141包括至少一反相器组A。所述反相器组A包括串联的第三反相器A3及第四反相器A4。所述第三反相器A3包括多个并联的PMOS管Mp1_PD_adj<0:n>组成的第三PMOS管阵列及多个并联的NMOS管Mn1_PD_adj<0:n>组成的第三NMOS管阵列;所述第四反相器A4包括多个并联的PMOS管Mp2_PD_adj<0:m>组成的第四PMOS管阵列及多个并联的NMOS管Mn2_PD_adj<0:m>组成的第四NMOS管阵列。其中n表示第三PMOS管阵列中并联的PMOS管的数量及第三NMOS管阵列中并联的NMOS管的数量,m表示第四PMOS管阵列中并联的PMOS管的数量及第四NMOS管阵列中并联的NMOS管的数量。在本具体实施方式中,所述第三反相器A3与所述第四反相器A4串联,使得输入信号经所述反相器组A后同相输出。

所述占空比控制单元二142输出一第三占空比控制信号Mp1_PD<0:n>和Mn1_PD<0:n>分别至Mp1_PD_adj<0:n>组成的第一PMOS管阵列的栅极和Mn1_PD_adj<0:n>组成的第一NMOS管阵列的栅极;所述第三反相器A3根据所述第三占空比控制信号Mp1_PD<0:n>和Mn1_PD<0:n>分别调整所述第三PMOS管阵列中的PMOS导通的数量及第三NMOS管阵列中NMOS管导通的数量,并输出一第三反相器输出信号out3_pos,所述第四反相器A4接收所述第三反相器输出信号out3_pos,并输出一第四反相器输出信号out4_pos,所述第四反相器输出信号out4_pos的占空比比所述负输入信号Data_In_Neg的预设占空比减小或增大。也就是说,所述占空比控制单元二142通过调整所述第三PMOS管阵列及第三NMOS管阵列导通的晶体管的数量,即所述第三PMOS管阵列及第三NMOS管阵列的尺寸,从而控制所述第四反相器输出信号out4_neg的占空比。

在本具体实施方式中,所述占空比调整单元二141包括一个反相器组A。所述反相器组A包括串联的第三反相器A3及第四反相器A4,则经所述第四反相器A4输出的第四反相器输出信号out4_pos的占空比比所述负输入信号Data_In_Neg的预设占空比减小所述设定值Δ,进而使得所述第二输出信号PD的第二占空比比所述预设占空比减小所述设定值Δ,进而使得信号输出端DQ的占空比为50%。在本发明其他具体实施方式中,所述占空比调整单元二141包括多个反相器组A,则经最后一个反相器A输出的输出信号的占空比比所述负输入信号Data_In_Neg的预设占空比增大所述设定值Δ,即占空比经多个反相器组A调整而使输出信号PU占空比比增大所述设定值Δ,进而使得信号输出端DQ的占空比为50%。

具体地说,在本具体实施方式中,所述设定值Δ为正值,所述占空比控制单元二142输出的第三占空比控制信号Mp1_PD<0:n>和Mn1_PD<0:n>与所述负输入信号Data_In_Neg组合形成一总的控制信号输入至所述第三反相器A3。所述第三反相器A3根据所述总控制信号增大所述第三PMOS管阵列中的PMOS导通的数量及减小所述第一NMOS管阵列中NMOS管导通的数量,所述第三反相器输出信号out3_neg中高电平占比大于低电平占比。所述第四反相器A4被该第三反相器输出信号out3_neg驱动后,第四反相器输出信号out4_neg中低电平占比大于高电平占比,该第四反相器输出信号out4_neg的占空比比负输入信号Data_In_Neg的预设占空比减小设定值|Δ|。该第四反相器输出信号out4_neg经所述放大器二143后形成具有第二占空比的第二输出信号PD,所述第二输出信号PD的第二占空比比预设占空比减小设定值|Δ|,所述第二输出信号PD驱动下拉NMOS管13,使得下拉NMOS管13的导通时间减小。

在本发明第二具体实施方式中,所述设定值Δ为负值,所述占空比控制单元二142输出的第三占空比控制信号Mp1_PD<0:n>和Mn1_PD<0:n>与所述负输入信号Data_In_Neg组合形成一总的控制信号输入至所述第三反相器A3。所述第三反相器A3根据所述总控制信号减少所述第三PMOS管阵列中的PMOS导通的数量及增大所述第三NMOS管阵列中NMOS管导通的数量,所述第三反相器输出信号out3_neg中低电平占比大于高电平占比。所述第四反相器A4被该第三反相器输出信号out3_neg驱动后,第四反相器输出信号out4_neg中高电平占比大于低电平占比,该第四反相器输出信号out4_neg的占空比比负输入信号Data_In_Neg的预设占空比大设定值|Δ|。该第四反相器输出信号out4_neg经所述放大器二143后形成具有第二占空比的第二输出信号PD,所述第二输出信号PD的第二占空比比预设占空比则增大设定值|Δ|,所述第二输出信号PD驱动下拉NMOS管13,使得下拉NMOS管13的导通时间增加。

进一步,在第一具体实施方式中,所述占空比控制单元二142还能够输出一第四占空比控制信号Mp2_PD<0:n>和Mn2_PD<0:n>至所述第四反相器A4的输入端,所述第四反相器A4根据所述第四占空比控制信号Mp2_PD<0:n>和Mn2_PD<0:n>及所述第三反相器输出信号out3_nge调整所述第四PMOS管阵列中的PMOS导通的数量及第四NMOS管阵列中NMOS管导通的数量,以使所述第二输出信号的第二占空比比所述预设占空比减小所述设定值Δ。也就是说,所述负输入信号Data_In_Neg经所述第三反相器A3后,第三反相器输出信号out3_neg的占空比并未被调整至需要数值,则可通过所述第三反相器输出信号out3_neg与所述第四占空比控制信号Mp2_PD<0:n>和Mn2_PD<0:n>形成总控制信号来调整所述第四PMOS管阵列中的PMOS导通的数量及第四NMOS管阵列中NMOS管导通的数量,以使所述第二输出信号的第二占空比比所述预设占空比减小所述设定值Δ。

上述为所述下拉预放大单元的一具体实施方式,在本发明其他具体实施方式中,也可采用其他的方法来实现所述下拉预放大单元的功能。

信号输出端DQ与所述上拉电阻R1的第二端及所述下拉电阻R2的第一端连接,信号输出端DQ的占空比与所述预设占空比相等,在一具体实施例中为0.5。

随着输出驱动电路所处的工艺温度电压等的变化,在输入信号传输的过程中,信号的占空比会发生偏移,导致最终在信号输出端输出的输出信号的占空比会偏离所述预设占空比。本发明在信号输入端与信号输出端之间设置上拉预放大单元12及下拉预放大单元14,并通过上拉预放大单元12及下拉预放大单元14调整正输入信号及负输入信号的占空比,使得信号输出端DQ占空比与输入信号的预设占空比相等,从而避免信号输入端与信号输出端的占空比发生变化。

本发明还提供一种存储器,其包括如上所述的输出驱动电路。所述存储器包括但不限于DRAM存储器。

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

- 输出驱动电路及存储器

- 温度控制输出驱动电路、驱动方法和存储器